# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Aug. 1996

# MSM82C51A-2RS/GS/JS

#### UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER

#### **GENERAL DESCRIPTION**

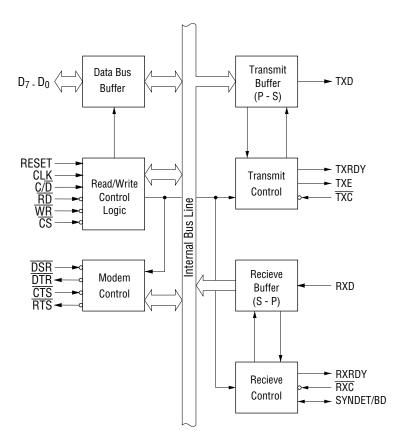

The MSM82C51A-2 is a USART (Universal Synchronous Asynchronous Receiver Transmitter) for serial data communication.

As a peripheral device of a microcomputer system, the MSM82C51A-2 receives parallel data from the CPU and transmits serial data after conversion. This device also receives serial data from the outside and transmits parallel data to the CPU after conversion.

The MSM82C51A-2 configures a fully static circuit using silicon gate CMOS technology. Therefore, it operates on extremely low power at 100  $\mu A$  (max) of standby current by suspending all operations.

#### **FEATURES**

- Wide power supply voltage range from 3 V to 6 V

- Wide temperature range from –40°C to 85°C

- Synchronous communication upto 64 Kbaud

- Asynchronous communication upto 38.4 Kbaud

- Transmitting/receiving operations under double buffered configuration.

- Error detection (parity, overrun and framing)

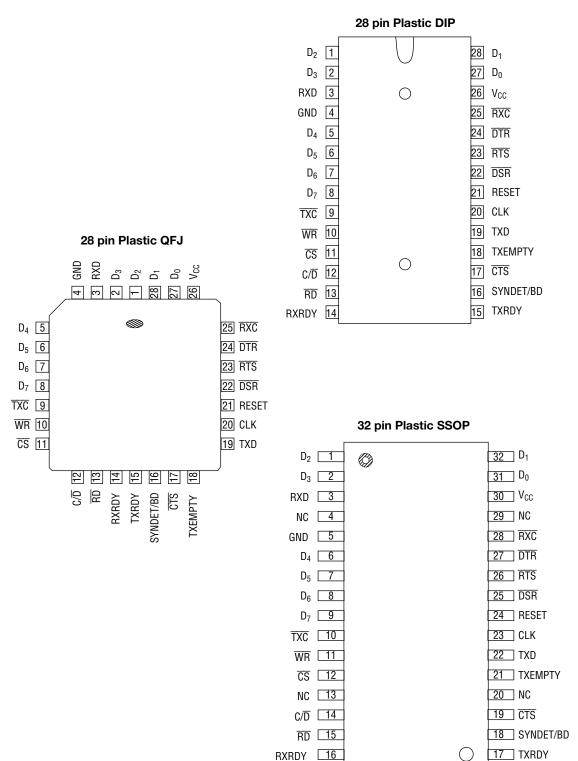

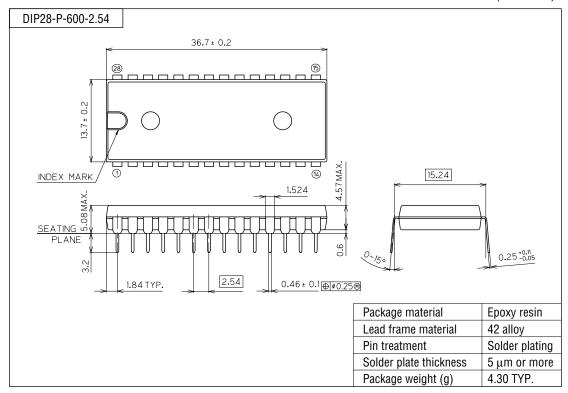

- 28-pin Plastic DIP (DIP28-P-600-2.54): (Product name: MSM82C51A-2RS)

- 28-pin Plastic QFJ (QFJ28-P-S450-1.27): (Product name: MSM82C51A-2JS)

- 32-pin Plastic SSOP(SSOP32-P-430-1.00-K): (Product name: MSM82C51A-2GS-K)

# **FUNCTIONAL BLOCK DIAGRAM**

# PIN CONFIGURATION (TOP VIEW)

# **FUNCTION**

#### **Outline**

The MSM82C51A-2's functional configuration is programed by software.

Operation between the MSM82C51A-2 and a CPU is executed by program control. Table 1 shows the operation between a CPU and the device.

| CS | C/D | RD | WR |                                |

|----|-----|----|----|--------------------------------|

| 1  | ×   | ×  | ×  | Data Bus 3-State               |

| 0  | ×   | 1  | 1  | Data Bus 3-State               |

| 0  | 1   | 0  | 1  | $Status \to CPU$               |

| 0  | 1   | 1  | 0  | $Control\ Word \leftarrow CPU$ |

| 0  | 0   | 0  | 1  | $Data \rightarrow CPU$         |

| 0  | 0 1 |    | 0  | Data ← CPU                     |

Table 1 Operation between MSM82C51A and CPU

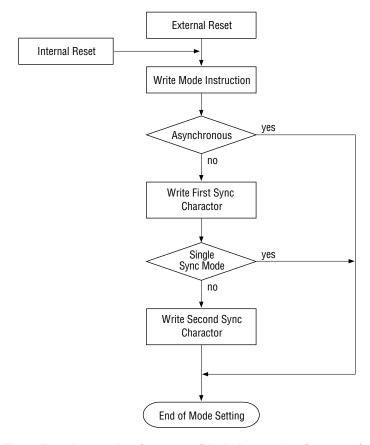

It is necessary to execute a function-setting sequence after resetting the MSM82C51A-2. Fig. 1 shows the function-setting sequence.

If the function was set, the device is ready to receive a command, thus enabling the transfer of data by setting a necessary command, reading a status and reading/writing data.

Fig. 1 Function-setting Sequence (Mode Instruction Sequence)

#### **Control Words**

There are two types of control word.

- 1. Mode instruction (setting of function)

- 2. Command (setting of operation)

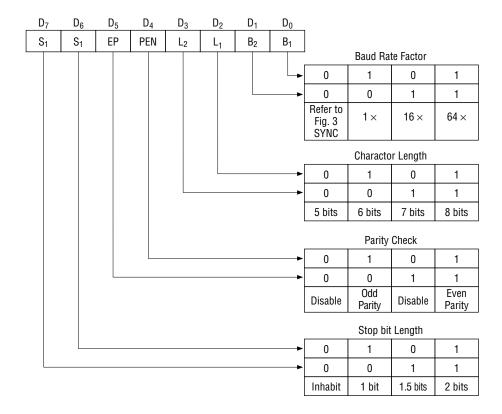

#### 1) Mode Instruction

Mode instruction is used for setting the function of the MSM82C51A-2. Mode instruction will be in "wait for write" at either internal reset or external reset. That is, the writing of a control word after resetting will be recognized as a "mode instruction." Items set by mode instruction are as follows:

- Synchronous/asynchronous mode

- Stop bit length (asynchronous mode)

- Character length

- Parity bit

- Baud rate factor (asynchronous mode)

- Internal/external synchronization (synchronous mode)

- Number of synchronous characters (Synchronous mode)

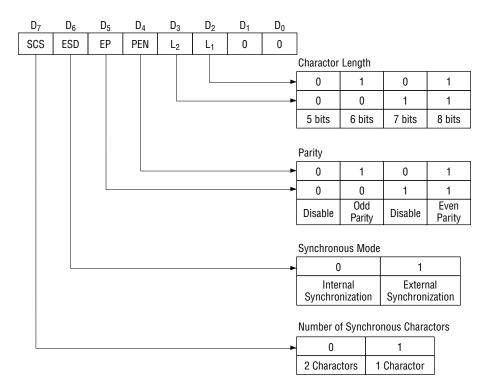

The bit configuration of mode instruction is shown in Figures 2 and 3. In the case of synchronous mode, it is necessary to write one-or two byte sync characters.

If sync characters were written, a function will be set because the writing of sync characters constitutes part of mode instruction.

Fig. 2 Bit Configuration of Mode Instruction (Asynchronous)

Fig. 3 Bit Configuration of Mode Instruction (Synchronous)

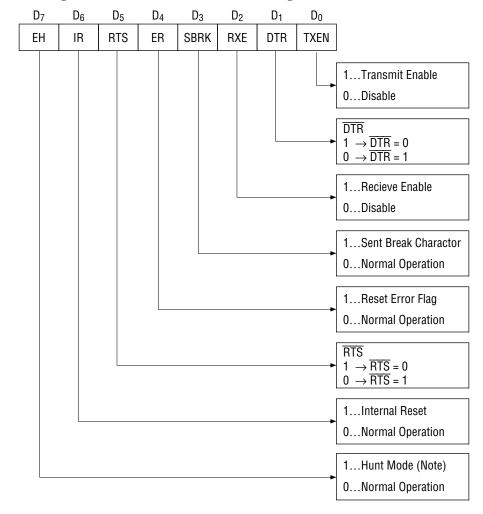

## 2) Command

Command is used for setting the operation of the MSM82C51A-2.

It is possible to write a command whenever necessary after writing a mode instruction and sync characters.

Items to be set by command are as follows:

- Transmit Enable/Disable

- Receive Enable/Disable

- DTR, RTS Output of data.

- Resetting of error flag.

- Sending to break characters

- Internal resetting

- Hunt mode (synchronous mode)

The bit configuration of a command is shown in Fig. 4.

**Note**: Seach mode for synchronous charactors in synchronous mode.

Fig. 4 Bit Configuration of Command

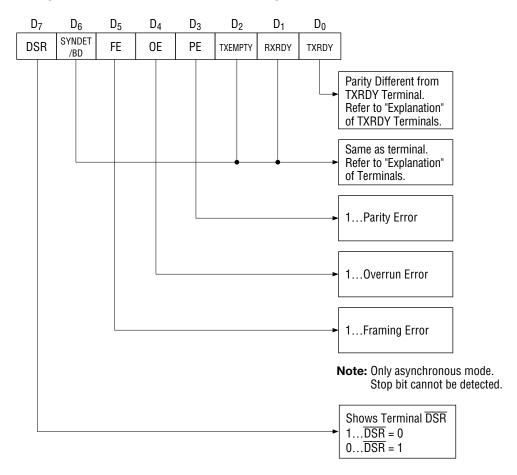

#### **Status Word**

It is possible to see the internal status of MSM82C51A-2 by reading a status word. The bit configuration of status word is shown in Fig. 5.

Fig. 5 Bit Configuration of Status Word

#### **Standby Status**

It is possible to put the MSM82C51A-2 in "standby status" When the following conditions have been satisfied the MSM82C51A-2 is in "standby status."

- (1)  $\overline{\text{CS}}$  terminal is fixed at Vcc level.

- (2) Input pins other  $\overline{CS}$ ,  $D_0$  to  $D_7$ ,  $\overline{RD}$ ,  $\overline{WR}$  and  $C/\overline{D}$  are fixed at Vcc or GND level (including SYNDET in external synchronous mode).

Note: When all output currents are 0, ICCS specification is applied.

# **Pin Description**

# $D_0$ to $D_7$ (I/O terminal)

This is bidirectional data bus which receive control words and transmits data from the CPU and sends status words and received data to CPU.

### **RESET (Input terminal)**

A "High" on this input forces the MSM82C51A-2 into "reset status."

The device waits for the writing of "mode instruction."

The min. reset width is six clock inputs during the operating status of CLK.

# **CLK** (Input terminal)

CLK signal is used to generate internal device timing.

CLK signal is independent of  $\overline{RXC}$  or  $\overline{TXC}$ .

However, the frequency of CLK must be greater than 30 times the  $\overline{RXC}$  and  $\overline{TXC}$  at Synchronous mode and Asynchronous "x1" mode, and must be greater than 5 times at Asynchronous "x16" and "x64" mode.

# WR (Input terminal)

This is the "active low" input terminal which receives a signal for writing transmit data and control words from the CPU into the MSM82C51A-2.

### **RD** (Input terminal)

This is the "active low" input terminal which receives a signal for reading receive data and status words from the MSM82C51A-2.

### C/D (Input terminal)

This is an input terminal which receives a signal for selecting data or command words and status words when the MSM82C51A-2 is accessed by the CPU.

If  $C/\overline{D} = low$ , data will be accessed.

If  $C/\overline{D}$  = high, command word or status word will be accessed.

#### **CS** (Input terminal)

This is the "active low" input terminal which selects the MSM82C51A-2 at low level when the CPU accesses.

Note: The device won't be in "standby status"; only setting  $\overline{CS}$  = High. Refer to "Explanation of Standby Status."

#### TXD (output terminal)

This is an output terminal for transmitting data from which serial-converted data is sent out. The device is in "mark status" (high level) after resetting or during a status when transmit is disabled. It is also possible to set the device in "break status" (low level) by a command.

#### **TXRDY** (output terminal)

This is an output terminal which indicates that the MSM82C51A-2 is ready to accept a transmitted data character. But the terminal is always at low level if  $\overline{\text{CTS}}$  = high or the device was set in "TX disable status" by a command.

Note: TXRDY status word indicates that transmit data character is receivable, regardless

of  $\overline{\text{CTS}}$  or command.

If the CPU writes a data character, TXRDY will be reset by the leading edge or  $\overline{\mbox{WR}}$  signal.

#### TXEMPTY (Output terminal)

This is an output terminal which indicates that the MSM82C51A-2 has transmitted all the characters and had no data character.

In "synchronous mode," the terminal is at high level, if transmit data characters are no longer remaining and sync characters are automatically transmitted. If the CPU writes a data character, TXEMPTY will be reset by the leading edge of  $\overline{\text{WR}}$  signal.

Note: As the transmitter is disabled by setting  $\overline{\text{CTS}}$  "High" or command, data written before disable will be sent out. Then TXD and TXEMPTY will be "High".

Even if a data is written after disable, that data is not sent out and TXE will be "High".After the transmitter is enabled, it sent out. (Refer to Timing Chart of Transmitter Control and Flag Timing)

#### TXC (Input terminal)

This is a clock input signal which determines the transfer speed of transmitted data.

In "synchronous mode," the baud rate will be the same as the frequency of  $\overline{TXC}$ .

In "asynchronous mode", it is possible to select the baud rate factor by mode instruction. It can be 1, 1/16 or 1/64 the  $\overline{TXC}$ .

The falling edge of  $\overline{TXC}$  sifts the serial data out of the MSM82C51A-2.

#### **RXD** (input terminal)

This is a terminal which receives serial data.

#### RXRDY (Output terminal)

This is a terminal which indicates that the MSM82C51A-2 contains a character that is ready to READ.

If the CPU reads a data character, RXRDY will be reset by the leading edge of  $\overline{RD}$  signal. Unless the CPU reads a data character before the next one is received completely, the preceding data will be lost. In such a case, an overrun error flag status word will be set.

#### RXC (Input terminal)

This is a clock input signal which determines the transfer speed of received data.

In "synchronous mode," the baud rate is the same as the frequency of  $\overline{\text{RXC}}$ .

In "asynchronous mode," it is possible to select the baud rate factor by mode instruction. It can be 1, 1/16, 1/64 the  $\overline{\text{RXC}}$ .

#### SYNDET/BD (Input or output terminal)

This is a terminal whose function changes according to mode.

In "internal synchronous mode." this terminal is at high level, if sync characters are received and synchronized. If a status word is read, the terminal will be reset.

In "external synchronous mode, "this is an input terminal.

A "High" on this input forces the MSM82C51A-2 to start receiving data characters.

In "asynchronous mode," this is an output terminal which generates "high level" output upon the detection of a "break" character if receiver data contains a "low-level" space between the stop bits of two continuous characters. The terminal will be reset, if RXD is at high level. After Reset is active, the terminal will be output at low level.

#### DSR (Input terminal)

This is an input port for MODEM interface. The input status of the terminal can be recognized by the CPU reading status words.

### DTR (Output terminal)

This is an output port for MODEM interface. It is possible to set the status of  $\overline{DTR}$  by a command.

## CTS (Input terminal)

This is an input terminal for MODEM interface which is used for controlling a transmit circuit. The terminal controls data transmission if the device is set in "TX Enable" status by a command. Data is transmitable if the terminal is at low level.

## RTS (Output terminal)

This is an output port for MODEM interface. It is possible to set the status  $\overline{\text{RTS}}$  by a command.

# **ABSOLUTE MAXIMUM RATING**

| Parameter            | Cymahal          |               | Rating                       |      |            |                        |  |  |  |  |  |  |

|----------------------|------------------|---------------|------------------------------|------|------------|------------------------|--|--|--|--|--|--|

| Parameter            | Symbol           | MSM82C51A-2RS | MSM82C51A-2JS                | Unit | Conditions |                        |  |  |  |  |  |  |

| Power Supply Voltage | V <sub>CC</sub>  |               | -0.5 to +7                   |      | ٧          | Mith was a sat         |  |  |  |  |  |  |

| Input Voltage        | V <sub>IN</sub>  |               | -0.5 to V <sub>CC</sub> +0.5 |      | ٧          | With respect<br>to GND |  |  |  |  |  |  |

| Output Voltage       | V <sub>OUT</sub> |               | -0.5 to V <sub>CC</sub> +0.5 |      | ٧          | to divid               |  |  |  |  |  |  |

| Storage Temperature  | T <sub>STG</sub> |               | °C                           | _    |            |                        |  |  |  |  |  |  |

| Power Dissipation    | P <sub>D</sub>   | 0.9 0.7 0.9 V |                              |      |            | Ta = 25°C              |  |  |  |  |  |  |

# **OPERATING RANGE**

| Parameter             | Symbol          | Range     | Unit |

|-----------------------|-----------------|-----------|------|

| Power Supply Voltage  | V <sub>CC</sub> | 3 - 6     | V    |

| Operating Temperature | T <sub>op</sub> | -40 to 85 | °C   |

# RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol          | Min. | Тур. | Max.                 | Unit |

|-----------------------|-----------------|------|------|----------------------|------|

| Power Supply Voltage  | V <sub>CC</sub> | 4.5  | 5    | 5.5                  | V    |

| Operating Temperature | T <sub>op</sub> | -40  | +25  | +85                  | °C   |

| "L" Input Voltage     | V <sub>IL</sub> | -0.3 | _    | +0.8                 | V    |

| "H" Input Voltage     | V <sub>IH</sub> | 2.2  | _    | V <sub>CC</sub> +0.3 | V    |

# **DC CHARACTERISTICS**

$(V_{CC} = 4.5 \text{ to } 5.5 \text{ V} \text{ Ta} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                   | Symbol           | Min. | Тур. | Max. | Unit | Measurement Conditions                                            |

|-----------------------------|------------------|------|------|------|------|-------------------------------------------------------------------|

| "L" Output Voltage          | V <sub>OL</sub>  | _    |      | 0.45 | V    | I <sub>OL</sub> = 2.5 mA                                          |

| "H" Output Voltage          | V <sub>OH</sub>  | 3.7  | _    | _    | V    | I <sub>OH</sub> = −2.5 mA                                         |

| Input Leak Current          | ILI              | -10  | _    | 10   | μΑ   | $0 \le V_{IN} \le V_{CC}$                                         |

| Output Leak Current         | I <sub>LO</sub>  | -10  | _    | 10   | μΑ   | 0 ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>                            |

| Operating Supply<br>Current | I <sub>CCO</sub> | _    | _    | 5    | mA   | Asynchronous X64 during Transmitting/<br>Receiving                |

| Standby Supply<br>Current   | I <sub>CCS</sub> | _    | _    | 100  | μА   | All Input voltage shall be fixed at V <sub>CC</sub> or GND level. |

# **AC CHARACTERISTICS**

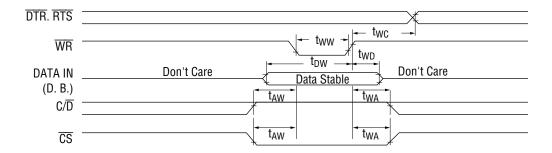

# **CPU Bus Interface Part**

$(V_{CC} = 4.5 \text{ to } 5.5 \text{ V}, Ta = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                | Symbol            | Min. | Max. | Unit            | Remarks |

|--------------------------|-------------------|------|------|-----------------|---------|

| Address Stable before RD | t <sub>AR</sub>   | 20   | _    | ns              | Note 2  |

| Address Hold Time for RD | t <sub>RA</sub>   | 20   | _    | ns              | Note 2  |

| RD Pulse Width           | t <sub>RR</sub>   | 130  | _    | ns              | _       |

| Data Delay from RD       | t <sub>RD</sub>   | _    | 100  | ns              | _       |

| RD to Data Float         | t <sub>DF</sub>   | 10   | 75   | ns              | _       |

| Recovery Time between RD | t <sub>RVR</sub>  | 6    | _    | t <sub>CY</sub> | Note 5  |

| Address Stable before WR | t <sub>AW</sub>   | 20   | _    | ns              | Note 2  |

| Address Hold Time for WR | t <sub>WA</sub>   | 20   | _    | ns              | Note 2  |

| WR Pulse Width           | tww               | 100  | _    | ns              | _       |

| Data Set-up Time for WR  | t <sub>DW</sub>   | 100  | _    | ns              | _       |

| Data Hold Time for WR    | t <sub>WD</sub>   | 0    | _    | ns              | _       |

| Recovery Time between WR | t <sub>RVW</sub>  | 6    | _    | t <sub>CY</sub> | Note 4  |

| RESET Pulse Width        | t <sub>RESW</sub> | 6    | _    | tcy             | _       |

#### **Serial Interface Part**

$(V_{CC} = 4.5 \text{ to } 5.5 \text{ V}, Ta = -40 \text{ to } 85^{\circ}\text{C})$

|                                        |                                |                                | (*(  | ,,,                 | 0.0 v, .u       | 10 10 00 0) |

|----------------------------------------|--------------------------------|--------------------------------|------|---------------------|-----------------|-------------|

| Parameter                              |                                | Symbol                         | Min. | Max.                | Unit            | Remarks     |

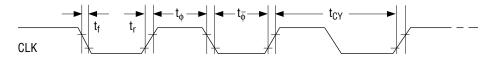

| Main Clock Period                      |                                | t <sub>CY</sub>                | 160  | _                   | ns              | Note 3      |

| Clock Low Tme                          |                                | $t_{\phi}^{-}$                 | 50   | _                   | ns              | _           |

| Clock High Time                        |                                | tφ                             | 70   | t <sub>CY</sub> -50 | ns              | _           |

| Clock Rise/Fall Time                   |                                | t <sub>r,</sub> t <sub>f</sub> | _    | 20                  | ns              | _           |

| TXD Delay from Falling Edge of         | TXC                            | t <sub>DTX</sub>               | _    | 1                   | μS              | _           |

|                                        | 1 × Baud                       | f <sub>TX</sub>                | DC   | 64                  | kHz             |             |

| Transmitter Clock Frequency            | 16 × Baud                      | f <sub>TX</sub>                | DC   | 615                 | kHz             | Note 3      |

|                                        | 64 × Baud                      | f <sub>TX</sub>                | DC   | 615                 | kHz             |             |

| Transmitter Olaski Lavy Times          | 1 × Baud                       | t <sub>TPW</sub>               | 13   | _                   | t <sub>CY</sub> | _           |

| Transmitter Clock Low Time             | $16 \times$ , $64 \times$ Baud | t <sub>TPW</sub>               | 2    | _                   | t <sub>CY</sub> | _           |

| Transmitter Clock High Time            | 1 × Baud                       | t <sub>TPD</sub>               | 15   | _                   | t <sub>CY</sub> | _           |

| Transmitter Glock riigh Time           | $16 \times$ , $64 \times$ Baud | t <sub>TPD</sub>               | 3    | _                   | t <sub>CY</sub> | _           |

|                                        | 1 × Baud                       | f <sub>RX</sub>                | DC   | 64                  | kHz             |             |

| Receiver Clock Frequency               | 16 × Baud                      | f <sub>RX</sub>                | DC   | 615                 | kHz             | Note 3      |

|                                        | 64 × Baud                      | f <sub>RX</sub>                | DC   | 615                 | kHz             |             |

| Deseiver Oleak Laur Times              | 1 × Baud                       | t <sub>RPW</sub>               | 13   | _                   | t <sub>CY</sub> | _           |

| Receiver Clock Low Time                | 16 ×, 64 × Baud                | t <sub>RPW</sub>               | 2    | _                   | t <sub>CY</sub> | _           |

| Desciver Cleak High Time               | 1 × Baud                       | t <sub>RPD</sub>               | 15   | _                   | t <sub>CY</sub> | _           |

| Receiver Clock High Time               | $16 \times$ , $64 \times$ Baud | t <sub>RPD</sub>               | 3    | _                   | t <sub>CY</sub> | _           |

| Time from the Center of Last Bi        | t to the Rise of               | t <sub>TXRDY</sub>             | _    | 8                   | t <sub>CY</sub> | _           |

| Time from the Leading Edge of of TXRDY | WR to the Fall                 | t <sub>TXRDY</sub> CLEAR       | _    | 400                 | ns              | _           |

| Time From the Center of Last B         | it to the Rise of RXRDY        | t <sub>RXRDY</sub>             | _    | 26                  | t <sub>CY</sub> | _           |

| Time from the Leading Edge of of RXRDY | RD to the Fall                 | t <sub>RXRDY</sub> CLEAR       | _    | 400                 | ns              | _           |

| Internal SYNDET Delay Time fro         | om Rising Edge of RXC          | t <sub>IS</sub>                | _    | 26                  | t <sub>CY</sub> | _           |

| SYNDET Setup Time for RXC              |                                | t <sub>ES</sub>                | 18   | _                   | t <sub>CY</sub> | _           |

| TXE Delay Time from the Cente          | r of Last Bit                  | t <sub>TXEMPTY</sub>           | 20   | _                   | t <sub>CY</sub> | _           |

| MODEM Control Signal Delay T of WR     | ime from Rising Edge           | t <sub>WC</sub>                | 8    | _                   | t <sub>CY</sub> | _           |

| MODEM Control Signal Setup T of RD     | ime for Falling Edge           | t <sub>CR</sub>                | 20   | _                   | t <sub>CY</sub> | _           |

| RXD Setup Time for Rising Edg          | e of RXC (1X Baud)             | t <sub>RXDS</sub>              | 11   | _                   | t <sub>CY</sub> | _           |

| RXD Hold Time for Falling Edge         | of RXC (1X Baud)               | t <sub>RXDH</sub>              | 17   | _                   | t <sub>CY</sub> | _           |

- Notes: 1. AC characteristics are measured at 150 pF capacity load as an output load based on 0.8 V at low level and 2.2 V at high level for output and 1.5 V for input.

- 2. Addresses are  $\overline{CS}$  and  $C/\overline{D}$ .

- 3.  $f_{TX}$  or  $f_{RX} \le 1/(30 \text{ Tcy})$  1× Baud  $f_{TX}$  or  $f_{RX} \le 1/(5 \text{ Tcy})$   $16 \times ,64 \times \text{ Baud}$

- 4. This recovery time is mode Initialization only. Recovery time between command writes for Asynchronous Mode is 8 t<sub>CY</sub> and for Synchronous Mode is 18 t<sub>CY</sub>. Write Data is allowed only when TXRDY = 1.

- 5. This recovery time is Status read only. Read Data is allowed only when RXRDY = 1.

- 6. Status update can have a maximum delay of 28 clock periods from event affecting the status.

# **TIMING CHART**

# **Sytem Clock Input**

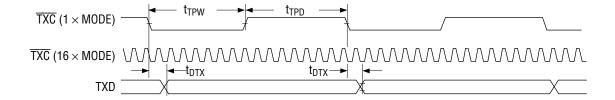

# **Transmitter Clock and Data**

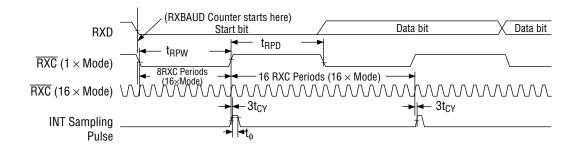

#### **Receiver Clock and Data**

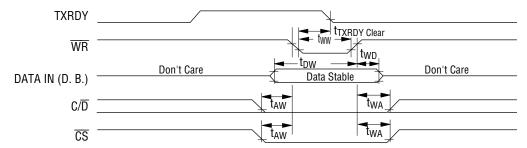

# Write Data Cycle (CPU → USART)

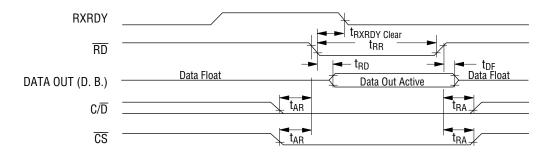

# Read Data Cycle (CPU ← USART)

# Write Control or Output Port Cycle (CPU → USART)

#### Read Control or Input Port Cycle (CPU ← USART)

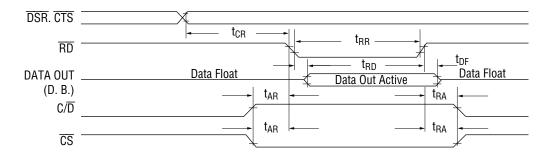

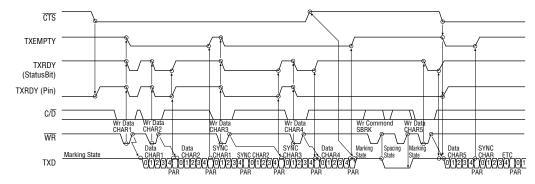

# Transmitter Control and Flag Timing (ASYNC Mode)

**Note:** The wave-form chart is based on the case of 7-bit data length + parity bit + 2 stop bit.

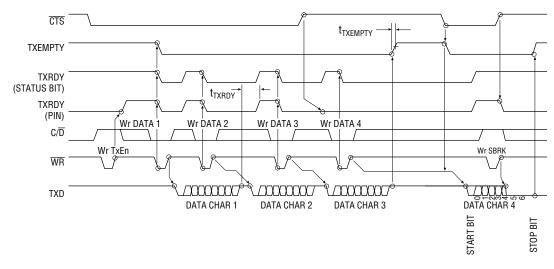

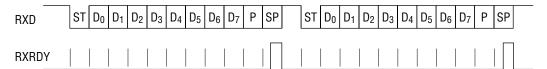

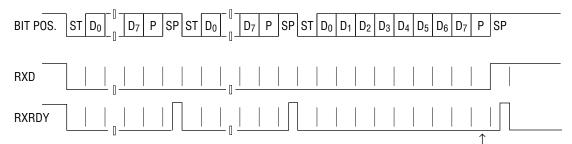

### Receiver Control and Flag Timing (ASYNC Mode)

**Note:** The wave-form chart is based on the case of 7 data bit length + parity bit + 2 stop bit.

# Transmitter Control and Flag Timing (SYNC Mode)

**Note:** The wave-form chart is based on the case of 5 data bit length + parity bit and 2 synchronous charactors.

Set SYNDET (Status bit)

#### (Note 2) SYNDET (Pin) (Note 1) SYNDET (SB) Data CHAR2 Lost ERROR (SB) RXRDY (PIN) Rd Status Wr EH<sub>0</sub> $C/\overline{D}$ Wr EH RxEn WR RD Don't 2are | CHAR 1 CHAR 2 | CHAR 1 | CHÀR 2 | CHAR 3 | CHÀR 3 | CHÀR 1 | CHÀR 2 | Don't Care | || CHÀR 1 | CHÀR 2 | CHAR 3 | CHÀR 3 | RXD ∠ CHAR ASSY CHAR ASSY Begins RXC And Begins Tolland

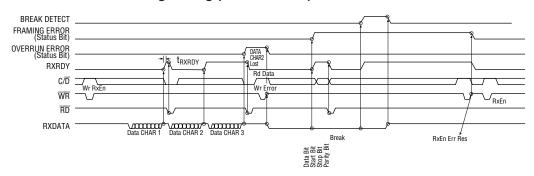

# Receiver Control and Flag Timing (SYNC Mode)

Note: 1. Internal Synchronization is based on the case of 5 data bit length + parity bit and 2 synchronous charactor.

Exit Hunt Mode

Set SYNDET (Status bit)

2. External Synchronization is based on the case of 5 data bit length + parity bit.

Exit Hunt Mode Set SYNDET

M

Note: 1. Half-bit processing for the start bit When the MSM82C51A-2 is used in the asynchronous mode, some problems are caused in the processing for the start bit whose length is smaller than the 1-data bit length. (See Fig. 1.)

| Start bit Length                      | Mode | Operation                                               |

|---------------------------------------|------|---------------------------------------------------------|

| Smaller than 7-Receiver Clock Length  | ×16  | The short start bit is ignored. (Normal)                |

| Smaller than 31-Receiver Clock Length | ×64  | The short start bit is ignored. (Normal)                |

| 8-Receiver Clock Length               | ×16  | Data cannot be received correctly due to a malfunction. |

| 32-Receiver Clock Length              | ×64  | Data cannot be received correctly due to a malfunction. |

| 9 to 16-Receiver Clock Length         | ×16  | The bit is regarded as a start bit. (normal)            |

| 33 to 64-Receiver Clock Length        | ×64  | The bit is regarded as a start bit. (normal)            |

2. Parity flag after a break signal is received (See Fig. 2.)

When the MSM82C51A-2 is used in the asynchrous mode, a parity flag may be set when the next normal data is read after a break signal is received.

A parity flag is set when the rising edge of the break signal (end of the break signal) is changed between the final data bit and the parity bit, through a RXRDY signal may not be outputted.

If this occurs, the parity flag is left set when the next normal dats is received, and the received data seems to be a parity error.

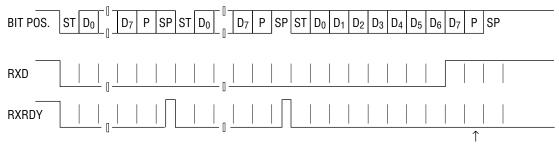

# Half-bit Processing Timing Chart for the Start bit (Fig. 1)

# **Normal Operation**

#### The Start bit Is Shorter Than a 1/2 Data bit

| RXD   |  | ST |  |  |  |  | S | T D | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | Р | SP |  |

|-------|--|----|--|--|--|--|---|-----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|----|--|

| RXRDY |  |    |  |  |  |  |   |     |                |                |                |                |                |                |                |   |    |  |

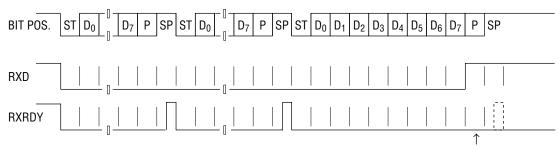

# The Start bit Is a 1/2 Data bit (A problem of MSM82C51A-2)

| RXD   | ST |  |  |  |  | ST | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | Р | SP |  |

|-------|----|--|--|--|--|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|----|--|

| RXRDY |    |  |  |  |  |    |                |                |                |                |                |                |                |                |   |    |  |

A RXRDY signal is outputted during data reception due to a malfunction.

# The Start bit Is Longer Than a 1/2 Data bit

| RXD   |  | Р Т |  |  |  |  | ST | $D_0$ | D <sub>1</sub> | $D_2$ | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D <sub>7</sub> | Р | SP |

|-------|--|-----|--|--|--|--|----|-------|----------------|-------|----------------|----------------|----------------|----------------|----------------|---|----|

| RXRDY |  |     |  |  |  |  |    |       |                |       |                |                |                |                |                |   |    |

ST: Start bit SP: Stop bit P: Parity bit D<sub>0</sub> - D<sub>7</sub>: Data bits

# **Break Signal Reception Timing and Parity Flag (Fig. 2)**

# **Normal Operation**

No parity flag is set. and no RXRDY signal is outputted.

# **Bug Timing**

A parity flag is set, but, no RXRDYsignal is outputted.

# **Normal Operation**

A parity flag is set. and a RXRDY signal is outputted.

# NOTICE ON REPLACING LOW-SPEED DEVICES WITH HIGH-SPEED DEVICES

The conventional low speed devices are replaced by high-speed devices as shown below. When you want to replace your low speed devices with high-speed devices, read the replacement notice given on the next pages.

| High-speed device (New) | Low-speed device (Old) | Remarks         |

|-------------------------|------------------------|-----------------|

| M80C85AH                | M80C85A/M80C85A-2      | 8bit MPU        |

| M80C86A-10              | M80C86A/M80C86A-2      | 16bit MPU       |

| M80C88A-10              | M80C88A/M80C88A-2      | 8bit MPU        |

| M82C84A-2               | M82C84A/M82C84A-5      | Clock generator |

| M81C55-5                | M81C55                 | RAM.I/O, timer  |

| M82C37B-5               | M82C37A/M82C37A-5      | DMA controller  |

| M82C51A-2               | M82C51A                | USART           |

| M82C53-2                | M82C53-5               | Timer           |

| M82C55A-2               | M82C55A-5              | PPI             |

#### Differences between MSM82C51A and MSM82C51A-2

#### 1) Manufacturing Process

These devices use a 3  $\mu$  Si-Gate CMOS process technology and have the same chip size.

#### 2) Function

These devices have the same logics except for changes in AC characteristics listed in (3-2).

#### 3) Electrical Characteristics

#### 3-1) DC Characteristics

| Parameter                  | Symbol | MSM82C51A | MSM82C51A-2 |

|----------------------------|--------|-----------|-------------|

| Vol measurement conditions | loL    | +2.0 mA   | +2.5 mA     |

| Von measurement conditions | Іон    | -400 μΑ   | -2.5 mA     |

Although the output voltage characteristics of these devices are identical, but the measurement conditions of the MSM82C51A-2 are more restricted than the MSM82C51A.

## 3-2) AC Characteristics

| Parameter                     | Symbol | MSM82C51A                           | MSM82C51A-2                        |

|-------------------------------|--------|-------------------------------------|------------------------------------|

| RD Pulse Width                | trr    | 250 ns minimum                      | 130 ns minimum                     |

| RD Rising to Data Difinition  | trd    | 200 ns maximum                      | 100 ns maximum                     |

| RD Rising to Data Float       | trf    | 100 ns maximum                      | 75 ns minimum                      |

| WR Pulse Width                | tww    | 250 ns minimum                      | 100 ns minimum                     |

| Data Setup Time for WR Rising | tow    | 150 ns minimum                      | 100 ns minimum                     |

| Data Hold Time for WR Rising  | two    | 20 ns minimum                       | 0 ns minimum                       |

| Master Clock Period           | tcy    | 250 ns minimum                      | 160 ns minimum                     |

| Clock Low Time                | tφ     | 90 ns minimum                       | 50 ns minimum                      |

| Clock High Time               | tφ     | 120 ns minimum<br>tcy-90 ns maximum | 70 ns minimum<br>tcy-50 ns maximum |

As shown above, the MSM82C51A-2 satisfies the characteristics of the MSM82C51A.

# **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

QFJ28-P-S450-1.27  $4.35 \pm 0.2$ 2.55 TYP. 18 □11.51± 0.08 012.45 ± 0.13 0.25 INDEX MARK Spherical surface (S) (M) 0.635 MIN. 1.27 0.81MAX. SEATING PLANE 0.41± 0.1 **₩**0.18**₩** Package material Epoxy resin 10.6 ± 0.25 Lead frame material Cu alloy Pin treatment Solder plating Solder plate thickness 5 µm or more

(Unit: mm)

1.00 TYP.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Package weight (g)

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

SS0P32-P-430-1.00-K 15.95 ± 0.1 12.0 ± 0.5 9.6 ± 0.2 7.9 ± 0.1 0.2 +0.1 2.05 ± 0.3 INDEX MARK Mirror finish 1.0 0.48 TYP. 2.5 MAX. 2.2 ± 0.2 0.35 ± 0.1 0.20 M **¾**0~10° 0.25 1.2 ± 0.2 1.3 TYP. SEATING PLANE Package material Epoxy resin Lead frame material 42 alloy Pin treatment Solder plating  $5\,\mu m$  or more Solder plate thickness

(Unit: mm)

0.60 TYP.

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Package weight (g)

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### 4) Notices on use

Note the following when replacing devices as the ASYNC pin is differently treated between the MSM82C84A and the MSM82C84A-5/MSM82C84A-2:

Case 1: When only a pullup resistor is externally connected to. The MSM82C84A can be replaced by the MSM82C84A-2.

Case 2: When only pulldown resistor is externally connected to.

When the pulldown resistor is 8 kiloohms or less, the MSM82C84A can be replaced by the MSM82C84A-2.

When the pulldown resistor is greater than 8 kiloohms, use a pulldown resistor of 8 kiloohms or less.

Case 3: When an output of the other IC device is connected to the device.

The MSM82C84A can be replaced by the MSM82C84A-2 when the  $I_{OL}$  pin of the device to drive the  $\overline{ASYNC}$  pin of the MSM82C84A-2 has an allowance of 100  $\mu A$  or more.

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.