# Z90231/233/234/239

# **Z8 DIGITAL TELEVISION CONTROLLERS**

### **FEATURES**

| Device | ROM<br>(KB) | RAM<br>(Bytes) | I/O<br>Lines¹ | Voltage<br>Range |

|--------|-------------|----------------|---------------|------------------|

| Z90231 | 32(OTP)     | 236            | 27            | 4.5V to 5.5V     |

| Z90233 | 16          | 236            | 27            | 4.5V to 5.5V     |

| Z90234 | 24          | 236            | 27            | 4.5V to 5.5V     |

| Z90239 | 32(ext.)    | 236            | 27            | 4.5V to 5.5V     |

Note: 1) It counts all muxed I/O port.

### Z8-Based CMOS Microcontroller for Consumer Television, Cable Box, and Satellite Receiver Applications

- 42-Pin SDIP Package except Z90239 (124 PGA)

- Z8<sup>®</sup> MCU Core at 6 MHz

- Mask ROM sizes Available in 16 and 24KB

- Ten 6-bit Pulse Width Modulators

- One 14-bit Pulse Width Modulator

- On-Chip Infrared (IR) Capture Registers

- Four Channel 4-bit Analog-to-Digital Converter

- Twenty Seven General Purpose I/O Pins

- I<sup>2</sup>C Master Serial Communication Port

## On Screen Display (OSD) Section

- Supports Displays up to 10 rows by 24 Columns with 256 Characters

- Character Cell Resolution of 14 Pixels by 18 Scan lines

- Variable Inter-row Spacing from 0–15 Horizontal Scan Lines

- Foreground and Background Colors Fully Programmable by Character

### **GENERAL DESCRIPTION**

The Z9023X Digital Television Controller (DTC) family is ZiLOG's latest and most powerful Z8-based DTC product offering. These parts feature larger system RAM and ROM options, together with a host of new features including a new color palette system, flexible inter-row spacing, higher character cell resolution, background mesh effect, dedicated I.R. capture registers, on-chip Analog-to-Digital conversion, and a hardware Master mode I<sup>2</sup>C interface. The familiar Z8 core in combination with these advanced features makes the Z9023X family an ideal choice for low to midrange televisions in both PAL and NTSC markets.

The Z9023X family consists of three basic device types; ICE Chip (Z90239), ROM Mask Parts (Z90233/Z90234), and OTP Part (Z90231). The OTP (Z90231) supports field programmable 32KB system ROM. ICE Chip (Z90239) is used in Z90239 Emulator and ProtoPak. As described above,

Z90233 supports 16KB system ROM and Z90234 supports 24KB system ROM for mask.

The Z9021X family takes full advantage of the Z8's expanded register file space to offer greater flexibility in On Screen Display creation.

**Note:** All signals with an overline, " $\overline{\phantom{a}}$ ", are active Low. For example,  $\overline{B/W}$  (WORD is active Low, only);  $\overline{B/W}$  (BYTE is active Low, only).

CP00300-TVX0698 1

### **GENERAL DESCRIPTION** (Continued)

Power connections follow conventional descriptions below:

| Connection | Circuit         | Device            |

|------------|-----------------|-------------------|

| Power      | V <sub>CC</sub> | $V_{DD}$          |

| Ground     | GND             | $V_{SS,} AV_{SS}$ |

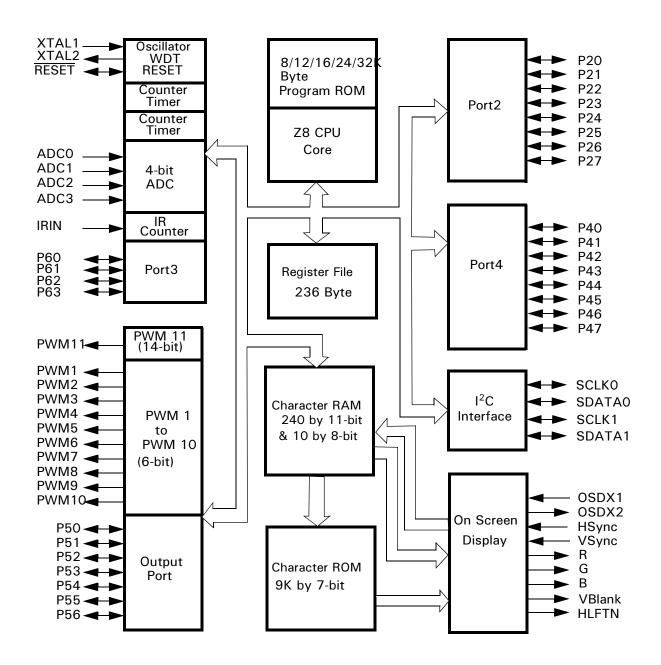

Figure 1. Functional Block Diagram

### PIN IDENTIFICATION

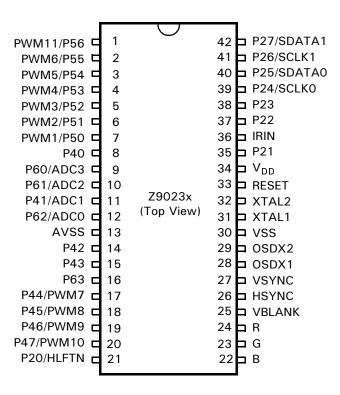

Figure 2. 42-Pin SIDP Pin Identification

# PIN IDENTIFICATION (Continued)

Table 1. Z90231/233/234 42-Pin SDIP Package

| Pin Number              | Pin Function                            | I/O/PWR | Reset State | Name                               | Note |

|-------------------------|-----------------------------------------|---------|-------------|------------------------------------|------|

| 34                      | +5 Volts                                | PWR     | PWR         | V <sub>DD</sub>                    |      |

| 30,13                   | 0 Volts                                 | PWR     | PWR         | V <sub>SS</sub> , AV <sub>SS</sub> |      |

| 36                      | Infra Red remote capture input          | ļ       | I           | IRIN                               |      |

| 1                       | 14-bit Pulse Width Modulator output     | 0       | I           | PWM11                              | 1    |

| 20,19,18,17,2,3,4,5,6,7 | 6-bit Pulse Width Modulator output      | 0       | I           | PWM[10:1]                          | 1    |

| 7,6,5,4,3,2,1           | Bit Programmable Input/Output ports     | I/O     | I           | P5[6:0]                            |      |

| 42,41,40,39,38,37,35,21 | Bit programmable Input/Output ports     | I/O     | I           | P2[7:0]                            |      |

| 21                      | Half tone output                        | 0       | I           | HLFTN                              |      |

| 40,42                   | I <sup>2</sup> C Data                   | I/O     | I           | SDATA0,1                           |      |

| 39,41                   | I <sup>2</sup> C Clock                  | I/O     | I           | SCLK0,1                            |      |

| 16,12,10,9              | Bit programmable Input/Output ports     | I/O     | I           | P6[3:0]                            |      |

| 20,19,18,17,15,14,11,8  | Bit programmable Input/Output ports     | I/O     | I           | P4[7:0]                            |      |

| 31                      | Crystal oscillator input                | I       | 1           | XTAL1                              |      |

| 32                      | Crystal oscillator output               | 0       | 0           | XTAL2                              |      |

| 28                      | Dot clock oscillator input              | I       | I           | OSDX1                              |      |

| 29                      | Dot clock oscillator output             | 0       | 0           | OSDX2                              |      |

| 26                      | Horizontal Sync                         | l       | I           | HSYNC                              |      |

| 27                      | Vertical Sync                           | l       | I           | VSYNC                              |      |

| 25                      | Video blank                             | 0       | 0           | VBLANK                             |      |

| 24,23,22                | Video R,G,B                             | 0       | 0           | R,G,B                              |      |

| 9,10,11,12              | 4-bit Analog to Digital converter input | Al      | I           | ADC[3:0]                           |      |

| 33                      | Device reset                            | I       | I           | /RESET                             |      |

#### Note:

<sup>1.</sup> It is Input on POR. It must be configured to be output ports for PWM applications

### **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This rating is a stress rating only. Operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

| Symbol           | Parameters            | Min  | Max                  | Units | Notes      |

|------------------|-----------------------|------|----------------------|-------|------------|

| V <sub>DD</sub>  | Power Supply Voltage  | -0.3 | +7                   | V     |            |

| V <sub>I</sub>   | Input Voltage         | -0.3 | V <sub>DD</sub> +0.3 | V     |            |

| Vo               | Output Voltage        | -0.3 | V <sub>DD</sub> +0.3 | V     |            |

| I <sub>OH</sub>  | Output Current High   |      | -10                  | mA    | per pin    |

| I <sub>OH</sub>  | Output Current High   |      | -100                 | mA    | per device |

| I <sub>OL</sub>  | Output Current Low    |      | 20                   | mA    | per pin    |

| I <sub>OL</sub>  | Output Current Low    |      | 200                  | mA    | per device |

| T <sub>A</sub>   | Operating Temperature | 0    | 70                   | °С    |            |

| T <sub>STG</sub> | Storage Temperature   | -55  | 150                  | °C    |            |

### STANDARD TEST CONDITIONS

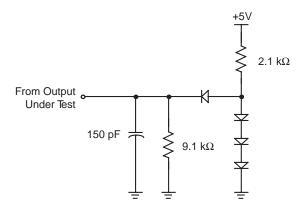

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin (Figure 3).

Figure 3. Test Load Diagram

### **DC CHARACTERISTICS**

$T_A = 0^{\circ}C \text{ to } + 70^{\circ}C; V_{DD} = +4.5V \text{ to } +5.5V; F_{OSC} = 6 \text{ MHz}$

| Symbol             | Parameter              | Min                  | Typical | Max                  | Units | Conditions                                 |

|--------------------|------------------------|----------------------|---------|----------------------|-------|--------------------------------------------|

| $V_{DD}$           | Power Supply Voltage   | 4.5                  | 5.00    | 5.5                  | V     |                                            |

| V <sub>IH</sub>    | Input Voltage High     | 0.7V <sub>DD</sub>   |         | $V_{DD}$             | V     |                                            |

| V <sub>IL</sub>    | Input Voltage Low      | 0                    |         | 0.2V <sub>DD</sub>   | V     |                                            |

| V <sub>IHC</sub>   | Input XTAL/Osc in High | 0.7V <sub>DD</sub>   |         | V <sub>CC</sub>      | V     |                                            |

| V <sub>ILC</sub>   | Input XTAL/Osc In Low  | 0                    |         | 0.07V <sub>DD</sub>  | V     |                                            |

| V <sub>OH_ST</sub> | Output Voltage High    | V <sub>DD</sub> -0.4 | 4.75    |                      | V     | I <sub>OH</sub> =–2mA for standard drive   |

| V <sub>OL_ST</sub> | Output Voltage Low     |                      | 0.16    | 0.4                  | V     | I <sub>OL</sub> =2.00mA for standard drive |

| V <sub>OH_LE</sub> | Output Voltage High    |                      |         | V <sub>DD</sub> -0.4 | V     | I <sub>OH</sub> =-0.98mA for low EMI drive |

| V <sub>OL_LE</sub> | Output Voltage Low     | 0.4                  |         |                      | V     | I <sub>OL</sub> =0.66mA for low EMI drive  |

| $V_{HY}$           | Schmitt Hysteresis     | 0.1V <sub>DD</sub>   | 8.0     |                      | V     |                                            |

| I <sub>IR</sub>    | Reset Input Current    |                      | -46     | -80                  | uA    | V <sub>RL</sub> =0V                        |

| I <sub>IL</sub>    | Input Leakage          | -3.0                 | 0.01    | 3.0                  | uA    | 0V,V <sub>DD</sub>                         |

| I <sub>OL</sub>    | Tri-State Leakage      | -3.0                 | 0.02    | 3.0                  | uA    | 0V,V <sub>DD</sub>                         |

| I <sub>CC</sub>    | Supply Current         |                      | 25      | 40                   | mA    | All inputs at rail;outputs floating        |

| I <sub>CC1</sub>   | HALT Mode Current      |                      | 3.2     | 6                    | mA    | All inputs at rail;outputs floating        |

| I <sub>CC2</sub>   | STOP Mode Current      |                      | 0.1     | 10                   | uA    | All inputs at rail;outputs floating        |

Note: Typical values measured at 25°C. Minimum and Maximum values indicated from 0°C to 70°C.

# **AC CHARACTERISTICS**

| No | Symbol                             | Parameter                                         | Min               | Max               | Unit |

|----|------------------------------------|---------------------------------------------------|-------------------|-------------------|------|

| 1  | T <sub>p</sub> C                   | Input clock period                                | 166               | 1000              | ns   |

| 2  | T <sub>r</sub> C, T <sub>f</sub> C | Clock input raise and fall                        |                   | 25                | ns   |

| 3  | T <sub>w</sub> C                   | Input clock width                                 | 35                |                   | ns   |

| 4  | $T_wH_{SYNC}L$                     | Timer input low width                             | 70                |                   | ns   |

| 5  | $T_wH_{SYNC}H$                     | Timer input high width                            | 3Т <sub>р</sub> С |                   |      |

| 6  | $T_pH_{SYNC}$                      | Timer input period                                | 8T <sub>p</sub> C |                   |      |

| 7  | $T_rH_{SYNC}$ , $T_rH_{SYNC}$      | Timer input raise and fall                        |                   | 100               | ns   |

| 8  | T <sub>w</sub> IL                  | Int request input low                             | 70                |                   | ns   |

| 9  | T <sub>w</sub> IH                  | Int request input high                            | 3Т <sub>р</sub> С |                   |      |

| 10 | T <sub>d</sub> POR                 | Power-On reset delay                              | 25                | 100               | ms   |

| 11 | T <sub>d</sub> LVIRES              | Low voltage detect to internal RESET condition    | 200               |                   | ns   |

| 12 | T <sub>w</sub> RES                 | Reset minimum width                               | 5T <sub>p</sub> C |                   |      |

| 13 | $T_dH_sOI$                         | H <sub>sync</sub> start to V <sub>osc</sub> stop  | 2T <sub>p</sub> V | 3T <sub>p</sub> V |      |

| 14 | T <sub>d</sub> H <sub>s</sub> Oh   | H <sub>sync</sub> start to V <sub>osc</sub> start |                   | 1T <sub>p</sub> V |      |

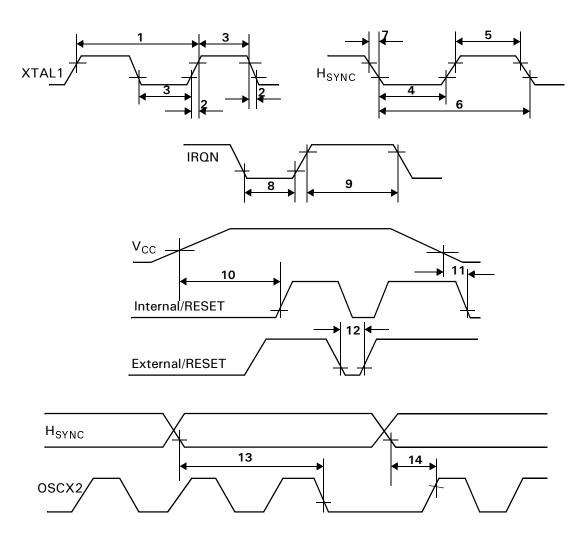

# **AC TIMING DIAGRAMS**

Figure 4. Timing Diagram

#### **Pre-Characterization Product:**

The product represented by this CPS is newly introduced and ZiLOG has not completed the full characterization of the product. The CPS states what ZiLOG knows about this product at this time, but additional features or non-conformance with

some aspects of the CPS may be found, either by ZiLOG or its customers in the course of further application and characterization work. In addition, ZiLOG cautions that delivery may be uncertain at times, due to start-up yield issues.

© 1998 by ZiLOG, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of ZiLOG, Inc. The information in this document is subject to change without notice. Devices sold by ZiLOG, Inc. are covered by warranty and patent indemnification provisions appearing in ZiLOG, Inc. Terms and Conditions of Sale only.

ZILOG, INC. MAKES NO WARRANTY, EXPRESS, STATUTORY, IMPLIED OR BY DESCRIPTION, REGARDING THE INFORMATION SET FORTH HEREIN OR REGARDING THE FREEDOM OF THE DESCRIBED DEVICES FROM INTELLECTUAL PROPERTY INFRINGEMENT. ZILOG, INC. MAKES NO WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE.

ZiLOG, Inc. shall not be responsible for any errors that may appear in this document. ZiLOG, Inc. makes no commitment to

update or keep current the information contained in this document.

ZiLOG's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and ZiLOG prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

ZiLOG, Inc.

910 East Hamilton Avenue, Suite 110

Campbell, CA 95008

Telephone (408) 558-8500

FAX 408 558-8300

Internet: http://www.zilog.com