## PCI-SCI Bridge Chips for System Area Networks

## Features and Benefits

- PCI 2.1 compliant, 64 bits, 33 MHz PCI bus

- ANSI/IEEE 1596-1992 Scalable Coherent Interface (SCI) standard compliant

- ANSI/IEEE 1159.1 (JTAG) support

- Compatible with Dolphin Link Controllers

- Chaining (Read/Write) DMA Engine

- Up to 4096 map entries in offchip SRAM

- 4 512 KBytes page size

- Hostbridge capability (PCI arbiter, Event reporter)

- Read prefetching/write gathering

- B-Link™ Compliant

Dolphin's PCI-SCI Bridge (PSB) Chip provides a reliable, very high bandwidth and low-latency connection between PCI buses, making it ideally suited for server clustering and high performance system area network applications.

The PSB-64 chip is designed to meet the requirements for high availability clustering and remote I/O applications. In a unique architecture combining both direct memory access (DMA) and remote memory access (RMA), high performance message passing protocols and transparent bus bridging operations are supported. The PSB chip is based on the ANSI/IEEE Scalable Coherent Interface (SCI) standard.

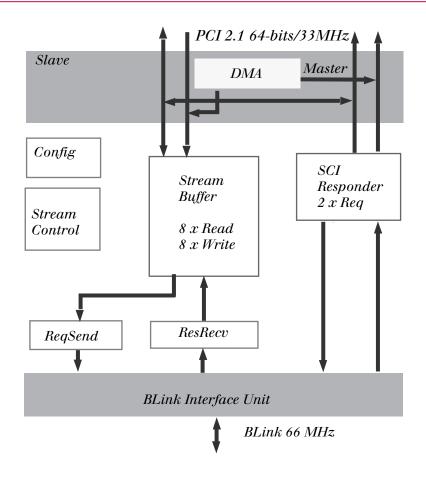

By use of the DMA controller chunks of memory can be copied directly between PCI buses in a single copy operation with no need for intermediate buffering in adapter cards or buffer memories. This feature greatly reduces latency and lowers overhead of data transfers. The DMA controller supports both read and write operations.

The remote memory access (RMA) feature of the PSB enables ultra-low latency messaging and low overhead and transparent I/O transfers. In RMA mode, PCI bus memory transactions are converted into corresponding SCI bus memory transactions allowing two physically separate PCI buses to appear as one. This feature allows applications to send data between system memories without the use of operating system services, thus greatly reducing latency and overhead.

The PSB has built-in address translation, error detection and protection mechanisms to support highly reliable connections.

## Block Diagram

## **Technical Specifications**

PCI Specification

PCI Specification 2.1

64 bits, 33 MHz operation 3.3V/5V PCI bus operation

**B-Link Specification**

64 bits, 50 MHz operation 500 Mbytes/sec bandwidth

SCI Specification

ANSI/IEEE 1596-1992 Scalable Coherent

Interface (SCI) compliant

Dolphin Headquarters USA:

3609 East Thousand Oaks Blvd, Suite 209 Westlake Village, CA 91362-3624

(805) 371-9493

(805) 371-9785

Packaging and Power

313 Ball Grid Array

3 Watts

3.3V or 5V I/O

**Operating Temperature**

Operating Temperature: 4°C-32°C

Relative Humidity: 5%-95% non-condensing

Performance

33 MHz

140 MBytes/sec RMA 107 MBytes/sec DMA

**Product Code**

PSB-64 (D667)

Dolphin Interconnect Solutions Offices:

Dolphin USA:

111 Speen Street Framingham, MA 01701-2090

(508) 875-3030 Fax:

(508) 875-1517

Dolphin Europe:

Olaf Helsets vei 6 0621 Oslo, Norway

Phone:

+ 47 23 16 70 00

Fax:

+ 47 23 16 71 80

Internet Information:

E-mail: info@dolphinics.com World Wide Web: http://www.dolphinics.com

© 1999 by Dolphin Interconnect Solutions, Inc. All rights reserved. Specifications subject to change without notice. *LinkController* is a trademark of Dolphin Interconnect Solutions. All other brand or product names are trademarks or registered trademarks of their respective holders