# 3946

# Half-Bridge Power MOSFET Controller

| V              |

|----------------|

|                |

| $\mathbf{V}^1$ |

| $V^2$          |

| $\mathbf{V}^1$ |

| $V^2$          |

|                |

Operating Temperature Range,  $T_A$ ...-40°C to +135°C Junction Temperature,  $T_J$ .....+150°C Storage Temperature Range,  $T_S$ ....-55°C to +150°C Notes:

1. Measured on a two-sided PCB with 3 in.<sup>2</sup> of 2 oz. copper.

2. Measured on JEDEC standard High-K board.

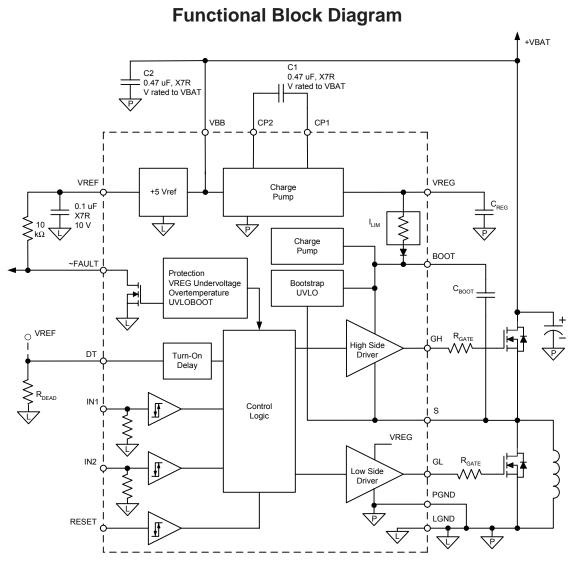

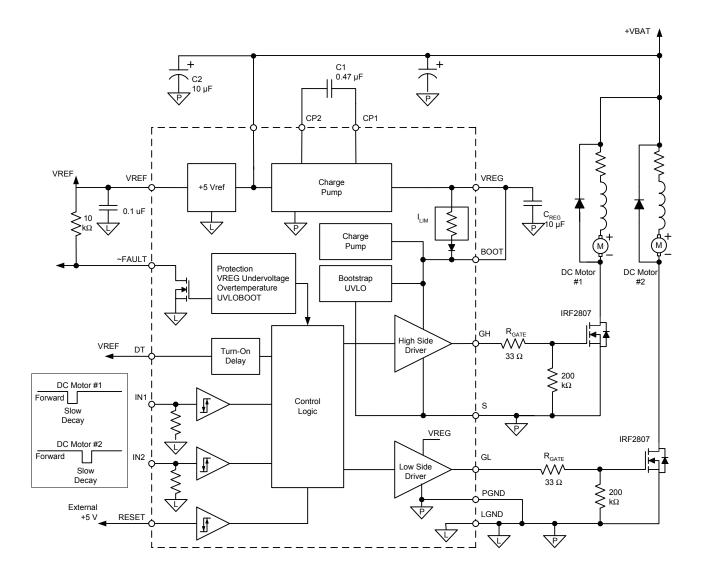

The A3946 is designed specifically for applications that require high power unidirectional dc motors, three-phase brushless dc motors, or other inductive loads. The A3946 provides two high-current gate drive outputs that are capable of driving a wide range of power N-channel MOSFETs. The high-side gate driver switches an N-channel MOSFET that controls current to the load, while the low-side gate driver switches an N-channel MOSFET as a synchronous rectifier.

A bootstrap capacitor provides the above-battery supply voltage required for N-channel MOSFETs. An internal charge pump for the high side allows for dc (100% duty cycle) operation of the half-bridge.

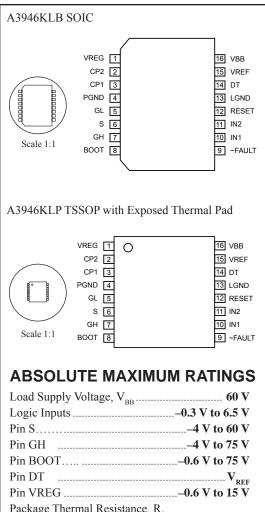

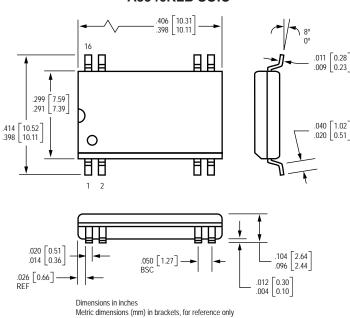

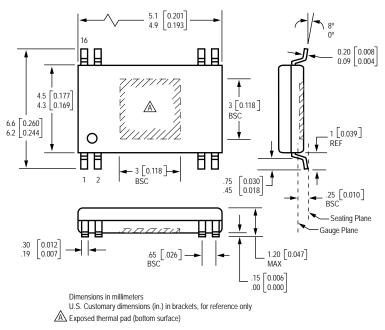

The A3946 is available in a choice of two power packages: a 16-lead SOIC with internally fused leads (part number suffix *LB*), and a 16-lead TSSOP with exposed thermal pad (suffix *LP*). Both packages have a lead (Pb) free version, with 100% matte tin plated leadframes (suffix *-T*).

#### **FEATURES**

- On-chip charge pump for 7 V minimum input supply voltage

- High-current gate drive for driving a wide range of N-channel MOSFETs

- Bootstrapped gate drive with charge pump for 100% duty cycle

- Overtemperature protection

- Undervoltage protection

- -40°C to 135°C ambient operation

#### Selection Guide

| Part Number  | Pb-free | Packing          | Package                                   |  |  |                             |

|--------------|---------|------------------|-------------------------------------------|--|--|-----------------------------|

| A3946KLB     | -       | 47 pieces/tube   |                                           |  |  |                             |

| A3946KLB-T   | Yes     |                  | 47 pieces/tube<br>16-pin SOIC with interr |  |  | 16-pin SOIC with internally |

| A3946KLBTR   | -       | 1000 pieces/reel | fused leads                               |  |  |                             |

| A3946KLBTR-T | Yes     | 1000 pieces/reei |                                           |  |  |                             |

| A3946KLP     | -       | 96 pieces/tube   |                                           |  |  |                             |

| A3946KLP-T   | Yes     |                  | 16-pin TSSOP with exposed                 |  |  |                             |

| A3946KLPTR   | _       | 4000 piagos/rool | thermal pad                               |  |  |                             |

| A3946KLPTR-T | Yes     | 4000 pieces/reel |                                           |  |  |                             |

#### **Control Logic Table**

| IN1 | IN2 | DT Pin                   | RESET | GH | GL | Function                                |

|-----|-----|--------------------------|-------|----|----|-----------------------------------------|

| Х   | Х   | X                        | 0     | Z  | Z  | Sleep mode                              |

| 0   | 0   | R <sub>DEAD</sub> - LGND | 1     | L  | Н  | Low-side FET ON following dead time     |

| 0   | 1   | R <sub>DEAD</sub> - LGND | 1     | L  | L  | All OFF                                 |

| 1   | 0   | R <sub>DEAD</sub> - LGND | 1     | L  | L  | All OFF                                 |

| 1   | 1   | R <sub>DEAD</sub> - LGND | 1     | Н  | L  | High-side FET ON following dead time    |

| 0   | 0   | VREF                     | 1     | L  | L  | All OFF                                 |

| 0   | 1   | VREF                     | 1     | L  | Н  | Low-side FET ON                         |

| 1   | 0   | VREF                     | 1     | Н  | L  | High-side FET ON                        |

| 1   | 1   | VREF                     | 1     | Н  | Н  | CAUTION: High-side and low-side FETs ON |

#### **ELECTRICAL CHARACTERISTICS** at $T_A = -40$ to +135°C, $V_{BB} = 7$ to 60 V (unless otherwise noted)

| Characteristics                   | Symbol              | Test Conditions                                            | Limits                 |      |      |       |  |

|-----------------------------------|---------------------|------------------------------------------------------------|------------------------|------|------|-------|--|

| Characteristics                   | Symbol              | Test Conditions                                            | Min.                   | Тур. | Max. | Units |  |

| V. Ouisseet Current               |                     | RESET = High, Outputs Low                                  | -                      | 3    | 6    | mA    |  |

| V <sub>BB</sub> Quiescent Current | I <sub>VBB</sub>    | RESET = Low                                                | -                      | _    | 10   | μA    |  |

|                                   | N                   | $V_{_{BB}}$ > 7.75 V, $I_{_{reg}}$ = 0 mA to 15 mA         | 12.0                   | 13   | 13.5 | V     |  |

| VREG Output Voltage               | $V_{REG}$           | $V_{_{BB}}$ = 7 V to 7.75 V, I $_{_{reg}}$ = 0 mA to 15 mA | 11.0                   | —    | 13.5 | V     |  |

| Charge Pump Frequency             | F <sub>CP</sub>     | CP1, CP2                                                   | -                      | 62.5 | _    | kHz   |  |

| VREF Output Voltage               | V <sub>REF</sub>    | I <sub>REF</sub> ≤ 4 mA, C <sub>REF</sub> = 0.1 μF         | 4.5                    | _    | 5.5  | V     |  |

| Gate Output Drive                 |                     |                                                            |                        |      |      |       |  |

| Turn On Time                      | t <sub>rise</sub>   | C <sub>LOAD</sub> = 3300 pF, 20% to 80%                    | -                      | 60   | 100  | ns    |  |

| Turn Off Time                     | t <sub>fall</sub>   | C <sub>LOAD</sub> = 3300 pF, 80% to 20%                    | _                      | 40   | 80   | ns    |  |

| Dullur On Desistance              | R <sub>DSUP</sub>   | $T_j = 25^{\circ}C$                                        | _                      | 4    | _    | Ω     |  |

| Pullup On Resistance              |                     | T <sub>j</sub> = 135°C                                     | _                      | 6    | _    | Ω     |  |

|                                   | R <sub>dsdown</sub> | T <sub>j</sub> = 25°C                                      | _                      | 2    | _    | Ω     |  |

| Pulldown On Resistance            |                     | T <sub>j</sub> = 135°C                                     | _                      | 3    | _    | Ω     |  |

| Short Circuit Current –<br>Source | _                   | t <sub>pw</sub> < 10 μs                                    | 800                    | _    | _    | mA    |  |

| Short Circuit Current –<br>Sink   | _                   | t <sub>pw</sub> < 10 μs                                    | 1000                   | _    | _    | mA    |  |

| GH Output Voltage                 | V <sub>GH</sub>     | $t_{pw}$ < 10 µs, Bootstrap Capacitor fully charged        | V <sub>REG</sub> – 1.5 | _    | _    | V     |  |

| GL Output Voltage                 | V <sub>GL</sub>     | _                                                          | V <sub>REG</sub> -0.2  | _    | _    | V     |  |

| Timing                            |                     |                                                            |                        |      |      |       |  |

| Dead Time (Delay from             | +                   | $R_{dead} = 5 \text{ k}\Omega$                             | 200                    | 350  | 500  | ns    |  |

| Turn Off to Turn On)              | t <sub>DEAD</sub>   | R <sub>dead</sub> = 100 kΩ                                 | 5                      | 6    | 7    | μs    |  |

| Propagation Delay                 | t <sub>PD</sub>     | Logic input to unloaded GH, GL. DT = VREF                  | _                      | _    | 150  | ns    |  |

#### **ELECTRICAL CHARACTERISTICS** at $T_A = -40$ to +135°C, $V_{BB} = 7$ to 60 V (unless otherwise noted)

|                              |                     |                                                   | Limits |      |      |       |

|------------------------------|---------------------|---------------------------------------------------|--------|------|------|-------|

| Characteristics              | Symbol              | Test Conditions                                   | Min.   | Тур. | Max. | Units |

| Protection                   |                     |                                                   | !      | 1    | 1    | 1     |

| VREG Undervoltage            | V <sub>REGON</sub>  | V <sub>REG</sub> increasing                       | 8.6    | 9.1  | 9.6  | V     |

| VREG Undervoltage            | V <sub>REGOFF</sub> | V <sub>REG</sub> decreasing                       | 7.8    | 8.3  | 8.8  | V     |

| BOOT Undervoltage            | V <sub>BSON</sub>   | V <sub>BOOT</sub> increasing                      | 8      | 8.75 | 9.5  | V     |

| BOOT Undervoltage            | V                   | V <sub>BOOT</sub> decreasing                      | 7.25   | 8.0  | 8.75 | V     |

| Thermal Shutdown Temperature | T <sub>JTSD</sub>   | Temperature increasing                            | _      | 170  | _    | °C    |

| Thermal Shutdown Hysteresis  | $\Delta T_{J}$      | Recovery = $T_{JTSD} - \Delta T_{J}$              | _      | 15   | _    | °C    |

| Logic                        | L.                  |                                                   |        |      |      |       |

| Input Current                | I <sub>IN(1)</sub>  | IN1 V <sub>IN</sub> / IN2 V <sub>IN</sub> = 2.0 V | -      | 40   | 100  | μA    |

|                              | I <sub>IN(0)</sub>  | IN1 V <sub>IN</sub> / IN2 V <sub>IN</sub> = 0.8 V | _      | 16   | 40   | μA    |

|                              |                     | RESET pin only                                    | _      | -    | 1    | μA    |

| Logic Input Voltage          | V <sub>IN(1)</sub>  | IN1 / IN2 logic high                              | 2.0    | -    | _    | V     |

|                              |                     | RESET logic high                                  | 2.2    | _    | _    | V     |

|                              | V <sub>IN(0)</sub>  | Logic low                                         | _      | _    | 0.8  | V     |

| Logic Input Hysteresis       | _                   | All digital inputs                                | 100    | _    | 300  | mV    |

| Foult Output                 | V <sub>ol</sub>     | I = 1 mA, fault asserted                          | _      | -    | 400  | mV    |

| Fault Output                 | V <sub>oh</sub>     | V = 5 V                                           | _      | _    | 1    | μA    |

#### **Functional Description**

**VREG.** A 13 V output from the on-chip charge pump, used to power the low-side gate drive circuit directly, provides the current to charge the bootstrap capacitors for the high-side gate drive.

The VREG capacitor,  $C_{REG}$ , must supply the instantaneous current to the gate of the low-side MOSFET. A 10  $\mu$ F, 25 V capacitor should be adequate. This capacitor can be either electrolytic or ceramic (X7R).

**Diagnostics and Protection**. The fault output pin, ~FAULT, goes low (i.e., FAULT = 1) when the RESET line is high and any of the following conditions are present:

- Undervoltage conditions on VREG (UVREG) or on the internal logic supply VREF (UVREF). These conditions set a latched fault.

- A junction temperature > 170°C (OVERTEMP). This condition sets a latched fault.

- An undervoltage on the stored charge of the BOOT capacitor (UVBOOT). This condition does NOT set a latched fault.

An overtemperature event signals a latched fault, but does not disable any output drivers, regulators, or logic inputs. The user must turn off the A3946 (e.g., force the RESET line low) to prevent damage.

The power FETs are protected from inadequate gate drive voltage by undervoltage detectors. Either of the regulator undervoltage faults (UVREG or UVREF) disable both output drivers until both voltages have been restored. The high-side driver is also disabled during a UVBOOT fault condition.

Under many operating conditions, both the high-side (GH) and low-side (GL) drivers may be off, allowing the BOOT capacitor to discharge (or never become charged) and create a UVBOOT fault condition, which in turn inhibits the high-side driver and creates a FAULT = 1. This fault is NOT latched. To remove this fault, momentarily turn on GL to charge the BOOT capacitor.

Latched faults may be cleared by a low pulse, 1 to  $10 \ \mu s$  wide, on the RESET line. Throughout that pulse (despite a possible UVBOOT), FAULT = 0; also the fault latch is

cleared immediately, and remains cleared. If the power is restored (no UVREG or UVREF), and if no OVERTEMP fault exists, then the latched fault remains cleared when the RESET line returns to high. However, FAULT = 1 may still occur because a UVBOOT fault condition may still exist.

**Charge Pump**. The A3946 is designed to accommodate a wide range of power supply voltages. The charge pump output, VREG, is regulated to 13 V nominal.

In all modes, this regulator is current-limited. When  $V_{BB}$ < 8 V, the charge pump operates as a voltage doubler. When 8 V <  $V_{BB}$ < 15 V, the charge pump operates as a voltage doubler/PWM, current-controlled, voltage regulator. When  $V_{BB}$ >15 V, the charge pump operates as a PWM, current-controlled, voltage regulator. Efficiency shifts, from 80% at  $V_{BB}$ = 7 V, to 20% at  $V_{BB}$  = 50 V.

CAUTION. Although simple paralleling of VREG supplies from several A3946s may appear to work correctly, such a configuration is NOT recommended. There is no assurance that one of the regulators will not dominate, taking on all of the load and back-biasing the other regulators. (For example, this could occur if a particular regulator has an internal reference voltage that is higher that those of the other regulators, which would force it to regulate at the highest voltage.)

**Sleep Mode/Power Up**. In Sleep Mode, all circuits are disabled in order to draw minimum current from VBB. When powering up and leaving Sleep Mode (the RESET line is high), the gate drive outputs stay disabled and a fault remains asserted until VREF and VREG pass their undervoltage thresholds. When powering up, before starting the first bootstrap charge cycle, wait until  $t = C_{\text{REG}}/4$  (where  $C_{\text{REG}}$  is in  $\mu$ F, and t is in ns) to allow the charge pump to stabilize.

When powered-up (not in Sleep Mode), if the RESET line is low for > 10  $\mu$ s, the A3946 may start to enter Sleep Mode (V<sub>REF</sub> < 4 V). In that case, ~FAULT = 1 as long as the RESET line remains low.

If the RESET line is open, the A3946 should go into Sleep Mode. However, to ensure that this occurs, the RESET line must be grounded.

**Dead Time**. The analog input pin DT sets the delay to turn on the high- or low-side gate outputs. When instructed to turn off, the gate outputs change after an short internal propagation delay (90 ns typical). The dead time controls the time between this turn-off and the turn-on of the appropriate gate. The duration,  $t_{DEAD}$ , can be adjusted within the range 350 ns to 6000 ns using the following formula:

$$t_{\rm DEAD} = 50 + (R_{\rm DEAD} / 16.7)$$

where  $t_{_{DEAD}}$  is in ns, and  $R_{_{DEAD}}$  is in  $\Omega$ , and should be in the range 5  $k\Omega < R_{_{DEAD}} < 100 \ k\Omega$ .

Do not ground the DT pin. If the DT pin is left open, dead time defaults to  $12 \ \mu s$ .

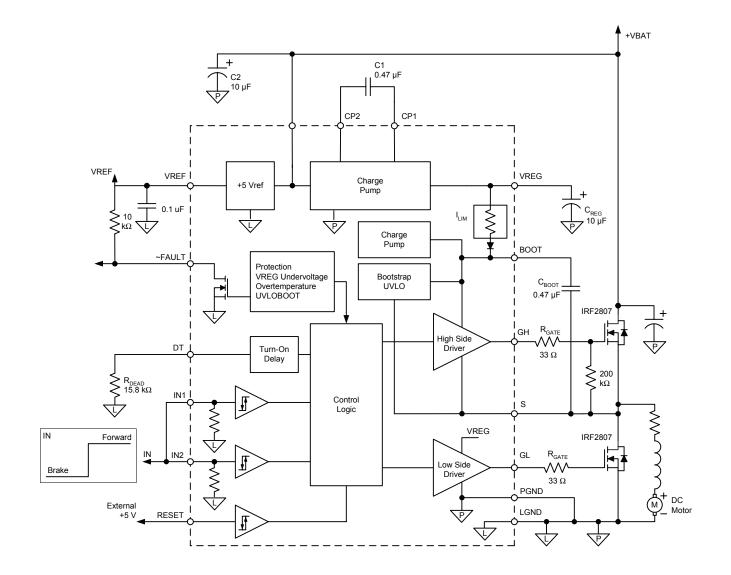

**Control Logic**. Two different methods of control are possible with the A3946. When a resistor is connected from DT to ground, a single-pin PWM scheme is utilized by shorting IN1 with IN2. If a very slow turn-on is required (greater than  $6 \ \mu$ s), the two input pins can be hooked-up individually to allow the dead times to be as long as needed.

The dead time circuit can be disabled by tying the DT pin to VREF. This disables the turn-on delay and allows direct control of each MOSFET gate via two control lines. This is shown in the Control Logic table, on page 2.

**Top-Off Charge Pump.** An internal charge pump allows 100% duty cycle operation of the high-side MOSFET. This is a low-current trickle charge pump, and is only operated after a high-side has been signaled to turn on. A small amount of bias current (< 200  $\mu$ A) is drawn from the BOOT pin to operate the floating high-side circuit. The charge pump simply provides enough drive to ensure that the gate voltage does not droop due to this bias supply current. The charge required for initial turn-on of the high-side gate must be supplied by bootstrap capacitor charge cycles. This is described in the section Application Information.

**VREF.** VREF is used for the internal logic circuitry and is not intended as an external power supply. However, the VREF pin can source up to 4 mA of current. A 0.1  $\mu$ F capacitor is needed for decoupling.

| Fault Mode                               | RESET | ~FAULT | VREG | VREF | <b>GH</b> <sup>1</sup> | <b>GL</b> <sup>1</sup> |

|------------------------------------------|-------|--------|------|------|------------------------|------------------------|

| No Fault                                 | 1     | 1      | ON   | ON   | (IL)                   | (IL)                   |

| BOOT Capacitor Undervoltage <sup>2</sup> | 1     | 0      | ON   | ON   | 0                      | (IL)                   |

| VREG Undervoltage <sup>3</sup>           | 1     | 0      | ON   | ON   | 0                      | 0                      |

| VREF Undervoltage⁴                       | 1     | 0      | OFF  | ON   | 0                      | 0                      |

| Thermal Shutdown <sup>3</sup>            | 1     | 0      | ON   | ON   | (IL)                   | (IL)                   |

| Sleep⁵                                   | 0     | 1      | OFF  | OFF  | High Z                 | High Z                 |

<sup>1</sup>(IL) indicates that the state is determined by the input logic.

<sup>2</sup>This fault occurs whenever there is an undervoltage on the BOOT capacitor. This fault is not latched.

<sup>3</sup>These faults are latched. Clear by pulsing RESET = 0.

<sup>4</sup>Unspecified VREF undervoltage threshold < 4 V.

<sup>5</sup>During power supply undervoltage conditions, GH and GL are instructed to be 0 (low). However, with VREG < 4 V, the outputs start to become high impedance (High Z). Refer to the section *Sleep Mode/Power Up*.

#### **Application Information**

**Bootstrap Capacitor Selection**.  $C_{BOOT}$  must be correctly selected to ensure proper operation of the device. If too large, time is wasted charging the capacitor, with the result being a limit on the maximum duty cycle and PWM frequency. If the capacitor is too small, the voltage drop can be too large at the time the charge is transferred from the  $C_{BOOT}$  to the MOSFET gate.

To keep the voltage drop small:

$$Q_{BOOT} >> Q_{GATE}$$

where a factor in the range of 10 to 20 is reasonable. Using 20 as the factor:

and

$$\begin{split} \mathbf{Q}_{\text{BOOT}} &= \mathbf{C}_{\text{BOOT}} \times \mathbf{V}_{\text{BOOT}} = \mathbf{Q}_{\text{GATE}} \times 20 \\ \mathbf{C}_{\text{BOOT}} &= \mathbf{Q}_{\text{GATE}} \times 20 \ / \ \mathbf{V}_{\text{BOOT}} \end{split}$$

The voltage drop on the BOOT pin, as the MOSFET is being turned on, can be approximated by:

$$Delta_v = Q_{GATE} / C_{BOOT}$$

For example, given a gate charge,  $Q_{GATE}$ , of 160 nC, and the typical BOOT pin voltage of 12 V, the value of the Boot capacitor,  $C_{BOOT}$  can be determined by:

$$C_{\text{BOOT}} = (160 \text{ nC} \times 20) / 12 \text{ V} \approx 0.266 \mu\text{F}$$

Therefore, a 0.22  $\mu$ F ceramic (X7R) capacitor can be chosen for the Boot capacitor.

In that case, the voltage drop on the BOOT pin, when the high-side MOSFET is turned on, is:

Delta\_v =

$$160 \text{ nC} / 0.22 \mu\text{F} = 0.73 \text{ V}$$

**Bootstrap Charging.** It is good practice to ensure that the high-side bootstrap capacitor is completely charged before a high-side PWM cycle is requested.

The time required to charge the capacitor can be approximated by:

$$_{\text{CHARGE}} = C_{\text{BOOT}} (\text{Delta}_v / 100 \text{ mA})$$

At power-up and when the drivers have been disabled for a long time, the bootstrap capacitor can be completely discharged. In this case, Delta\_v can be considered to be the full high-side drive voltage, 12 V. Otherwise, Delta\_v is the amount of voltage dropped during the charge transfer, which should be 400 mV or less. The capacitor is charged whenever the S pin is pulled low, via a GL PWM cycle, and current flows from VREG through the internal bootstrap diode circuit to  $C_{BOOT}$ .

**Power Dissipation.** For high ambient temperature applications, there may be little margin for on-chip power consumption. Careful attention should be paid to ensure that the operating conditions allow the A3946 to remain in a safe range of junction temperature.

The power consumed by the A3946 can be estimated as:

where:

Pd\_bias =

$$V_{BB} \times I_{VBB}$$

, typically 3 mA,

and

Pd\_cpump =

$$(2V_{BB} - V_{REG}) I_{AVE}$$

, for  $V_{BB} < 15$  V, or

Pd\_cpump =  $(V_{DD} - V_{DEG}) I_{AVE}$ , for  $V_{DD} > 15$  V,

in either case, where

$$I_{AVE} = Q_{GATE} \times 2 \times f_{PWM}$$

and

Pd\_switching\_loss =

$$Q_{GATE} \times V_{REG} \times 2 \times f_{PWM}$$

Ratio,

where

Ratio =

$$10 \Omega / (R_{GATE} + 10 \Omega)$$

#### **Application Block Diagrams**

Diagram A. Dependent drivers. Unidirectional motor control with braking and dead time.  $T_{DEAD} = 1 \ \mu s$ ;  $Q_{TOTAL} = 160 \ nC$ .

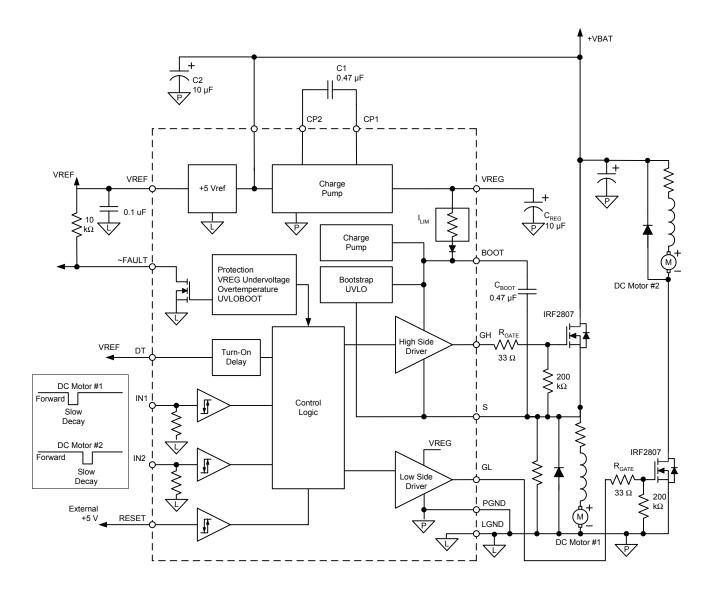

Diagram B. Independent drivers. One high-side drive and one low-side drive.

Diagram C. Independent drivers. Two low-side drives.

| Pin Name | Pin Description                                                                                                                                                                                                     | SOIC-16<br>(A3946KLB) | TSSOP-16<br>(A3946KLP) |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|

| VREG     | Gate drive supply.                                                                                                                                                                                                  | 1                     | 1                      |

| CP2      | Charge pump capacitor, positive side. When not using the charge pump, leave this pin open.                                                                                                                          | 2                     | 2                      |

| CP1      | Charge pump capacitor, negative side. When not using the charge pump, leave this pin open.                                                                                                                          | 3                     | 3                      |

| PGND*    | External ground. Internally connected to the power ground.                                                                                                                                                          | 4                     | 4                      |

| GL       | Low-side gate drive output for external MOSFET driver. External series gate resistor can be used to control slew rate seen at the power driver gate, thereby controlling the di/dt and dv/dt of the S pin output.   | 5                     | 5                      |

| S        | Directly connected to the load terminal. The pin is also connected<br>to the negative side of the bootstrap capacitor and negative supply<br>connection for the floating high-side drive.                           | 6                     | 6                      |

| GH       | High-side gate drive output for N-channel MOSFET driver. External series gate resistor can be used to control slew rate seen at the power driver gate, thereby controlling the di/dt and dv/dt of the S pin output. | 7                     | 7                      |

| BOOT     | High-side connection for bootstrap capacitor, positive supply for the high-side gate drive.                                                                                                                         | 8                     | 8                      |

| ~FAULT   | Diagnostic output, open drain. Low during a fault condition.                                                                                                                                                        | 9                     | 9                      |

| IN1      | Logic control.                                                                                                                                                                                                      | 10                    | 10                     |

| IN2      | Logic control.                                                                                                                                                                                                      | 11                    | 11                     |

| RESET    | Logic control input. When RESET = 0, the chip is in a very low power sleep mode.                                                                                                                                    | 12                    | 12                     |

| LGND*    | External ground. Internally connected to the logic ground.                                                                                                                                                          | 13                    | 13                     |

| DT       | Dead Time. Connecting a resistor to GND sets the turn-on delay to prevent shoot-through. Forcing this input high disables the dead time circuit and changes the logic truth table.                                  | 14                    | 14                     |

| VREF     | 5 V internal reference decoupling terminal.                                                                                                                                                                         | 15                    | 15                     |

| VBB      | Supply Input.                                                                                                                                                                                                       | 16                    | 16                     |

\*In the LB package, the PGND pin (4) and LGND pin (13) grounds are internally connected by the leadframe. In the LP package, however, the PGND pin (4) and LGND pin (13) grounds are NOT internally connected, and both must be connected to ground externally.

In the LP package, the exposed thermal pad is not connected to any pin, but should be externally connected to ground, to reduce noise pickup by the pad.

A3946KLB SOIC

Webbed lead frame. Leads 4 and 13 are joined together within the device package.

#### A3946KLP TSSOP with Exposed Thermal Pad

NOTES:

1. Exact body and lead configuration at vendor's option within limits shown.

2. Lead spacing tolerance is non-cumulative.

3. Supplied in standard sticks/tubes of 49 devices or add "TR" to part number for tape and reel.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copyright©2003, 2004 AllegroMicrosystems, Inc.