# **PLL Clock Multiplier**

#### **Features**

- Zero ppm multiplication error

- Input crystal frequency of 5 30MHz

- Input clock frequency of 4 50MHz

- Output clock frequencies up to 200MHz

- Low period jitter 80ps (100~200MHz)

- Duty cycle 45/55% of output clock

- 9 Selectable frequencies controlled by S<sub>0</sub> and S<sub>1</sub> pins

- Operating voltages of 3.0 to 5.5V

- · Packaging:

- 8-pin SOIC (W)

- Pb-Free and Green 8-pin SOIC (WE)

### **Description**

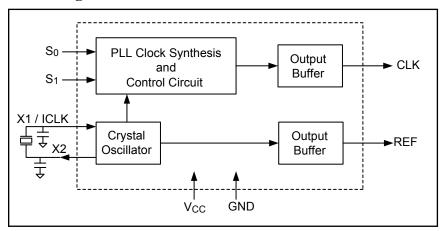

Pericom Semiconductor's PI6C4512 is a precision general-purpose clock synthesizer that reaches maximum 200MHz. This device uses an external low-cost crystal to generate very accurate rate and stable system clocks. This is the most cost effective way to reduce high-price, high frequency crystals. Using PLL techniques, the device uses a standard fundamental mode, inexpensive crystal to produce output clocks up to 200 MHz.

The internal Logic divider is to generate nine different popular multiplication factors, allowing one chip to output many common frequencies.

## **Block Diagram**

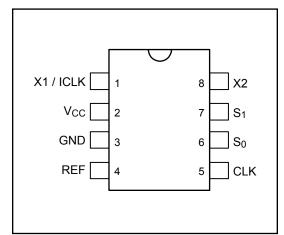

# **Pin Configuration**

#### **Clock Output Table**

| $S_1$ | $S_0$ | CLK      |

|-------|-------|----------|

| 0     | 0     | x 4      |

| 0     | M     | x (16/3) |

| 0     | 40,   | x 5      |

| M     | 0     | x 2.5    |

| M     | M     | x 2      |

| M     | 1     | x (10/3) |

| 1     | 0     | x 6      |

| 1     | M     | x 3      |

| 1     | 1     | x 8      |

#### Notes:

1. M = leave unconnected (self-biases to V<sub>CC</sub>/2).

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested)

| Storage temperature                                   | 65 to 150°C                  |

|-------------------------------------------------------|------------------------------|

| Ambient Operating Temperature                         |                              |

| Supply Voltage to Ground Potential (V <sub>CC</sub> ) | 0.3 to +7.0V                 |

| Inputs (Referenced to GND)                            | 0.5 to V <sub>CC</sub> +0.5V |

| Clock Output (Referenced to GND)                      | 0.5 to V <sub>CC</sub> +0.5V |

| Soldering Temperature (Max of 10 seconds)             | 260°C (Max.10s)              |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Pin Description**

| Name     | Pin | Description                                                                         |  |

|----------|-----|-------------------------------------------------------------------------------------|--|

| X1/ICLK  | 1   | Crystal connection or clock input.                                                  |  |

| $V_{CC}$ | 2   | Connect to +3.3V or +5V.                                                            |  |

| GND      | 3   | Ground                                                                              |  |

| REF      | 4   | Buffered crystal oscillator output clock                                            |  |

| CLK      | 5   | Clock output                                                                        |  |

| $S_0$    | 6   | Multiplier select pin 0. Connect to GND or V <sub>CC</sub> or float (no connection) |  |

| $S_1$    | 7   | Multiplier select pin 1. Connect to GND or V <sub>CC</sub> or float (no connection) |  |

| X2       | 8   | Crystal connection. Leave unconnected for clock input.                              |  |

#### **External Components**

The PI6C4512 requires a minimum number of external components for proper operation. Decoupling capacitors of  $0.01\mu F$  should be connected between each  $V_{DD}$  and GND as close to the chip as possible. A series termination resistor of  $33\Omega$  may be used for each clock output. The crystal should be a fundamental mode, parallel resonant. Crystal capacitors should be connected from  $X_1$  to ground and  $X_2$  to ground to optimize the inital accuracy. The value of these capacitors igiven by the following equation, where  $C_L$  is the crystal load capacitance: Crystal caps (pF) = ( $C_L$ -15) x2. So for a crystal with 18pF load capacitance, two 6pF caps should be used.

2

# **Recommended Operation Conditions**

| Symbol   | Description           | Test Condition | Min. | Тур. | Max. | Units |

|----------|-----------------------|----------------|------|------|------|-------|

| $V_{CC}$ | Supply Voltage        |                | 3    |      | 5.5  | V     |

| TA       | Operating Temperature |                | 0    |      | 70   | °C    |

# **DC Electrical Characteristics** ( $V_{CC} = 3.3V \pm 0.3V$ , $T_A = 0 \sim 70^{\circ}C$ , unless otherwise noted)

| Symbol            | Description               | Test Condition         | Pin                             | Min.                 | Тур.               | Max.                   | Units |

|-------------------|---------------------------|------------------------|---------------------------------|----------------------|--------------------|------------------------|-------|

| V <sub>CC</sub>   | Supply voltage            |                        | V <sub>CC</sub>                 | 3                    |                    | 5.5                    | V     |

| $I_{CC}$          | Supply current            | no load, 20MHz Crystal | $V_{CC}$                        | `                    | 12                 | 20                     | mA    |

| $V_{\mathrm{IH}}$ | Input logic high          |                        | ICLK                            | $(V_{CC}/2) + 1$     | V <sub>CC</sub> /2 |                        |       |

| $V_{IL}$          | Input logic low           |                        | ICLK                            |                      | V <sub>CC</sub> /2 | (V <sub>CC</sub> /2)-1 |       |

| $V_{\mathrm{IH}}$ | Input logic high          |                        | S <sub>0</sub> , S <sub>1</sub> | V <sub>CC</sub> -0.5 |                    |                        |       |

| $V_{IM}$          | Input mid-level           |                        | $S_0, S_1$                      |                      | V <sub>CC</sub> /2 |                        | V     |

| $V_{\rm IL}$      | Input logic low           |                        | S <sub>0</sub> , S <sub>1</sub> |                      |                    | 0.5                    |       |

| $V_{OH}$          | High-level output voltage | $I_{OH} = -12mA$       | CLK, REF                        | 2.4                  |                    |                        |       |

| $V_{OL}$          | Low-level output voltage  | $I_{OL} = 12mA$        | CLK, REF                        |                      |                    | 0.4                    |       |

| Is                | Short circuit current     |                        | CLK                             |                      | ±70                |                        | mA    |

## **AC Electrical Characteristics** ( $V_{CC} = 3.3V \pm 0.3V$ , $T_A = 0 \sim 70$ °C, unless noted)

| Symbol           | Parameter                       | Test Condition                 | Pin  | Min. | Typ. | Max. | Unit |

|------------------|---------------------------------|--------------------------------|------|------|------|------|------|

|                  | Innert Francisco                | Crystal                        | ICLK | 5    |      | 30   |      |

| $f_{IN}$         | Input Frequency                 | Clock                          | ICLK | 4    |      | 50   | MII- |

|                  | V <sub>CC</sub> : 4.5 to 5.5V   | CLK                            | 20   |      | 200  | MHz  |      |

| $f_{OUT}$        | Output frequency <sup>(2)</sup> | V <sub>CC</sub> : 3.0 to 3.6V  | CLK  | 20   |      | 180  |      |

| t <sub>r</sub>   | Output clock rise time          | 0.8 to 2.0V,<br>with 15pF load | CLK  |      | 1    |      |      |

| $t_{\mathrm{f}}$ | Output clock fall time          | 2.0 to 0.8V,<br>with 15pF load | CLK  |      | 1    |      | ns   |

| Duty             | Output clock duty ycle          | At V <sub>CC</sub> /2          | CLK  | 45   | 50   | 55   | %    |

|                  | PLL bandwidth <sup>(1)</sup>    |                                |      | 10   |      |      | kHz  |

|                  | Period Jitter                   | 100MHz~200MHz                  | CLK  |      | 80   | 100  | ps   |

3

#### Notes:

- 1. Only reference for design

- 2. The phase relationship between input and output clocks can change at power up.

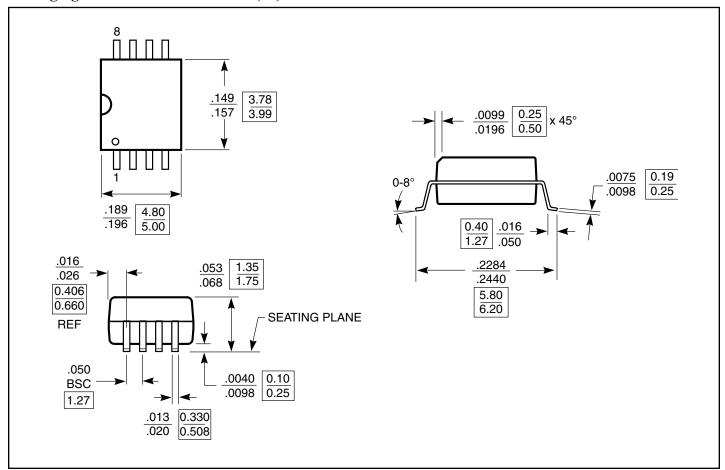

#### Packaging Mechanical: 8-Pin SOIC (W)

### **Ordering Information**

| Ordering Code | Package Code | Package Description          |

|---------------|--------------|------------------------------|

| PI6C4512W     | W            | 8-pin SOIC                   |

| PI6C4512WE    | WE           | Pb-Free and Green 8-pin SOIC |

#### Notes

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

4