# 3.3 V Slew Rate Limited, Half Duplex RS-485/RS-422 Transceiver

# ADM3493

### **FEATURES**

Operates with 3.3 V supply Interoperable with 5 V logic EIA RS-422 and RS-485 compliant over full CM range Data rate: 250 kbps Half duplex transceiver Reduced slew rates for low EMI 2 nA supply current in shutdown mode Up to 256 transceivers on a bus -7 V to +12 V bus common-mode range Specified over -40°C to +85°C temperature range 8 ns skew Available in 8-lead SOIC

### **APPLICATIONS**

Low power RS-485 applications EMI sensitive systems DTE-DCE interfaces Industrial control Packet switching Local area networks Level translators

### **GENERAL DESCRIPTION**

The ADM3493 is a low power, differential line transceiver designed to operate using a single 3.3 V power supply. Low power consumption, coupled with a shutdown mode, makes it ideal for power-sensitive applications. The ADM3493 is suitable for communication on multipoint bus transmission lines.

The device contains one driver and one receiver. Designed for half-duplex communication, the ADM3493 features a slew rate limited driver that minimizes EMI and reduces reflections caused by improperly terminated cables, allowing error-free data transmission at data rates up to 250 kbps. The receiver input impedance is 96 k $\Omega$ , allowing up to 256 transceivers to be connected on the bus. A thermal shutdown circuit prevents excessive power dissipation caused by bus contention or by output shorting. If a significant temperature increase is detected in the internal driver circuitry during fault conditions then the thermal shutdown circuit forces the driver output into a high impedance state. The receiver contains a fail-safe feature that results in a logic high output state, if the inputs are unconnected (floating).

The ADM3493 is fully specified over the commercial and industrial temperature ranges and is available in an 8-lead SOIC.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

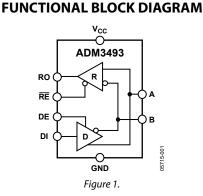

| Functional Block Diagram1                    |

| General Description                          |

| Revision History                             |

| Specifications                               |

| Timing Specifications                        |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configurations and Function Descriptions |

| Test Circuits                                |

### **REVISION HISTORY**

10/05—Rev. 0: Initial Version

| Switching Characteristics           | 8  |

|-------------------------------------|----|

| Typical Performance Characteristics | 9  |

| Circuit Description                 | 11 |

| Reduced EMI and Reflections         | 11 |

| Low Power Shutdown Mode             | 11 |

| Driver Output Protection            | 11 |

| Propagation Delay                   | 11 |

| Typical Applications                | 11 |

| Outline Dimensions                  | 12 |

| Ordering Guide                      | 12 |

## **SPECIFICATIONS**

$V_{\text{CC}}$  = 3.3 V ±0.3 V,  $T_{\text{A}}$  =  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$  unless otherwise noted.

### Table 1.

| Parameter                                                                | Min                   | Тур   | Max  | Units | Test Condit                                                            | Test Conditions/Comments              |  |

|--------------------------------------------------------------------------|-----------------------|-------|------|-------|------------------------------------------------------------------------|---------------------------------------|--|

| DRIVER                                                                   |                       |       |      |       |                                                                        |                                       |  |

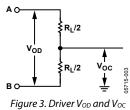

| Differential Output Voltage, Vod                                         | 2.0                   |       |      | V     | $R_L$ = 100 Ω (RS-422), $V_{cc}$ = 3.3 V<br>±5% (see Figure 3)         |                                       |  |

|                                                                          | 1.5                   |       |      | V     | $R_L = 54 \Omega$ (R                                                   | S-485) (see Figure 3)                 |  |

|                                                                          | 1.5                   |       |      | V     | $R_L = 60 \Omega (R)$<br>(see Figure 4                                 | S-485), V <sub>cc</sub> = 3.3 V<br>4) |  |

| $\Delta$  V <sub>OD</sub>   for Complementary Output States <sup>1</sup> |                       |       | 0.2  | V     | $R_L = 54 \Omega \text{ or}$                                           | $100\Omega$ (see Figure 3)            |  |

| Common-Mode Output Voltage, Voc                                          |                       |       | 3    | V     | $R_L = 54 \Omega \text{ or}$                                           | $100\Omega$ (see Figure 3)            |  |

| $\Delta$  V <sub>oc</sub>   for Common-Mode Output Voltage <sup>1</sup>  |                       |       | 0.2  | V     | $R_L = 54 \Omega \text{ or}$                                           | 100 $\Omega$ (see Figure 3)           |  |

| DRIVER INPUT LOGIC                                                       |                       |       |      |       |                                                                        |                                       |  |

| CMOS Input Logic Threshold Low, V⊪                                       |                       |       | 0.8  | V     | DE, DI, RE                                                             |                                       |  |

| CMOS Input Logic Threshold High, $V_{IL}$                                | 2.0                   |       |      | V     | DE, DI, RE                                                             |                                       |  |

| CMOS Logic Input Current, I <sub>N1</sub>                                |                       |       | ±2   | μΑ    | DE, DI, RE                                                             |                                       |  |

| Input Current (A, B), I <sub>N2</sub>                                    |                       | 60    |      | μΑ    | $V_{IN} = 12 V$                                                        | DE = 0 V                              |  |

|                                                                          |                       | -60   |      | μΑ    | $V_{IN} = -7 V$                                                        | $V_{CC} = 0 V \text{ or } 3.6 V$      |  |

| RECEIVER                                                                 |                       |       |      |       |                                                                        |                                       |  |

| Differential Input Threshold Voltage, VTH                                | -0.2                  |       | 0.2  | V     | $-7V < V_{CM} < +12 V$<br>$V_{CM} = 0 V$                               |                                       |  |

| Input Hysteresis, $\Delta V_{TH}$                                        |                       | 50    |      | mV    |                                                                        |                                       |  |

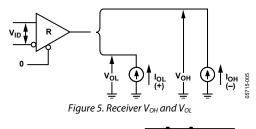

| CMOS Output Voltage High, V <sub>OH</sub>                                | V <sub>cc</sub> – 0.4 |       |      | V     | $I_{OUT} = -1.5 \text{ mA}, V_{ID} = 200 \text{ mV}$<br>(see Figure 5) |                                       |  |

| CMOS Output Voltage Low, Vol                                             |                       |       | 0.4  | V     | $I_{OUT} = 2.5 \text{mA}, V_{ID} = 200 \text{mV}$<br>(see Figure 5)    |                                       |  |

| Three-State Output Leakage Current, Iozr                                 |                       |       | ±1   | μΑ    | $V_{cc} = 3.6 V, 0$                                                    | $V \leq V_{OUT} \leq V_{cc}$          |  |

| Input Resistance, R <sub>IN</sub>                                        |                       | 96    |      | kΩ    | $-7 V < V_{CM} < + 12 V$                                               |                                       |  |

| POWER SUPPLY CURRENT                                                     |                       |       |      |       |                                                                        |                                       |  |

| Supply Current                                                           |                       | 1.1   | 2.2  | mA    | $DE = V_{CC}$                                                          |                                       |  |

|                                                                          |                       |       |      |       | $\overline{\text{RE}} = 0 \text{ V or } \text{V}$                      | /cc No load,                          |  |

|                                                                          |                       | 0.95  | 1.9  | mA    | DE = V <sub>cc</sub>                                                   | DI = 0 V or V <sub>CC</sub>           |  |

|                                                                          |                       |       |      |       | $\overline{\text{RE}} = 0 \text{ V}$                                   |                                       |  |

| Supply Current in Shutdown Mode, Ishda                                   |                       | 0.002 | 1    | μΑ    | $DE = 0 V, \overline{RE} = V_{CC}, DI = V_{CC} or$                     |                                       |  |

| Driver Short-Circuit Output Current, Iosd                                |                       |       | -250 | mA    | $V_{OUT} = -7 V$                                                       |                                       |  |

|                                                                          |                       |       | 250  | mA    | $V_{\text{OUT}} = 12  V$                                               |                                       |  |

| Receiver Short-Circuit Output Current, Iosr                              | ±8                    |       | ±60  | mA    | $0 V < V_{RO} < V$                                                     | /cc                                   |  |

$^1\Delta V_{\text{OD}}$  and  $\Delta V_{\text{OC}}$  are the changes in  $V_{\text{OD}}$  and  $V_{\text{OC}}$ , respectively, when DI input changes state.

### **TIMING SPECIFICATIONS**

$V_{CC}$  = 3.3 V,  $T_A$  = 25°C, unless otherwise noted.

### Table 2.

| Parameter                                                                                    | Min | Тур  | Max  | Units | Test Conditions/Comments                                             |

|----------------------------------------------------------------------------------------------|-----|------|------|-------|----------------------------------------------------------------------|

| DRIVER                                                                                       |     |      |      |       |                                                                      |

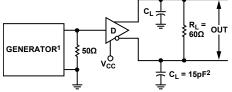

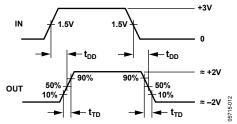

| Differential Output Delay, tDD                                                               | 600 | 900  | 1400 | ns    | $R_L = 60 \Omega$ (see Figure 6 and Figure 12)                       |

| Differential Output Transition Time, trd                                                     | 400 | 700  | 1200 | ns    | $R_L = 60 \Omega$ (see Figure 6 and Figure 12)                       |

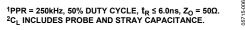

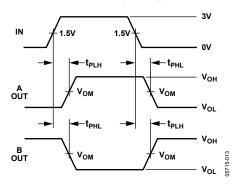

| Propagation Delay, Low-to-High Level, $t_{PLH}$                                              | 700 | 1000 | 1500 | ns    | $R_L = 27 \Omega$ (see Figure 7 and Figure 13)                       |

| Propagation Delay, High-to-Low Level, tPHL                                                   | 700 | 1000 | 1500 | ns    | $R_L = 27 \Omega$ (see Figure 7 and Figure 13)                       |

| t <sub>PLH</sub> – t <sub>PHL</sub>   Propagation Delay Skew <sup>1</sup> , t <sub>PDs</sub> |     | 100  |      | ns    | $R_L = 27 \Omega$ (see Figure 7 and Figure 13)                       |

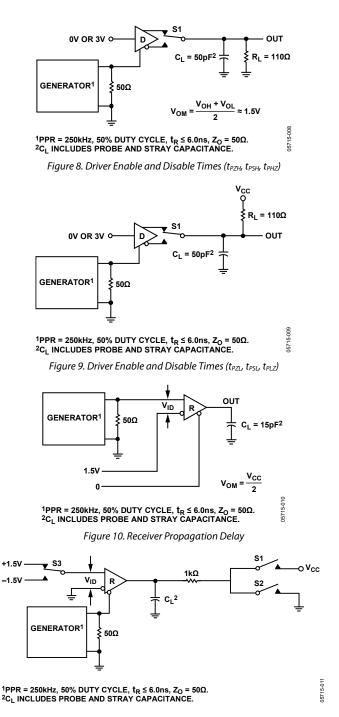

| DRIVER OUTPUT ENABLE/DISABLE TIMES                                                           |     |      |      |       |                                                                      |

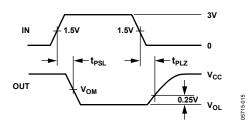

| Output Enable Time to Low Level, tPZL                                                        |     | 900  | 1300 | ns    | $R_L = 110 \Omega$ (see Figure 9 and Figure 15)                      |

| Output Enable Time to High Level, t <sub>PZH</sub>                                           |     | 600  | 800  | ns    | $R_L = 110 \Omega$ (see Figure 8 and Figure 14)                      |

| Output Disable Time from High Level, t <sub>PHZ</sub>                                        |     | 50   | 80   | ns    | $R_L = 110 \Omega$ (see Figure 8 and Figure 14)                      |

| Output Disable Time from Low Level, t <sub>PLZ</sub>                                         |     | 50   | 80   | ns    | $R_L = 110 \Omega$ (see Figure 9 and Figure 15)                      |

| Output Enable Time from Shutdown to Low Level, t <sub>PSL</sub>                              |     | 1.9  | 2.7  | μs    | $R_L$ = 110 $\Omega$ (see Figure 9 and Figure 15)                    |

| Output Enable Time from Shutdown to<br>High Level, t <sub>PSH</sub>                          |     | 2.2  | 3.0  | μs    | $R_L$ = 110 $\Omega$ (see Figure 8 and Figure 14)                    |

| RECEIVER                                                                                     |     |      |      |       |                                                                      |

| Time to Shutdown <sup>2</sup> , t <sub>SHDN</sub>                                            | 80  | 190  | 300  | ns    |                                                                      |

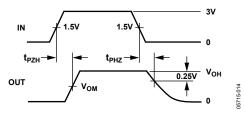

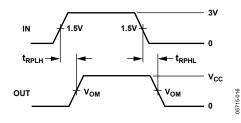

| Propagation Delay, Low-to-High Level, $t_{\text{RPLH}}$                                      | 25  | 75   | 180  | ns    | $V_{ID} = 0$ V to 3.0 V, $C_L = 15$ pF (see Figure 10 and Figure 16) |

| Propagation Delay, High-to-Low Level, $t_{\text{RPHL}}$                                      | 25  | 75   | 180  | ns    | $V_{ID} = 0$ V to 3.0 V, $C_L = 15$ pF (see Figure 10 and Figure 16) |

| $ t_{PLH} - t_{PHL} $ Propagation Delay Skew, $t_{RPDS}$                                     |     |      | 50   | ns    | $V_{ID} = 0$ V to 3.0 V, $C_L = 15$ pF (see Figure 10 and Figure 16) |

| RECEIVER OUTPUT ENABLE/DISABLE TIMES                                                         |     |      |      |       |                                                                      |

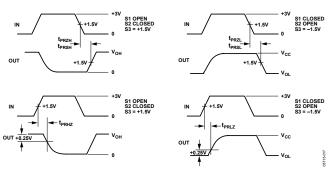

| Output Enable Time to Low Level, tPRZL                                                       |     | 25   | 50   | ns    | $C_L = 15 \text{ pF}$ (see Figure 11 and Figure 17)                  |

| Output Enable Time to High Level, tPRZH                                                      |     | 25   | 50   | ns    | $C_L = 15 \text{ pF}$ (see Figure 11 and Figure 17)                  |

| Output Disable Time from High Level, tPRHZ                                                   |     | 25   | 45   | ns    | $C_L = 15 \text{ pF}$ (see Figure 11 and Figure 17)                  |

| Output Disable Time from Low Level, tPRLZ                                                    |     | 25   | 45   | ns    | $C_L = 15 \text{ pF}$ (see Figure 11 and Figure 17)                  |

| Output Enable Time from Shutdown to Low Level, t <sub>PRSL</sub>                             |     | 720  | 1400 | ns    | $C_L = 15 \text{ pF}$ (see Figure 11 and Figure 17)                  |

| Output Enable Time from Shutdown to<br>High Level, t <sub>PRSH</sub>                         |     | 720  | 1400 | ns    | $C_L = 15 \text{ pF}$ (see Figure 11 and Figure 17)                  |

<sup>1</sup> Measured on  $|t_{PLH}(A) - t_{PHL}(A)|$  and  $|t_{PLH}(B) - t_{PHL}(B)|$ . <sup>2</sup> The transceivers are put into shutdown by bringing RE high and DE low. If the inputs are in this state for less than 80 ns, the parts are guaranteed not to enter shutdown. If the inputs are in this state for at least 300 ns, the parts are guaranteed to enter shutdown.

## ABSOLUTE MAXIMUM RATINGS

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Tuble 5.                                |                                      |

|-----------------------------------------|--------------------------------------|

| Parameter                               | Rating                               |

| V <sub>cc</sub> to GND                  | 7 V                                  |

| Digital I/O Voltage (DE, RE, DI)        | -0.3 V to Vcc + 0.3 V                |

| Digital I/O Voltage (R <sub>OUT</sub> ) | $V_{CC}$ – 0.5 V to $V_{CC}$ + 0.5 V |

| Driver Output/Receiver Input Voltage    | –7.5 V to +12.5 V                    |

| Operating Temperature Range             | -40°C to +85°C                       |

| Storage Temperature Range               | –65°C to +125°C                      |

| θ <sub>JA</sub> Thermal Impedance       |                                      |

| 8-Lead SOIC                             | 121°C/W                              |

| Lead Temperature                        |                                      |

| Soldering (10 seconds)                  | 300°C                                |

| Vapor Phase (60 seconds)                | 215℃                                 |

| Infrared (15 seconds)                   | 220°C                                |

|                                         | ÷                                    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

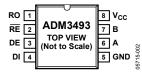

Figure 2. Pin Configuration

#### Table 4. . Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                                                                                                                                                                    |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RO       | Receiver Output. When enabled, if $A > B$ by 200 mV, then $RO = high$ .<br>If $A < B$ by 200 mV, then $RO = low$ .                                                                                             |

| 2       | RE       | Receiver Output Enable. A low level enables the receiver output, RO. A high level places it in a high impedance state. If RE is high and DE is low, the device enters a low power shutdown mode.               |

| 3       | DE       | Driver Output Enable. A high level enables the driver differential Outputs A and B. A low level places it in a high impedance state. If RE is high and DE is low, the device enters a low power shutdown mode. |

| 4       | DI       | Driver Input. When the driver is enabled, a logic low on DI forces A low and B high while a logic high on DI forces A high and B low.                                                                          |

| 5       | GND      | Ground.                                                                                                                                                                                                        |

| 6       | А        | Noninverting Receiver Input A and Noninverting Driver Output A.                                                                                                                                                |

| 7       | В        | Inverted Receiver Input B and Inverted Driver Output B.                                                                                                                                                        |

| 8       | Vcc      | Power Supply, 3.3 V $\pm$ 0.3 V.                                                                                                                                                                               |

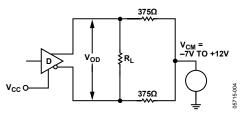

Figure 4. Driver Vod with Varying Common-Mode Voltage

Figure 6. Driver Differential Output Delay and Transition Times

Figure 11. Receiver Enable and Disable Times

### SWITCHING CHARACTERISTICS

Figure 12. Driver Differential Output Delay and Transition Times

Figure 13. Driver Propagation Delays

Figure 14. Driver Enable and Disable Times (t<sub>PZH</sub>, t<sub>PSH</sub>, t<sub>PHZ</sub>)

Figure 15. Driver Enable and Disable Times (t<sub>PZL</sub>, t<sub>PSL</sub>, t<sub>PLZ</sub>)

Figure 16. Receiver Propagation Delay

Figure 17. Receiver Enable and Disable Times

### **TYPICAL PERFORMANCE CHARACTERISTICS**

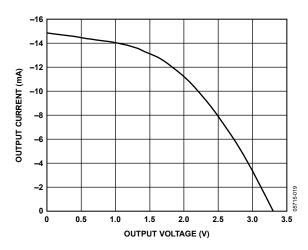

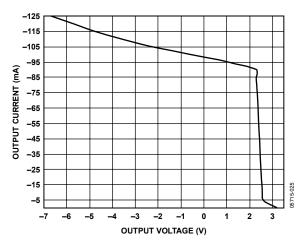

Figure 18. Output Current vs. Receiver Output Low Voltage

Figure 19. Output Current vs. Receiver Output High Voltage

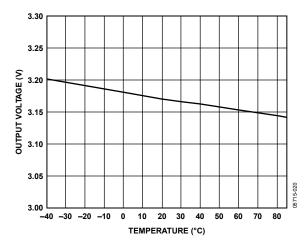

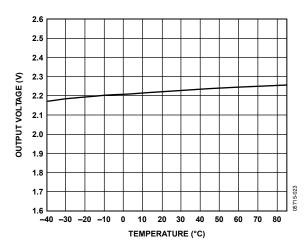

Figure 20. Receiver Output High Voltage vs. Temperature,  $I_0 = 1.5 \text{ mA}$

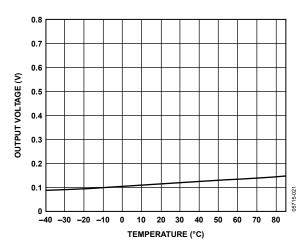

Figure 21. Receiver Output Low Voltage vs. Temperature,  $I_0 = 2.5 \text{ mA}$

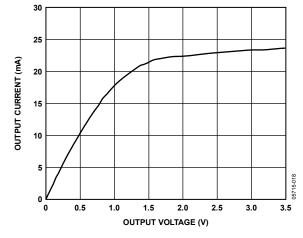

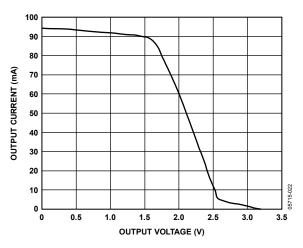

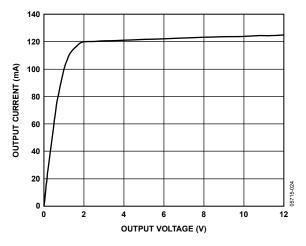

Figure 22. Driver Output Current vs. Differential Output Voltage

Figure 23. Driver Differential Output Voltage vs. Temperature,  $RI = 54 \Omega$

Figure 24. Output Current vs. Driver Output Low Voltage

Figure 25. Output Current vs. Driver Output High Voltage

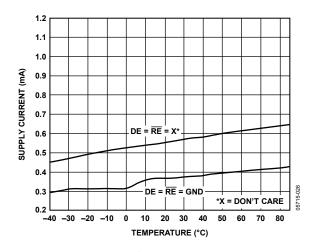

Figure 26. Supply Current vs. Temperature

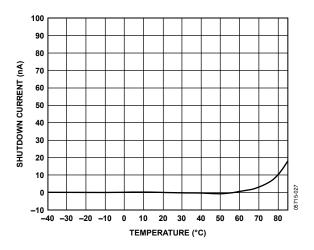

Figure 27. Shutdown Current vs. Temperature,  $V_{CC} = 3.3 V$

## **CIRCUIT DESCRIPTION**

The ADM3493 is a low power transceiver for RS-485 and RS-422 communications. The ADM3493 can transmit and receive at data rates up to 250 kbps in a half duplex configuration. Driver Enable (DE) and Receiver Enable ( $\overline{\text{RE}}$ ) pins are included when disabled; the driver and receiver outputs are high impedance.

| Tran                  | smitting In | puts           | Transn<br>Out       | Mode                |        |  |  |

|-----------------------|-------------|----------------|---------------------|---------------------|--------|--|--|

| RE                    | DE          | DI             | В                   | Α                   |        |  |  |

| X <sup>1</sup>        | 1           | 1              | 0                   | 1                   | Normal |  |  |

| <b>X</b> <sup>1</sup> | 1           | 0              | 1                   | 0                   | Normal |  |  |

| 0                     | 0           | X <sup>1</sup> | High-Z <sup>2</sup> | High-Z <sup>2</sup> | Normal |  |  |

Χ1

#### Table 5. Transmitting Truth Table

<sup>1</sup> X = Don't care.

1

<sup>2</sup> High-Z = High Impedance.

#### Table 6. Receiving Truth Table

0

| Receiving Inputs |   |                | Receiving Inputs Receiving<br>Outputs |          |  |  |

|------------------|---|----------------|---------------------------------------|----------|--|--|

| RE DE A-B        |   |                | RO                                    |          |  |  |

| 0                | 0 | ≥+0.2 V        | 1                                     | Normal   |  |  |

| 0                | 0 | ≤–0.2 V        | 0                                     | Normal   |  |  |

| 0                | 0 | Inputs Open    | 1                                     | Normal   |  |  |

| 1                | 0 | X <sup>1</sup> | High-Z <sup>2</sup>                   | Shutdown |  |  |

High-Z<sup>2</sup>

High-Z<sup>2</sup>

Shutdown

$^{1}$  X = Don't care.

<sup>2</sup> High-Z = High Impedance

### **REDUCED EMI AND REFLECTIONS**

The ADM3493 is a slew rate limited transceiver, minimizing EMI and reducing reflections caused by improperly terminated cables.

### LOW POWER SHUTDOWN MODE

A low power shutdown mode is initiated by bringing both  $\overline{RE}$  high and DE low. The ADM3493 does not shut down unless both the driver and receiver are disabled (high impedance). In shutdown, the ADM3493 typically draws only 2 nA of supply current. For the ADM3493, the t<sub>PSH</sub> and t<sub>PSL</sub> enable times assume the part was in the low power shutdown mode; the t<sub>PZH</sub> and t<sub>PZL</sub> enable times assume the receiver or driver was disabled, but the part was not shut down.

### **DRIVER OUTPUT PROTECTION**

Two methods are implemented to prevent excessive output current and power dissipation caused by faults or by bus contention. Current limit protection on the output stage provides immediate protection against short circuits over the whole common-mode voltage range (see Typical Performance Characteristics). In addition, a thermal shutdown circuit forces the driver outputs into a high impedance state if the die temperature rises excessively.

### **PROPAGATION DELAY**

Skew time is simply the difference between the low-to-high and high-to-low propagation delay. Small driver/receiver skew times help maintain a symmetrical mark-space ratio (50% duty cycle). The receiver skew time,  $|t_{PRLH} - t_{PRHL}|$ , is 20 ns for the ADM3493. The driver skew time is typically under 100 ns.

### **TYPICAL APPLICATIONS**

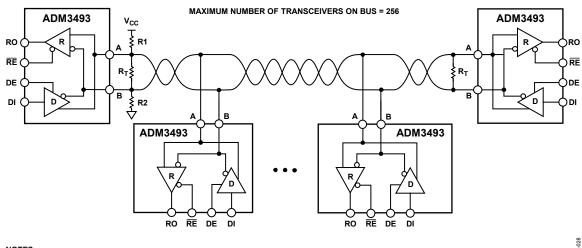

The ADM3493 transceiver is designed for bidirectional data communications on multipoint bus transmission lines. Figure 22 shows a typical network application's circuits. To minimize reflections, the line should be terminated at both ends in its characteristic impedance, and stub lengths off the main line should be kept as short as possible. The slew rate limited ADM3493 is tolerant of imperfect termination.

NOTES 1.  $R_T$  IS EQUAL TO THE CHARACTERISTIC IMPEDANCE OF THE CABLE.

Figure 28. ADM3493 Typical Half Duplex RS-485 Network

### **OUTLINE DIMENSIONS**

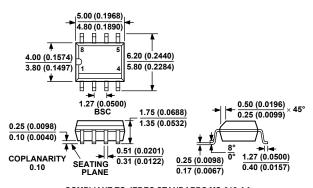

COMPLIANT TO JEDEC STANDARDS MS-012-AA CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 29. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

|                               |                   |                                                |                 | Ordering |

|-------------------------------|-------------------|------------------------------------------------|-----------------|----------|

| Model                         | Temperature Range | Package Description                            | Package Options | Quantity |

| ADM3493ARZ <sup>1</sup>       | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8             |          |

| ADM3493ARZ-REEL7 <sup>1</sup> | –40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8             | 1,000    |

$^{1}$  Z = Pb-free part.

www.analog.com