# OKI Semiconductor ML674000

Network Solutions Oki for a Global Society

**FEDL674000-02** Issue Date: Dec. 10, 2002

# 32-bit General-purpose, ARM-based Microcontroller

# GENERAL DESCRIPTION

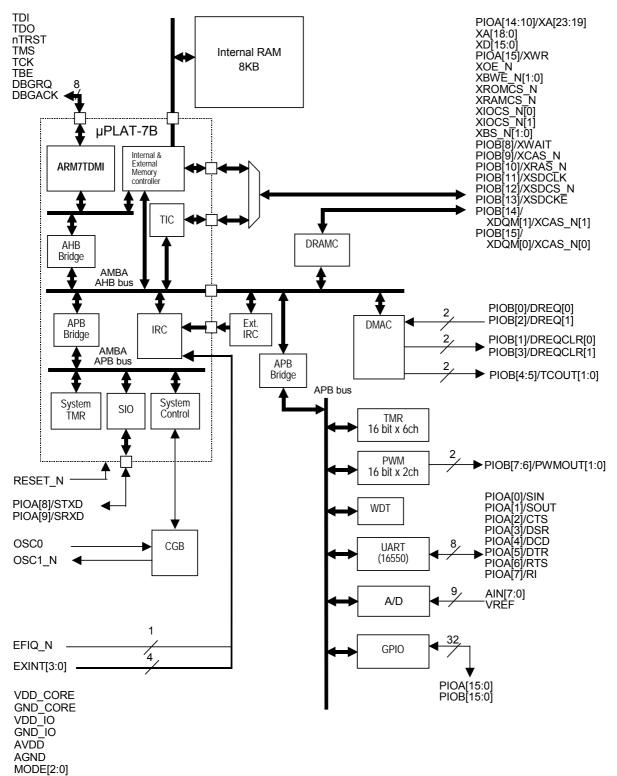

Oki's ML674000 standard microcontroller (MCU) is a member of an extensive and growing family of ARM<sup>®</sup> architecture 32-bit MCUs for general-purpose applications that require 32-bit CPU performance and low cost afforded by MCU integrated features.

ML674000 MCU provides a host of useful peripherals such as 8KB of on-board SRAM, timers, watchdog timer, pulse-width modulators, AD converter, UART's, GPIO connectivity capability, and external memory controller. These integrated features make it ideal for embedded applications where low costs and low power consumption are key.

Oki's ML674K series MCUs are capable of executing both the 32-bit ARM instruction set for high-performance applications as well as the 16-bit Thumb<sup>®</sup> instruction set for power-efficient applications. With an ARM7TDMI<sup>®</sup> core operating at 33 MHz maximum frequency, ARM Thumb<sup>™</sup> capabilities, and robust feature sets, the ML674K series MCUs are suitable for an array of applications including high performance industrial controllers and instrumentation, telecom, PC peripherals, security/surveillance, test equipment, and a variety of consumer electronics devices.

# The ARM7TDMI<sup>®</sup> Advantage

Oki's ML67 Family of low-cost ARM-based MCUs offers system designers a bridge from 8- and 16-bit proprietary MCU architectures to ARM's higher-performance, affordable, widely-accepted industry standard architecture and its industry-wide support infrastructure. The ARM industry infrastructure offers system developers many advantages including software compatibility, many ready-to-use software applications, and numerous choices among hardware and software development tools. These ARM-based advantages allow Oki's customers to better leverage engineering resources, lower development costs, minimize project risks, and reduce their product time to market. In addition, migration of a design with an Oki standard MCU to an Oki custom solution is easily facilitated with its award-winning  $\mu$ PLAT<sup>TM</sup> product development architecture.

# FEATURES

• CPU

32-bit RISC CPU (ARM7TDMI)

32-bit instructions (ARM Instructions) and 16-bit instructions (Thumb Instructions) mixed General purpose registers : 31 x 32 bits Built-in Barrel shifter and multiplier (32 bit x 8 bit, Modified Booth's Algorithm) Little endian Built-in debug function

- Internal memory RAM 8KB (32-bit access)

- External memory controller ROM (FLASH): 16 Mbytes SRAM: 16 Mbytes DRAM: 64 Mbytes (SDRAM and EDO-DRAM support)

External IO devices: 16 Mbytes x 2 banks (with wait control by external signal)

ARM, ARM7TDMI, Multi-ICE and AMBA are registered trademarks of ARM Ltd., UK. µPLAT is Oki's trademark.

The contents of this data sheet are subject to change for modification without notice.

- Interrupt controller

- 24 sources: 19 internals and 5 externals (IRQ: 4, FIQ: 1)

- DMA controller

- 2 channels: Dual address mode, cycle steal and burst tranfer mode

- Timer

- 1 channel: 16-bit auto reload for operating system 6 channels: 16-bit auto reload for application

- 1 channel: 16 bit watchdog timer

- Serial interface

- 1 channel: UART

- 1 channel: UART with 16-byte FIFO

- Parallel I/O Port

- 2 ports x 16 bits (bitwise input/output settings)

- PWM

- 2 channels x 16 bits

- Analog-to-Digital Converter 8 channels x 10 bits

- Power down mechanism Standby (all clock stop) and Halt (clock stop by each function block) Clock gear (selectable 1/1, 1/2, 1/4, 1/8, 1/16 input clock frequency)

- JTAG interface

- Connectable to JTAG ICE (e.g. ARM MutiICE)

- Power supply voltage Core section: 2.25 V to 2.75 V IO section: 3.0 V to 3.6 V

- Operating frequency 33 MHz (Max.)

- Operating temperature (ambient temperature) -40°C to +85°C

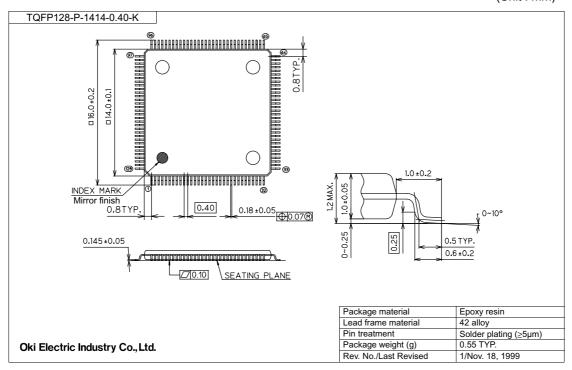

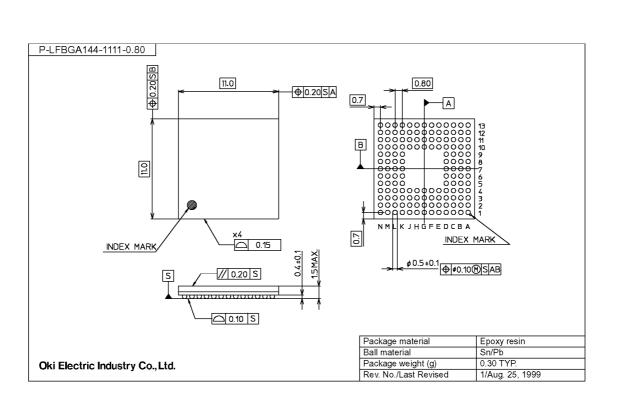

- Package

128-pin plastic TQFP (P-TQFP128-1414-0.40-K) 144-pin plastic LFBGA (P-LFBGA144-1111-0.80)

#### **BLOCK DIAGRAM**

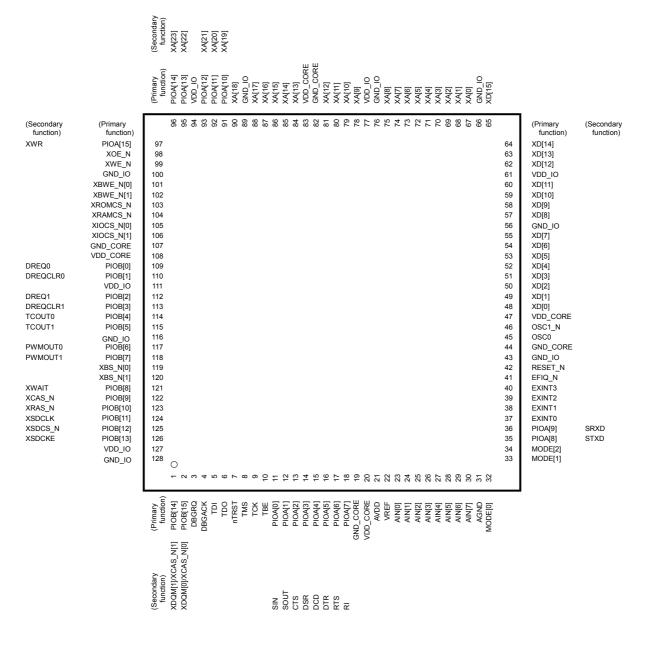

## PIN CONFIGURATION (TOP VIEW)

**128-Pin Plastic TQFP**

|    | Α                    | В                                  | С                                  | D                   | E                   | F                | G               | н            | J      | к      | L                | м            | N                | -  |

|----|----------------------|------------------------------------|------------------------------------|---------------------|---------------------|------------------|-----------------|--------------|--------|--------|------------------|--------------|------------------|----|

| 13 | NC                   | NC                                 | NC                                 | PIOA[12]/<br>XA[21] | XA[18]              | XA[16]           | GND_<br>CORE    | XA[8]        | XA[5]  | XA[2]  | GND_IO           | XD[15]       | NC               | 13 |

| 12 | PIOA[15]/<br>XWR     | PIOA[14]/<br>XA[23]                | VDD_IO                             | GND_IO              | XA[15]              | XA[14]           | XA[10]          | GND_IO       | XA[7]  | XA[4]  | XA[1]            | NC           | XD[14]           | 12 |

| 11 | XOE_N                | GND_IO                             | NC                                 | PIOA[11]/<br>XA[20] | PIOA[10]/<br>XA[19] | VDD_<br>CORE     | XA[12]          | XA[9]        | XA[3]  | XA[0]  | NC               | VDD_IO       | XD[13]           | 11 |

| 10 | XBWE_<br>N[0]        | XROM<br>CS_N                       | XWE_N                              | PIOA[13]/<br>XA[22] | XA[17]              | XA[13]           | XA[11]          | VDD_IO       | XA[6]  | XD[12] | XD[10]           | GND_IO       | XD[11]           | 10 |

| 9  | XRAM<br>CS_N         | XIOCS_<br>N[1]                     | XBWE_<br>N[1]                      | XIOCS_<br>N[0]      |                     |                  |                 |              |        | XD[7]  | XD[9]            | XD[5]        | XD[8]            | 9  |

| 8  | GND_<br>CORE         | VDD_<br>CORE                       | PIOB[1]/<br>DREQCLR<br>0           | PIOB[0]/<br>DREQ0   |                     |                  |                 |              |        | XD[3]  | XD[2]            | XD[4]        | XD[6]            | 8  |

| 7  | PIOB[4]/<br>TCOUT0   | VDD_IO                             | PIOB[3]/<br>DREQCLR<br>1           | PIOB[2]/<br>DREQ1   |                     |                  |                 |              |        | XD[0]  | XD[1]            | NC           | NC               | 7  |

| 6  | XBS_N[0]             | PIOB[6]/<br>PWMOUT0                | PIOB[5]/<br>TCOUT1                 | GND_IO              |                     |                  |                 |              |        | NC     | VDD_<br>CORE     | OSC1_N       | OSC0             | 6  |

| 5  | PIOB[9]/<br>XCAS_N   | PIOB[7]/<br>PWMOUT<br>1            | PIOB[10]/<br>XRAS_N                | XBS_N[1]            |                     |                  |                 |              |        | GND_IO | EXINT3           | GND_<br>CORE | RESET_N          | 5  |

| 4  | PIOB[12]/<br>XSDCS_N | PIOB[8]/<br>XWAIT                  | PIOB[11]/<br>XSDCLK                | VDD_IO              | тск                 | PIOA[2]/<br>CTS  | PIOA[5]/<br>DTR | VDD_<br>CORE | AIN[0] | AIN[7] | EXINT0           | EFIQ_N       | EXINT2           | 4  |

| 3  | NC                   | PIOB[13]/<br>XSDCKE                | NC                                 | DBGRQ               | TDO                 | PIOA[3]/<br>DSR  | PIOA[6]/<br>RTS | GND_<br>CORE | AIN[3] | AIN[4] | PIOA[8]/<br>STXD | EXINT1       | PIOA[9]/<br>SRXD | 3  |

| 2  | NC                   | GND_IO                             | DBGACK                             | nTRST               | TBE                 | PIOA[1]/<br>SOUT | PIOA[4]/<br>DCD | NC           | AVDD   | AIN[1] | AIN[6]           | NC           | MODE[2]          | 2  |

| 1  | NC                   | PIOB[14]/<br>XDQM[1]/<br>XCAS_N[1] | PIOB[15]/<br>XDQM[0]/<br>XCAS_N[0] | TDI                 | TMS                 | PIOA[0]/<br>SIN  | PIOA[7]/<br>RI  | VREF         | AIN[2] | AIN[5] | AGND             | MODE[0]      | MODE[1]          | 1  |

|    | Α                    | В                                  | С                                  | D                   | E                   | F                | G               | Н            | J      | к      | L                | м            | N                |    |

Note: Don't connect NC pins with others.

# 144-Pin Plastic LFBGA

# LIST OF PINS

| Pin N | umber |          |     | Primary Function                               | Secondary Function    |     |                          |

|-------|-------|----------|-----|------------------------------------------------|-----------------------|-----|--------------------------|

| TQFP  | LFBGA | Pin Name | I/O | Function                                       | Pin Name              | I/O | Function                 |

| 1     | B1    | PIOB[14] | I/O | General-purpose port (with interrupt function) | XDQM[1]/<br>XCAS_N[1] | 0   | I/O mask/CAS (MSB)       |

| 2     | C1    | PIOB[15] | I/O | General-purpose port (with interrupt function) | XDQM[0]/<br>XCAS_N[0] | 0   | I/O mask/CAS (LSB)       |

| 3     | D3    | DBGRQ    | Ι   | Debugging input signal                         | _                     | —   |                          |

| 4     | C2    | DBGACK   | 0   | Debugging output signal                        | _                     | _   |                          |

| 5     | D1    | TDI      | Ι   | JTAG data input                                | _                     | —   |                          |

| 6     | E3    | TDO      | 0   | JTAG data output                               |                       |     |                          |

| 7     | D2    | nTRST    | Т   | JTAG reset                                     | -                     |     |                          |

| 8     | E1    | TMS      | Ι   | JTAG mode select                               | _                     | _   |                          |

| 9     | E4    | ТСК      | I   | JTAG clock                                     | _                     | _   |                          |

| 10    | E2    | TBE      | Ι   | Test input signal                              | _                     | _   |                          |

| 11    | F1    | PIOA[0]  | I/O | General-purpose port (with interrupt function) | SIN                   | Ι   | UART Serial Data In      |

| 12    | F2    | PIOA[1]  | I/O | General-purpose port (with interrupt function) | SOUT                  | 0   | UART Serial Data Out     |

| 13    | F4    | PIOA[2]  | I/O | General-purpose port (with interrupt function) | CTS                   | Ι   | UART Clear To Send       |

| 14    | F3    | PIOA[3]  | I/O | General-purpose port (with interrupt function) | DSR                   | Ι   | UART Set Ready           |

| 15    | G2    | PIOA[4]  | I/O | General-purpose port (with interrupt function) | DCD                   | Ι   | UART Carrier Detect      |

| 16    | G4    | PIOA[5]  | I/O | General-purpose port (with interrupt function) | DTR                   | 0   | UART Data Terminal Ready |

| 17    | G3    | PIOA[6]  | I/O | General-purpose port (with interrupt function) | RTS                   | 0   | UART Request To Send     |

| 18    | G1    | PIOA[7]  | I/O | General-purpose port (with interrupt function) | RI                    | Ι   | UART Ring Indicator      |

| 19    | H3    | GND_CORE | GND | Core ground                                    | _                     | —   |                          |

| 20    | H4    | VDD_CORE | VDD | Core power supply                              | _                     | —   |                          |

| 21    | J2    | AVDD     | VDD | Analog-to-digital converter power supply       | _                     | —   |                          |

| 22    | H1    | VREF     | I   | Analog-to-digital converter reference voltage  |                       | —   |                          |

| 23    | J4    | AIN[0]   | I   | Analog-to-digital converter analog input       |                       | _   |                          |

| 24    | K2    | AIN[1]   | I   | Analog-to-digital converter analog input       | _                     | _   |                          |

| 25    | J1    | AIN[2]   | I   | Analog-to-digital converter analog input       | _                     | _   |                          |

| 26    | J3    | AIN[3]   | I   | Analog-to-digital converter analog input       | _                     | _   |                          |

| 27    | K3    | AIN[4]   | I   | Analog-to-digital converter analog input       | _                     | _   |                          |

| 28    | K1    | AIN[5]   | I   | Analog-to-digital converter analog input       |                       | —   |                          |

| 29    | L2    | AIN[6]   | I   | Analog-to-digital converter analog input       |                       | _   |                          |

| 30    | K4    | AIN[7]   | I   | Analog-to-digital converter analog input       | _                     | _   |                          |

| 31    | L1    | AGND     | GND | GND for A/D converter                          | _                     | —   |                          |

| 32    | M1    | MODE[0]  | I   | Mode setting                                   |                       | _   |                          |

| 33    | N1    | MODE[1]  | I   | Mode setting                                   | _                     | _   |                          |

| 34    | N2    | MODE[2]  | I   | Mode setting                                   | _                     | —   |                          |

| 35    | L3    | PIOA[8]  | I/O | General-purpose port (with interrupt function) | STXD                  | 0   | SIO transmit data output |

| 36    | N3    | PIOA[9]  | I/O | General-purpose port (with interrupt function) | SRXD                  | Ι   | SIO receive data input   |

| 37    | L4    | EXINT0   | 1   | Interrupt input                                |                       | _   |                          |

| 38    | M3    | EXINT1   | I   | Interrupt input                                |                       | _   |                          |

| 39    | N4    | EXINT2   | I   | Interrupt input                                |                       | _   |                          |

| -     |       |          | 1   |                                                |                       |     |                          |

#### FEDL674000-02

### **OKI** Semiconductor

| Pin N | umber |          |     | Primary Function        |          | Sec | ondary Function |

|-------|-------|----------|-----|-------------------------|----------|-----|-----------------|

| TQFP  | LFBGA | Pin Name | I/O | Function                | Pin Name | I/O | Function        |

| 40    | L5    | EXINT3   | Ι   | Interrupt input         | _        | _   |                 |

| 41    | M4    | EFIQ_N   | I   | FIQ input               |          | _   |                 |

| 42    | N5    | RESET_N  | I   | Reset input             |          | —   |                 |

| 43    | K5    | GND_IO   | GND | I/O ground              | _        | _   |                 |

| 44    | M5    | GND_CORE | GND | Core ground             | _        | _   |                 |

| 45    | N6    | OSC0     | Ι   | Oscillator input        | _        | —   |                 |

| 46    | M6    | OSC1_N   | 0   | Oscillator output       | _        | —   |                 |

| 47    | L6    | VDD_CORE | VDD | Core power supply       | _        | —   |                 |

| 48    | K7    | XD[0]    | I/O | External data bus       |          | _   |                 |

| 49    | L7    | XD[1]    | I/O | External data bus       |          | _   |                 |

| 50    | L8    | XD[2]    | I/O | External data bus       |          | _   |                 |

| 51    | K8    | XD[3]    | I/O | External data bus       |          | —   |                 |

| 52    | M8    | XD[4]    | I/O | External data bus       |          | _   |                 |

| 53    | M9    | XD[5]    | I/O | External data bus       |          | —   |                 |

| 54    | N8    | XD[6]    | I/O | External data bus       |          | —   |                 |

| 55    | К9    | XD[7]    | I/O | External data bus       | _        | —   |                 |

| 56    | M10   | GND_IO   | GND | I/O ground              | -        | _   |                 |

| 57    | N9    | XD[8]    | I/O | External data bus       |          | —   |                 |

| 58    | L9    | XD[9]    | I/O | External data bus       | _        | —   |                 |

| 59    | L10   | XD[10]   | I/O | External data bus       |          | —   |                 |

| 60    | N10   | XD[11]   | I/O | External data bus       |          | —   |                 |

| 61    | M11   | VDD_IO   | VDD | I/O power supply        | _        | —   |                 |

| 62    | K10   | XD[12]   | I/O | External data bus       |          | —   |                 |

| 63    | N11   | XD[13]   | I/O | External data bus       |          | —   |                 |

| 64    | N12   | XD[14]   | I/O | External data bus       |          | _   |                 |

| 65    | M13   | XD[15]   | I/O | External data bus       |          | _   |                 |

| 66    | L13   | GND_IO   | GND | I/O ground              |          | —   |                 |

| 67    | K11   | XA[0]    | 0   | External address output |          | _   |                 |

| 68    | L12   | XA[1]    | 0   | External address output | -        | —   |                 |

| 69    | K13   | XA[2]    | 0   | External address output |          | _   |                 |

| 70    | J11   | XA[3]    | 0   | External address output |          | _   |                 |

| 71    | K12   | XA[4]    | 0   | External address output |          | _   |                 |

| 72    | J13   | XA[5]    | 0   | External address output |          | —   |                 |

| 73    | J10   | XA[6]    | 0   | External address output |          | _   |                 |

| 74    | J12   | XA[7]    | 0   | External address output |          | _   |                 |

| 75    | H13   | XA[8]    | 0   | External address output |          | —   |                 |

| 76    | H12   | GND_IO   | GND | I/O ground              |          | —   |                 |

| 77    | H10   | VDD_IO   | VDD | I/O power supply        | _        | —   |                 |

| 78    | H11   | XA[9]    | 0   | External address output |          | —   |                 |

| 79    | G12   | XA[10]   | 0   | External address output |          | —   |                 |

| 80    | G10   | XA[11]   | 0   | External address output |          | _   |                 |

| 81    | G11   | XA[12]   | 0   | External address output | _        | —   |                 |

### **OKI** Semiconductor

| Pin N | umber |            |     | Primary Function                               |            | Sec | condary Function                     |

|-------|-------|------------|-----|------------------------------------------------|------------|-----|--------------------------------------|

| TQFP  | LFBGA | Pin Name   | I/O | Function                                       | Pin Name   | I/O | Function                             |

| 82    | G13   | GND_CORE   | GND | Core ground                                    |            | _   |                                      |

| 83    | F11   | VDD_CORE   | VDD | Core power supply                              |            | _   |                                      |

| 84    | F10   | XA[13]     | 0   | External address output                        |            | _   |                                      |

| 85    | F12   | XA[14]     | 0   | External address output                        | _          | —   |                                      |

| 86    | E12   | XA[15]     | 0   | External address output                        | _          | —   |                                      |

| 87    | F13   | XA[16]     | 0   | External address output                        | _          | —   |                                      |

| 88    | E10   | XA[17]     | 0   | External address output                        | _          | —   |                                      |

| 89    | D12   | GND_IO     | GND | I/O ground                                     | _          | —   |                                      |

| 90    | E13   | XA[18]     | 0   | External address output                        | _          | —   |                                      |

| 91    | E11   | PIOA[10]   | I/O | General-purpose port (with interrupt function) | XA[19]     | 0   | External address output              |

| 92    | D11   | PIOA[11]   | I/O | General-purpose port (with interrupt function) | XA[20]     | 0   | External address output              |

| 93    | D13   | PIOA[12]   | I/O | General-purpose port (with interrupt function) | XA[21]     | 0   | External address output              |

| 94    | C12   | VDD_IO     | VDD | I/O power supply                               | _          |     |                                      |

| 95    | D10   | PIOA[13]   | I/O | General-purpose port (with interrupt function) | XA[22]     | 0   | External address output              |

| 96    | B12   | PIOA[14]   | I/O | General-purpose port (with interrupt function) | XA[23]     | 0   | External address output              |

| 97    | A12   | PIOA[15]   | I/O | General-purpose port (with interrupt function) | XWR        | 0   | External bus data transfer direction |

| 98    | A11   | XOE_N      | 0   | Output enable (except SDRAM)                   |            | —   |                                      |

| 99    | C10   | XWE_N      | 0   | Write enable                                   | _          | —   |                                      |

| 100   | B11   | GND_IO     | GND | I/O ground                                     | _          |     |                                      |

| 101   | A10   | XBWE_N[0]  | 0   | Write enable (LSB)                             |            |     |                                      |

| 102   | C9    | XBWE_N[1]  | 0   | Write enable (MSB)                             |            |     |                                      |

| 103   | B10   | XROMCS_N   | 0   | External ROM chip select                       |            |     |                                      |

| 104   | A9    | XRAMCS_N   | 0   | External RAM chip select                       |            |     |                                      |

| 105   | D9    | XIOCS_N[0] | 0   | I/O bank 0 chip select                         |            |     |                                      |

| 106   | В9    | XIOCS_N[1] | 0   | I/O bank 1 chip select                         | -          | _   |                                      |

| 107   | A8    | GND_CORE   | GND | Core ground                                    |            |     |                                      |

| 108   | B8    | VDD_CORE   | VDD | Core power supply                              |            |     |                                      |

| 109   | D8    | PIOB[0]    | I/O | General-purpose port (with interrupt function) | DREQ0      | Ι   | DMA request signal (Ch 0)            |

| 110   | C8    | PIOB[1]    | I/O | General-purpose port (with interrupt function) | DREQCLR0   | 0   | DREQ clear signal (Ch 0)             |

| 111   | B7    | VDD_IO     | VDD | I/O power supply                               | -          |     |                                      |

| 112   | D7    | PIOB[2]    | I/O | General-purpose port (with interrupt function) | DREQ1      | Ι   | DMA request signal (Ch 1)            |

| 113   | C7    | PIOB[3]    | I/O | General-purpose port (with interrupt function) | DREQCLR1   | 0   | DREQ clear signal (Ch 1)             |

| 114   | A7    | PIOB[4]    | I/O | General-purpose port (with interrupt function) | TCOUT0     | 0   | DMA Termination Signal (CH 0)        |

| 115   | C6    | PIOB[5]    | I/O | General-purpose port (with interrupt function) | TCOUT1     | 0   | DMA Termination Signal (CH 1)        |

| 116   | D6    | GND_IO     | GND | I/O ground                                     | _          | _   |                                      |

| 117   | B6    | PIOB[6]    | I/O | General-purpose port (with interrupt function) | PWMOUT0    | 0   | PWM output (Ch 0)                    |

| 118   | B5    | PIOB[7]    | I/O | General-purpose port (with interrupt function) | PWMOUT1    | 0   | PWM output (Ch 1)                    |

| 119   | A6    | XBS_N[0]   | 0   | External bus byte select (LSB)                 | _          |     |                                      |

| 120   | D5    | XBS_N[1]   | 0   | External bus byte select (MSB)                 | _          | —   |                                      |

| 121   | B4    | PIOB[8]    | I/O | General-purpose port (with interrupt function) | XWAIT      | Ι   | WAIT input for IO bank 0             |

| 122   | A5    | PIOB[9]    | I/O | General-purpose port (with interrupt function) | XCAS_N     | 0   | Column address strobe (SDRAM)        |

| 123   | C5    | PIOB[10]   | I/O | General-purpose port (with interrupt function) | <br>XRAS_N | 0   | Row address strobe (SDRAM/EDO)       |

| Pin Number |       | Primary Function |     |                                                | Secondary Function |     |                      |  |

|------------|-------|------------------|-----|------------------------------------------------|--------------------|-----|----------------------|--|

| TQFP       | LFBGA | Pin Name         | I/O | Function                                       | Pin Name           | I/O | Function             |  |

| 124        | C4    | PIOB[11]         | I/O | General-purpose port (with interrupt function) | XSDCLK             | 0   | SDRAM clock          |  |

| 125        | A4    | PIOB[12]         | I/O | General-purpose port (with interrupt function) | XSDCS_N            | 0   | SDRAM chip select    |  |

| 126        | B3    | PIOB[13]         | I/O | General-purpose port (with interrupt function) | XSDCKE             | 0   | Clock enable (SDRAM) |  |

| 127        | D4    | VDD_IO           | VDD | I/O power supply                               | _                  |     |                      |  |

| 128        | B2    | GND_IO           | GND | I/O ground                                     | _                  |     |                      |  |

Note: A1, C3, H2, M2, K6, M7, N7, M12, N13, L11, C13, B13, A13, C11, A3, A2 pins of LFBGA packaged version are NC pins. These pins must be left unconnected.

# **PIN DESCRIPTION**

| Pin Name      | I/O     | Description                                                                                                                                                                                                                                                                       | Primary/<br>Secondary | Logic    |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|

| System        | •       |                                                                                                                                                                                                                                                                                   |                       |          |

| RESET_N       | Ι       | Reset input                                                                                                                                                                                                                                                                       | —                     | Negative |

| OSC0          | I       | Crystal oscillator connection or external clock input.<br>Connect a crystal oscillator (16 MHz to 33 MHz), if used, to OSC0 and<br>OSC1_N.                                                                                                                                        | _                     |          |

| OSC1_N        | 0       | Crystal oscillator connection.<br>Leave this pin unconnected if using external clock input.                                                                                                                                                                                       | —                     |          |

| TBE           | Ι       | Test pin. Drive at High level.                                                                                                                                                                                                                                                    | _                     | Negative |

| Debugging su  | pport.  |                                                                                                                                                                                                                                                                                   |                       |          |

| DBGRQ         | I       | Debugging pin. Normally connect to ground.                                                                                                                                                                                                                                        | —                     | Positive |

| DBGACK        | 0       | Debugging pin. Normally leave open.                                                                                                                                                                                                                                               | —                     | Positive |

| ТСК           | Ι       | Debugging pin. Normally connect to ground.                                                                                                                                                                                                                                        | _                     | —        |

| TMS           | Т       | Debugging pin. Normally drive at High level.                                                                                                                                                                                                                                      | —                     | Positive |

| nTRST         | Т       | Debugging pin. Normally connect to ground.                                                                                                                                                                                                                                        | —                     | Negative |

| TDI           | Ι       | Debugging pin. Normally drive at High level.                                                                                                                                                                                                                                      | —                     | Positive |

| TDO           | 0       | Debugging pin. Normally leave open.                                                                                                                                                                                                                                               | —                     | Positive |

| General-purpo | ose I/O | ports                                                                                                                                                                                                                                                                             |                       |          |

| PIOA[15:0]    | I/O     | General-purpose port.<br>Not available for use as port pins when secondary functions are in use.                                                                                                                                                                                  | Primary               | Positive |

| PIOB[15:0]    | I/O     | General-purpose port.<br>Not available for use as port pins when secondary functions are in use. Note<br>that enabling DRAM controller with MODE[2:0] inputs permanently<br>configures PIOB[15:9] for their secondary functions, making them<br>unavailable for use as port pins. | Primary               | Positive |

#### FEDL674000-02

### **OKI** Semiconductor

| Pin Name              | I/O     | Description                                                                                                                                                                                                            | Primary/<br>Secondary | Logic                 |

|-----------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|

| External Bus          | •       |                                                                                                                                                                                                                        |                       |                       |

| XA[23:19]             | 0       | Address bus to external RAM, external ROM, external I/O banks, and external DRAM. After a reset, these pins are configured for their primary function (PIOA[14:10]).                                                   | Secondary             | Positive              |

| XA[18:0]              | ο       | Address bus to external RAM, external ROM, external I/O banks, and external DRAM                                                                                                                                       | —                     | Positive              |

| XD[15:0]              | I/O     | Data bus to external RAM, external ROM, external I/O banks, and external DRAM                                                                                                                                          | _                     | Positive              |

| External bus of       | control | signals                                                                                                                                                                                                                |                       |                       |

| XROMCS_N              | 0       | ROM bank chip select                                                                                                                                                                                                   | —                     | Negative              |

| XRAMCS_N              | 0       | SRAM bank chip select                                                                                                                                                                                                  | —                     | Negative              |

| XIOCS_N[0]            | 0       | I/O bank 0 chip select                                                                                                                                                                                                 | —                     | Negative              |

| XIOCS_N[1]            | 0       | I/O bank 1 chip select                                                                                                                                                                                                 | —                     | Negative              |

| XOE_N                 | 0       | Output enable/read enable                                                                                                                                                                                              | —                     | Negative              |

| XWE_N                 | 0       | Write enable                                                                                                                                                                                                           | —                     | Negative              |

| XBS_N[1:0]            | 0       | Byte select: XBS_N[1] for MSB; XBS_N[0] for LSB                                                                                                                                                                        | —                     | Negative              |

| XBWE_N[0]             | 0       | LSB write enable                                                                                                                                                                                                       | —                     | Negative              |

| XBWE_N[1]             | 0       | MSB write enable                                                                                                                                                                                                       | —                     | Negative              |

| XWR                   | 0       | Data transfer direction for external bus, used when connecting to Motorola I/O devices. This represents the secondary function of pin PIOA[15], produced by setting bit 7 in the port control (GPCTL) register to "1." | Secondary             | _                     |

| XWAIT                 | I       | External I/O bank 0 WAIT signal.<br>This input permits access to devices slower than register settings.                                                                                                                | Secondary             | Positive              |

| External bus of       | control | signals (DRAM)                                                                                                                                                                                                         |                       |                       |

| XRAS_N                | 0       | Row address strobe. Used for both EDO DRAM and SDRAM.                                                                                                                                                                  | Secondary             | Negative              |

| XCAS_N                | 0       | Column address strobe signal (SDRAM)                                                                                                                                                                                   | Secondary             | Negative              |

| XSDCLK                | 0       | SDRAM clock (same frequency as internal system clock)                                                                                                                                                                  | Secondary             | _                     |

| XSDCKE                | 0       | Clock enable (SDRAM)                                                                                                                                                                                                   | Secondary             | _                     |

| XSDCS_N               | 0       | Chip select (SDRAM)                                                                                                                                                                                                    | Secondary             | Negative              |

| XDQM[1]/<br>XCAS_N[1] | 0       | Connected to SDRAM: DQM (MSB)<br>Connected to EDO DRAM: column address strobe signal (MSB)                                                                                                                             | Secondary             | Positive/<br>Negative |

| XDQM[0]/<br>XCAS_N[0] | 0       | Connected to SDRAM: DQM (LSB)<br>Connected to EDO DRAM: column address strobe signal (LSB)                                                                                                                             | Secondary             | Positive/<br>Negative |

#### FEDL674000-02

### **OKI** Semiconductor

| Pin Name      | I/O     | Description                                                                                                                                                                 | Primary/<br>Secondary | Logic    |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|

| DMA control s | signals |                                                                                                                                                                             |                       |          |

| DREQ0         | I       | Ch 0 DMA request signal, used when DMA controller configured for DREQ type                                                                                                  | Secondary             | Positive |

| DREQCLR0      | ο       | Ch 0 DREQ signal clear request. The DMA device responds to this output by negating DREQ.                                                                                    | Secondary             | Positive |

| TCOUTO        | 0       | Indicates to Ch 0 DMA device that last transfer has started                                                                                                                 | Secondary             | Positive |

| DREQ1         | I       | Ch 1 DMA request signal, used when DMA controller configured for DREQ type                                                                                                  | Secondary             | Positive |

| DREQCLR1      | ο       | Ch 1 DREQ signal clear request. The DMA device responds to this output by negating DREQ.                                                                                    | Secondary             | Positive |

| TCOUT1        | 0       | Indicates to Ch 1 DMA device that last transfer has started                                                                                                                 | Secondary             | Positive |

| SIO           | •       |                                                                                                                                                                             |                       |          |

| STXD          | 0       | SIO transmit signal                                                                                                                                                         | Secondary             | Positive |

| SRXD          | I       | SIO receive signal                                                                                                                                                          | Secondary             | Positive |

| UART          |         |                                                                                                                                                                             |                       | •        |

| SIN           | I       | Serial data input                                                                                                                                                           | Secondary             | Positive |

| SOUT          | 0       | Serial data output                                                                                                                                                          | Secondary             | Positive |

| CTS           | I       | Clear To Send.<br>Indicates that modem or data set is ready to transfer data.<br>Bit 4 in modem status register reflects this input.                                        | Secondary             | Negative |

| DSR           | I       | Data Set Ready.<br>Indicates that modem or data set is ready to establish a communications link<br>with UART.<br>Bit 5 in modem status register reflects this input.        | Secondary             | Negative |

| DCD           | I       | Data Carrier Detect.<br>Indicates that modem or data set has detected data carrier signal.<br>Bit 7 in modem status register reflects this input.                           | Secondary             | Negative |

| DTR           | ο       | Data Terminal Ready.<br>Indicates that UART is ready to establish a communications link with<br>modem or data set.<br>Bit 0 in modem control register controls this output. | Secondary             | Negative |

| RTS           | 0       | Request To Send.<br>Indicates that UART is ready to transfer data to modem or data set.<br>Bit 1 in modem control register controls this output.                            | Secondary             | Negative |

| RI            | I       | Ring Indicator.<br>Indicates that modem or data set has received telephone ring indicator.<br>Bit 6 in modem status register reflects this input.                           | Secondary             | Negative |

| Pin Name                             | I/O     | Description                                                                                   | Primary/<br>Secondary | Logic                 |

|--------------------------------------|---------|-----------------------------------------------------------------------------------------------|-----------------------|-----------------------|

| PWM signals                          |         |                                                                                               | ·                     |                       |

| PWMOUT0                              | 0       | Ch 0 PWM output                                                                               | Secondary             | Positive              |

| PWMOUT1                              | 0       | Ch 1 PWM output                                                                               | Secondary             | Positive              |

| Analog-to-digi                       | tal con | iverter                                                                                       |                       |                       |

| AIN[0]                               | Ι       | Ch 0 analog input                                                                             | —                     |                       |

| AIN[1]                               | Ι       | Ch 1 analog input                                                                             | —                     |                       |

| AIN[2]                               | Ι       | Ch 2 analog input                                                                             | —                     |                       |

| AIN[3]                               | Ι       | Ch 3 analog input                                                                             | —                     |                       |

| AIN[4]                               | Ι       | Ch 4 analog input                                                                             | —                     |                       |

| AIN[5]                               | Ι       | Ch 5 analog input                                                                             | —                     |                       |

| AIN[6]                               | Ι       | Ch 6 analog input                                                                             | —                     |                       |

| AIN[7]                               | Ι       | Ch 7 analog input                                                                             | —                     |                       |

| VREF                                 | Ι       | Analog-to-digital converter convert reference voltage                                         | —                     |                       |

| AVDD                                 |         | Analog-to-digital converter power supply                                                      | —                     |                       |

| AGND                                 |         | Analog-to-digital converter ground                                                            | —                     |                       |

| Interrupt signa                      | als     |                                                                                               |                       |                       |

| EXINT3<br>EXINT2<br>EXINT1<br>EXINT0 | I       | External interrupt input signals                                                              | _                     | Positive/<br>Negative |

| EFIQ_N                               | I       | External fast interrupt input signal.<br>Interrupt controller connects this to CPU FIQ input. | _                     | Negative              |

| MODE                                 |         |                                                                                               |                       |                       |

| MODE[2:0]                            | I       | Operating mode control signals                                                                | —                     |                       |

| Power supplie                        | s       |                                                                                               |                       |                       |

| VDD_CORE                             | _       | Core power supply                                                                             | _                     |                       |

| VDD_IO                               |         | I/O power supply                                                                              | _                     |                       |

| GND_CORE                             | _       | Core ground                                                                                   | _                     |                       |

| GND_IO                               | _       | I/O ground                                                                                    | _                     |                       |

#### **DESCRIPTION OF FUNCTIONS**

| CPU                      |                                                                                     |

|--------------------------|-------------------------------------------------------------------------------------|

| CPU core:                | ARM7TDMI                                                                            |

| Operating frequency:     | 1 MHz to 33 MHz                                                                     |

| Instructions:            | ARM instruction (32-bit length) and Thumb instruction (16-bit length) can be mixed. |

| General register bank:   | $31 \times 32$ bits                                                                 |

| Built-in barrel shifter: | ALU and barrel shift operations can be executed by one instruction.                 |

| Multiplier:              | 32 bits × 8 bits (Modified Booth's Algorithm)                                       |

| Built-in debug function: | JTAG interface, break point register                                                |

| -                        |                                                                                     |

#### **Built-in Memory**

RAM:

8 KB (2K × 32 bits) Connected to processor bus (read: 1 cycle access, write: 2 cycle access)

#### **Interrupt Controller**

Fast interrupt input (FIQ) and interrupt input (IRQ) are employed as interrupt input signals of ARM core. The interrupt controller controls these interrupt signals going to ARM core.

- (1) Interrupt sources of ML674000

FIQ: 1 source, external source (external pin: EFIQ\_N)

IRQ: 23 sources, internal sources : 19, external sources : 4 (external pins: EXINT[3:0])

- (2) Interrupt priority levelPriority can be set in 8 levels for each source.

- (3) External interrupt pin input Level sense: Interrupt signal level is selected. Edge sense: Rise or fall is selected.

- (4) External fast interrupt pin input Edge sense: Fall edge is detected.

#### Timer

7 channels of 16-bit reload timers are employed. Of these, 1 channel is used as system timer for OS. The timers of other 6 channels are used in application software.

- (1) System timer: 1 channel

16-bit auto reload timer: Used as system timer for OS (This timer is incorporated in µPLAT-7B.)

Interval mode

- (2) Application timer: 6 channels 16-bit auto reload timer One shot, interval mode Clock can be set for each channel

#### WDT

This MCU contains a Watch Dog Timer that can also function as an interval timer.

- (1) 16-bit timer

- (2) Watch dog timer or interval timer mode can be selected

- (3) Interrupt or reset generation

- Watchdog timer mode: generates reset or interrupt when the timer is overflows.Interval timer mode: generates interrupt when the timer reaches an overflow condition.

- (4) Maximum period: 200 msec or longer

#### PWM

This MCU contains two PWM (Pulse Width Modulation) channels which can change duty cycle within a certain fixed period. The PWM output resolution is 16 bits for each channel.

#### **Serial Interface**

This LSI contains two channels of serial interface.

- UART without FIFO: 1 channel This serial interface is incorporated in μPLAT-7B.

- (2) UART with 16-byte FIFO: 1 channel This is ACE (Asynchronous Communication Element) equivalent in function to 16550A. It has 16-byte FIFO in both sending and receiving.

#### **GPIO**

This LSI contains two 16-bit parallel ports.

- (1) Input or output can be selected for each bit.

- (2) Interrupt can be used for all 16 bits of each channel, and all GPIO pins can be used as interrupt inputs.

- (3) Interrupt mask and interrupt mode (level) can be set for all bits.

- (4) Configured as inputs immediately after reset.

#### **AD** Converter

This is a successive approximation type AD converter.

- (1) 10 bits  $\times$  8 channels

- (2) Sample and hold function

- (3) Scan mode and select mode are supported

- (4) Interrupt is generated after completion of conversion.

- (5) Minimum conversion time of  $5 \,\mu s$ .

#### DMAC

This MCU contains a two channel direct memory access controller which transfers data between memory and memory, between I/O and memory and between I/O and I/O.

- (1) Number of channels: 2 channels

- (2) Channel priority level: Fixed mode

Channel priority level is always fixed (channel 0 > 1).

#### Roundrobin

Priority level of the channel requested for transfer is kept lowest.

- (3) Maximum number of transfers: 65,536 times (64K times)

- (4) Data transfer size: Byte (8 bits), half-word (16 bits), word (32 bits)

- (5) Bus request system: Cycle steal mode

Bus request signal is asserted for each DMA transfer cycle.

- Burst mode

- Bus request signal is asserted until all transfers of transfer cycles are complete.

(6) DMA transfer request: Software request

- By setting the software transfer request bit inside DMAC, the CPU starts DMA transfer.

- External request

DMA transfer is started by external request allocated to each channel.

- (7) Interrupt request: Interrupt request is generated in CPU after the end of DMA transfers for the set number of transfer cycles or after occurrence of error.

- Interrupt request signal is output separately for each channel.

Interrupt request signal output can be masked for each channel.

#### **External Memory Controller**

Controls access of externally connected devices such as ROM (FLASH), SRAM, SDRAM (EDO DRAM) and IO devices.

- ROM (FLASH) access function Supports 16-bit device Supports FLASH memory: Byte write (can be written only by IF equivalent to SRAM). Access timing setting

- (2) SRAM access function Supports 16-bit device Supports asynchronous SRAM Access timing setting

- (3) DRAM access function Supports 16-bit device Supports EDO/SDRAM: Simultaneous connections to EDO-DRAM and SDRAM cannot be made.

Access timing setting

- (4) External IO access function Supports 8-bit/16-bit device Supports 2 banks independently Supports external wait input: XWAIT (IO bank 0 only) Access timing setting (for each bank)

#### **Power Management**

HALT and STANDBY functions are supported as power save functions.

- (1) HALT mode HALT object CPU, internal RAM, AHB bus control HALT mode setting: Set by the system control register. HALT mode cancelling: Reset, interrupt

- (2) STANDBY mode

Stops the clock of entire LSI.

STANDBY mode setting: Specified by the system control register.

STANDBY mode cancelling: Reset, external interrupt (other than FIQ)

# ABSOLUTE MAXIMUM RATINGS

| Item                                | Symbol                       | Conditions               | Rating                                                                 | Unit |  |

|-------------------------------------|------------------------------|--------------------------|------------------------------------------------------------------------|------|--|

| Digital power supply voltage (core) | $V_{DD_{CORE}}$              |                          | -0.3 to +3.6                                                           |      |  |

| Digital power supply voltage (I/O)  | V <sub>DD_IO</sub>           |                          | -0.3 to +4.6                                                           |      |  |

| Input voltage                       | VI                           |                          | –0.3 to V <sub>DD_IO</sub> +0.3                                        |      |  |

| Output voltage                      | Vo                           |                          | –0.3 to V <sub>DD_IO</sub> +0.3                                        | V    |  |

| Analog power supply voltage         | $AV_{DD}$                    | GND = AGND = 0 V         | -0.3 to V <sub>DD_IO</sub> +0.3                                        |      |  |

| Analog reference voltage            | $V_{REF}$                    | Ta = 25°C                | $-0.3$ to V <sub>DD_IO</sub> +0.3 and<br>-0.3 to AV <sub>DD</sub> +0.3 |      |  |

| Analog input voltage                | V <sub>AI</sub>              |                          | –0.3 to V <sub>REF</sub>                                               |      |  |

| Input current                       | lı                           |                          | -10 to +10                                                             |      |  |

| High level output current           | I <sub>OH</sub>              |                          | +10                                                                    | m (  |  |

| Low level output current *1         |                              |                          | -20                                                                    | mA   |  |

| Low level output current *2         | I <sub>OL</sub>              |                          | -30                                                                    |      |  |

| Power dissipation                   | P <sub>D</sub>               | Ta = 85°C<br>per package | 530                                                                    | mW   |  |

| Storage temperature                 | temperature T <sub>STG</sub> |                          | -50 to +150                                                            | °C   |  |

#### Notes

1. All output pins except XA[15:0]

2. XA[15:0]

# **RECOMMENDED OPERATING CONDITIONS**

|                                       |                    |                                                                          |         |         | (GN     | D = 0 V) |

|---------------------------------------|--------------------|--------------------------------------------------------------------------|---------|---------|---------|----------|

| ltem                                  | Symbol             | Conditions                                                               | Minimum | Typical | Maximum | Unit     |

| Digital power supply voltage (core)   | $V_{DD\_CORE}$     |                                                                          | 2.25    | 2.5     | 2.75    |          |

| Digital power supply voltage<br>(I/O) | V <sub>DD_IO</sub> | Vdd_io≥Vdd_core                                                          | 3.0     | 3.3     | 3.6     | V        |

| Analog power supply voltage           | $AV_{DD}$          | $A_{VDD} = V_{DD_{IO}}$                                                  | 3.0     | 3.3     | 3.6     |          |

| Analog reference voltage              | $V_{REF}$          | $V_{REF} = A_{VDD} = V_{DD_{IO}}$                                        | 3.0     | 3.3     | 3.6     |          |

| Storage hold voltage                  | V <sub>DDH</sub>   | f <sub>osc</sub> = 0 Hz                                                  | 2.25    | _       | 3.6     |          |

| Operating frequency                   | f <sub>osc</sub>   | V <sub>DD_CORE</sub> = 2.25 to 2.75<br>V <sub>DD_IO</sub> = 3.0 to 3.6 * | 1       | _       | 33.333  | MHz      |

| Ambient temperature                   | Та                 | —                                                                        | -40     | 25      | +85     | °C       |

Note

Oscillator frequencies between 16 MHz and 33 MHz. Minimum of 2.56 MHz for external SDRAM. Minimum of 6.4 MHz for external EDO DRAM. Minimum of 2 MHz for analog-to-digital converter.

# **ELECTRICAL CHARACTERISTICS**

# **DC Characteristics**

| Item                                      | Symbol                           | Conditions                                             | Minimum              | Typical | Maximum                 | Unit |  |

|-------------------------------------------|----------------------------------|--------------------------------------------------------|----------------------|---------|-------------------------|------|--|

| High level input voltage                  | V <sub>IH</sub>                  |                                                        | 2.0                  |         | V <sub>DD_IO</sub> +0.3 |      |  |

| Low level input voltage                   | VIL                              |                                                        | -0.3                 |         | 0.8                     |      |  |

| Schmitt input buffer threshold voltage    | $V_{T+}$                         | —                                                      | _                    | 1.6     | 2.1                     |      |  |

|                                           | V <sub>T</sub> -                 |                                                        | 0.7                  | 1.1     | —                       |      |  |

| inconoid voltage                          | V <sub>HYS</sub>                 |                                                        | 0.4                  | 0.5     | —                       |      |  |

|                                           | V                                | I <sub>OH</sub> = –100 μA                              | V <sub>DD</sub> -0.2 | _       | —                       | V    |  |

| High level output voltage                 | V <sub>OH</sub>                  | I <sub>OH</sub> = -4 mA                                | 2.4                  |         | —                       |      |  |

| Low level output voltage                  |                                  | I <sub>OL</sub> = 100 μA                               | —                    | _       | 0.2                     |      |  |

| Low level output voltage *1               | V <sub>OL</sub>                  | I <sub>OL</sub> = 4 mA                                 | —                    | _       | 0.4                     |      |  |

| Low level output voltage *2               |                                  | I <sub>OL</sub> = 6 mA                                 | _                    | _       | 0.4                     |      |  |

| Input leak current *3                     |                                  | $V_{I} = 0 V/V_{DD_{IO}}$                              | -10                  | _       | 10                      | μΑ   |  |

| Input leak current *4                     | I <sub>IH</sub> /I <sub>IL</sub> | V <sub>I</sub> = 0 V<br>Pull-up resistance of<br>50 kΩ | 10                   | 66      | 200                     |      |  |

| Output leak current                       | I <sub>LO</sub>                  | $V_{O} = 0 V/V_{DD_{IO}}$                              | -10                  | _       | 10                      |      |  |

| Input pin capacitance                     | Cı                               | _                                                      |                      | 6       | _                       | pF   |  |

| Output pin capacitance                    | Co                               | —                                                      | _                    | 9       | _                       |      |  |

| I/O pin capacitance                       | C <sub>IO</sub>                  | —                                                      | _                    | 10      | _                       | 1    |  |

| Analog reference power supply current     | I <sub>REF</sub>                 | Analog-to-digital converter operative *5               | _                    | 320     | 650                     | μA   |  |

|                                           |                                  | Analog-to-digital<br>converter stopped                 | _                    | 1       | 2                       |      |  |

| Current consumption<br>(STANDBY)          | I <sub>DDS_CORE</sub>            | Ta = 25°C * <sup>6</sup>                               | _                    | 3       | 45                      | μΑ   |  |

|                                           | I <sub>DDS_IO</sub>              | Ta = 25 C                                              | _                    | 1       | 5                       |      |  |

| Current consumption (HALT) * <sup>7</sup> | IDDH_CORE                        |                                                        | _                    | 8       | 15                      | mA   |  |

|                                           | I <sub>DDH_IO</sub>              | f <sub>osc</sub> = 16 MHz                              | _                    | 2       | 5                       |      |  |

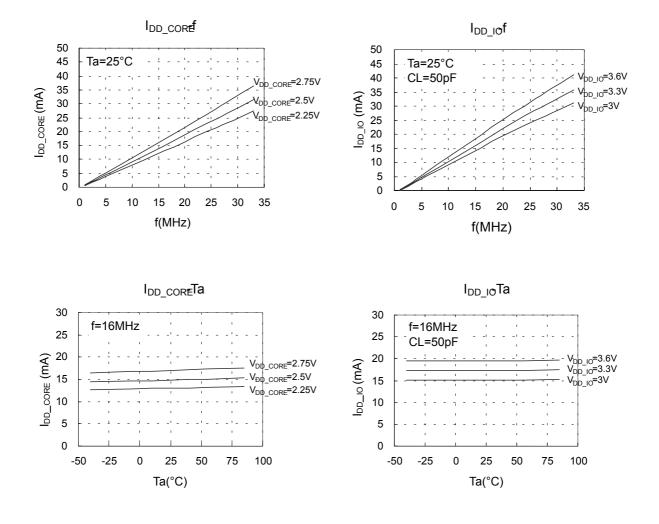

| Current consumption (RUN)                 | I <sub>DD_CORE</sub>             | C <sub>L</sub> = 50 pF                                 | _                    | 15      | 25                      | mA   |  |

|                                           | I <sub>DD_IO</sub>               |                                                        | _                    | 18      | 30                      |      |  |

### Notes

1. All output pins except XA[15:0]

2. XA[15:0]

- 3. All input pins except  $RESET_N$

- 4. RESET\_N pin, with 50 k $\Omega$  pull-up resistance

- 5. Analog-Digital Converter operation ratio is 20%

- 6.  $V_{DD\_IO}$  or 0 V for input ports; no load for other pins

- 7. DRAM function stop by MODE pin setting

#### **Power Consumption**

The values in the following charts are measured values in the operating conditions indicated. The samples were taken during normal operation in ARM mode with all peripheral clocks activated. Instructions were being executed from external memory.

| 0 0                          |                   | (V <sub>DD_CORE</sub> = 2.50 V, V <sub>DD_IO</sub> = 3.3 V, Ta = 25°C |         |         |         | , Ta = 25°C) |  |

|------------------------------|-------------------|-----------------------------------------------------------------------|---------|---------|---------|--------------|--|

| Item                         | Symbol            | Conditions                                                            | Minimum | Typical | Maximum | Unit         |  |

| Resolution                   | n                 | —                                                                     |         | _       | 10      | bit          |  |

| Linearity error              | EL                | A                                                                     | -       | ±3      | —       | LSB          |  |

| Differential linearity error | ED                | Analog input source impedance                                         |         | ±3      | _       |              |  |

| Zero scale error             | Ezs               | Ri ≤ 1kΩ                                                              |         | ±3      | _       |              |  |

| Full scale error             | E <sub>FS</sub>   |                                                                       | -       | ±3      | —       |              |  |

| Conversion time              | t <sub>CONV</sub> | —                                                                     | 5       | _       | —       | μS           |  |

| Throughput                   |                   | _                                                                     | 10      |         | 200     | kHz          |  |

#### **Analog-to-Digital Converter Characteristics**

Note: VDD\_IO and AVDD should be supplied separately.

- · Definition of Terms

- (1) Resolution: Minimum input analog value recognized. For 10-bit resolution, this is (VREF Aground) ÷ 1024.

- (2) Linearity error: Difference between the theoretical and actual conversion characteristics. (Note that it does not include quantization error.) The theoretical conversion characteristic divides the voltage range between VREF and AGND into 1024 equal steps.

- (3) Differential linearity error: Difference between the theoretical and actual input voltage change producing a 1-bit change in the digital output anywhere within the conversion range. This is an indicator of conversion characteristic smoothness. The theoretical value is (VREF - Aground) ÷ 1024.

- (4) Zero scale error: Difference between the theoretical and actual conversion characteristics at the point where the digital output switches from "0x000" to "0x001."

- (5) Full scale error: Difference between the theoretical and actual conversion characteristics at the point where the digital output switches from "0x3FE" to "0x3FF."

# PACKAGE DIMENSIONS

(Unit : mm)

#### **OKI** Semiconductor

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

| Document<br>No. | Date          | Page<br>Previous Current<br>Edition Edition |          | Description                                                                                                     |  |

|-----------------|---------------|---------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------|--|

| PEDL674000-01   | Oct., 2001    | Edition<br>–                                | Edition  | Preliminary edition 1                                                                                           |  |

| PEDL674000-02   | May 17, 2002  | _                                           | _        | Preliminary edition 2                                                                                           |  |

|                 |               | 1                                           | 1        | Feature Table rewritten.                                                                                        |  |

|                 |               | 2-13                                        | 2-12     | Pin names are changed.                                                                                          |  |

|                 |               | 14-16                                       | 13-15    | Description rewritten.                                                                                          |  |

|                 |               | 17                                          | 16-37    | Electrical characteristics added.                                                                               |  |

| FEDL674000-01   | Aug. 8, 2002  | _                                           | _        | Final edition 1                                                                                                 |  |

|                 |               | 1                                           | 1        | Number of interrupt sources corrected.                                                                          |  |

|                 |               | 8                                           | 8        | TBE signal description corrected.                                                                               |  |

|                 |               | 8                                           | 8        | Pin numbers of XA[23:19] and XA[18:0] corrected.                                                                |  |

|                 |               | 15-36                                       | 15-50    | Description rewritten.                                                                                          |  |

| FEDL674000-02   | Dec. 10, 2002 | _                                           | _        | Final edition 2                                                                                                 |  |

|                 |               | 1                                           | 1 to 2   | Description changed.<br>Supported DRAM area changed from 16Mbytes<br>to 64Mbytes.<br>Add 144-pin LFBGA package. |  |

|                 |               | _                                           | 5        | Add Pin layout for LFBGA package.                                                                               |  |

|                 |               | 4 to 7                                      | 6 to 9   | Change table of pin list.<br>(Add LFBGA description and correct some misdescription.)                           |  |

|                 |               | 8 to 11                                     | 10 to 13 | Change table of pin description.<br>(Correct some misdescription.)                                              |  |

|                 |               | 12 to 14                                    | 14 to 16 | Description changed.                                                                                            |  |

|                 |               | 18 to 50                                    | _        | Description of AC characteristics Deleted.<br>Please refer to User's Manual.                                    |  |

|                 |               | 51                                          | 21       | The values of Zero scale error and Full scale error of Analog-to-Digital converter are corrected.               |  |

|                 |               | _                                           | 23       | Add Package Dimensions for LFBGA package.                                                                       |  |

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.