## Electrical Characteristics Over the Operating Range [3]

| Parameter        | Description                              | Test Conditions                                                                                                       | 7B136-15<br>7B146-15 |      | 7B136-20<br>7B146-20 |      | Unit |    |

|------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|------|------|----|

|                  |                                          |                                                                                                                       |                      | Min. | Max.                 | Min. | Max. |    |

| V <sub>OH</sub>  | Output HIGH Voltage                      | $V_{CC} = Min., I_{OH} = -4.0 \text{ mA}$                                                                             |                      | 2.4  |                      | 2.4  |      | V  |

| $V_{OL}$         | Output LOW Voltage                       | I <sub>OL</sub> = 4.0 mA                                                                                              |                      |      | 0.4                  |      | 0.4  | ٧  |

|                  |                                          | I <sub>OL</sub> = 16.0 mA <sup>[4]</sup>                                                                              |                      |      | 0.5                  |      | 0.5  |    |

| V <sub>IH</sub>  | Input HIGH Voltage                       |                                                                                                                       |                      | 2.2  |                      | 2.2  |      | V  |

| $V_{\rm IL}$     | Input LOW Voltage                        |                                                                                                                       |                      |      | 8.0                  |      | 0.8  | ٧  |

| I <sub>IX</sub>  | Input Load Current                       | $GND \le V_1 \le V_{CC}$                                                                                              |                      | -10  | +10                  | -10  | +10  | μА |

| l <sub>OZ</sub>  | Output Leakage<br>Current                | $GND \le V_O \le V_{CC}$ , Output Disabled                                                                            |                      | -10  | +10                  | -10  | +10  | μА |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating                | CE = V <sub>II</sub> Outputs Open,<br>f = f <sub>MAX</sub> <sup>[5]</sup>                                             | Com'l                |      | 260                  |      | 240  | mA |

| Supply Current   | Supply Current                           | $f = f_{MAX}^{[D]}$                                                                                                   | Ind                  |      |                      |      | 300  |    |

| I <sub>SB1</sub> | Standby Current Both Ports,              | CE <sub>L</sub> and CE <sub>R ≥</sub> V <sub>IH</sub> ,                                                               | Com'l                |      | 110                  |      | 100  | mA |

|                  | TTL Inputs                               | $f = f_{MAX}^{[5]}$                                                                                                   | Ind                  |      |                      |      | 105  | 1  |

| I <sub>SB2</sub> | Standby Current One Port,                | CE <sub>L</sub> or CE <sub>R</sub> ≥ V <sub>IH</sub> ,                                                                | Com'l                |      | 165                  |      | 155  | mA |

|                  | TTL Inputs                               | Active Port Outputs Open,<br>f = f <sub>MAX</sub> <sup>[5]</sup>                                                      | Ind                  |      |                      |      | 180  |    |

| I <sub>SB3</sub> | Standby Current Both Ports, CMOS Inputs  | Both Ports $\overline{CE}_L$ and $\overline{CE}_{R \ge V_{CC}} = 0.2V$ ,                                              | Com'l                |      | 15                   |      | 15   | mA |

|                  |                                          | $V_{IN} \ge V_{CC} - 0.2V \text{ or } V_{IN} \le 0.2V, f = 0$                                                         | Ind                  |      |                      |      | 30   | 1  |

| I <sub>SB4</sub> | Standby Current One Port,<br>CMOS Inputs | One Port $\overline{CE}_L$ or $\overline{CE}_R \ge V_{CC} - 0.2V$ , $V_{IN} \ge V_{CC} - 0.2V$ or $V_{IN} \le 0.2V$ , | Com'l                |      | 160                  |      | 150  | mA |

|                  |                                          | Active Port Outputs Open,<br>$f = f_{MAX}^{[5]}$                                                                      | Ind                  |      |                      |      | 170  | 1  |

#### Notes:

See the last page of this specification for Group A subgroup testing information.

BUSY and INT pins only.

At f=f<sub>MAX</sub>, address and data inputs are cycling at the maximum frequency of read cycle of 1/t<sub>rc</sub> and using AC Test Waveforms input levels of GND to 3V.

# Capacitance<sup>[6]</sup>

| Parameter        | Description        | Test Conditions                                             | Max. | Unit |

|------------------|--------------------|-------------------------------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz}, $<br>$V_{CC} = 5.0V$ | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | 100                                                         | 10   | pF   |

#### Notes:

6. Tested initially and after any design or process changes that may affect these parameters.

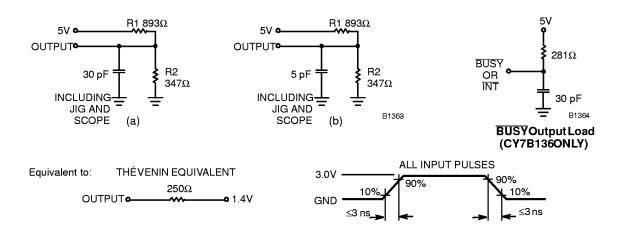

#### **AC Test Loads and Waveforms**

### Switching Characteristics Over the Operating Range [3, 7]

|                   |                                      | 7B136-15<br>7B146-15 |      | 7B136-20<br>7B146-20 |      |      |

|-------------------|--------------------------------------|----------------------|------|----------------------|------|------|

| Parameter         | Description                          | Min.                 | Max. | Min.                 | Max. | Unit |

| READ CYCLE        | •                                    | •                    | •    | •                    | •    | •    |

| t <sub>RC</sub>   | Read Cycle Time                      | 15                   |      | 20                   |      | ns   |

| t <sub>AA</sub>   | Address to Data Valid <sup>[8]</sup> |                      | 15   |                      | 20   | ns   |

| t <sub>oha</sub>  | Data Hold from Address Change        | 3                    |      | 3                    |      | ns   |

| t <sub>ACE</sub>  | CE LOW to Data Valid <sup>[8]</sup>  |                      | 15   |                      | 20   | ns   |

| DOE               | OE LOW to Data Valid <sup>[8]</sup>  |                      | 10   |                      | 13   | ns   |

| t <sub>LZOE</sub> | OE LOW to Low Z <sup>[9]</sup>       | 3                    |      | 3                    |      | ns   |

| HZOE              | OE HIGH to High Z <sup>[9,10]</sup>  |                      | 10   |                      | 13   | ns   |

| t <sub>LZCE</sub> | CE LOW to Low Z <sup>[9]</sup>       | 3                    |      | 3                    |      | ns   |

| t <sub>HZCE</sub> | CE HIGH to High Z <sup>[9,10]</sup>  |                      | 10   |                      | 13   | ns   |

| t <sub>PU</sub>   | CE LOW to Power-Up                   | 0                    |      | 0                    |      | ns   |

| t <sub>PD</sub>   | CE HIGH to Power-Down                |                      | 15   |                      | 20   | ns   |

| WRITE CYCLE       | 1] '                                 | •                    |      |                      |      |      |

| t <sub>wc</sub>   | Write Cycle Time                     | 15                   |      | 20                   |      | ns   |

| tsce              | CE LOW to Write End                  | 12                   |      | 15                   |      | ns   |

| t <sub>AW</sub>   | Address Set-Up to Write End          | 12                   |      | 15                   |      | ns   |

| t <sub>HA</sub>   | Address Hold from Write End          | 2                    |      | 2                    |      | ns   |

| SA                | Address Set-Up to Write Start        | 0                    |      | 0                    |      | ns   |

| t <sub>PWE</sub>  | R/W Pulse Width                      | 12                   |      | 15                   |      | ns   |

| t <sub>SD</sub>   | Data Set-Up to Write End             | 10                   |      | 13                   |      | ns   |

#### Notes:

- Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading of the specified I<sub>OL</sub>/I<sub>OH,</sub> and 30-pF load capacitance. 7.

- AC test conditions use  $V_{OH} = 1.6V$  and  $V_{OL} = 1.4V$ .

- 9. At any given temperature and voltage condition for any given device, t<sub>HZCE</sub> is less than t<sub>LZCE</sub> and t<sub>HZCE</sub> is less than t<sub>LZCE</sub>.

- $t_{LZCE}$ ,  $t_{LZNE}$ ,  $t_{LZOE}$ ,  $t_{LZOE}$ , and  $t_{HZNE}$  are tested with  $C_L = 5pF$  as in part (b) of AC Test Loads. Transition is measured  $\pm \pm 500$  mV from steady-state voltage.

- The internal write time of the memory is defined by the overlap of CE LOW and RW LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write. These parameters are measured from the input signal changing, until the output pin goes to a high-impedance state. CY7B146 only.

For information on port-to-port delay through RAM cells, from writing port to reading port, refer to the Read Timing with Port-to-Port Delay timing diagram.

## $\textbf{Switching Characteristics} \ \, \text{Over the Operating Range}^{[3,\,7]} \ \, \text{(Continued)}$

|                      |                                                     |      | 36-15<br>46-15 |      | 36-20<br>46-20 |      |

|----------------------|-----------------------------------------------------|------|----------------|------|----------------|------|

| Parameter            | Description                                         | Min. | Max.           | Min. | Max.           | Unit |

| t <sub>HD</sub>      | Data Hold from Write End                            | 0    |                | 0    |                | ns   |

| t <sub>HZWE</sub>    | R/W LOW to High Z                                   |      | 10             |      | 13             | ns   |

| t <sub>LZWE</sub>    | R/W HIGH to Low Z                                   | 3    |                | 3    |                | ns   |

| BUSY/INTERRUP        | T TIMING                                            | •    | •              |      | •              | •    |

| t <sub>BLA</sub>     | BUSY LOW from Address Match                         |      | 15             |      | 20             | ns   |

| t <sub>BHA</sub>     | BUSY HIGH from Address Mismatch <sup>[12]</sup>     |      | 15             |      | 20             | ns   |

| t <sub>BLC</sub>     | BUSY LOW from CE LOW                                |      | 15             |      | 20             | ns   |

| t <sub>BHC</sub>     | BUSY HIGH from CE HIGH[12]                          |      | 15             |      | 20             | ns   |

| t <sub>PS</sub>      | Port Set Up for Priority                            | 5    |                | 5    |                | ns   |

| t <sub>WB</sub> [13] | R/W LOW after BUSY LOW                              | 0    |                | 0    |                | ns   |

| t <sub>WH</sub>      | R/W HIGH after BUSY HIGH                            | 13   |                | 20   |                | ns   |

| t <sub>BDD</sub>     | BUSY HIGH to Valid Data                             |      | 15             |      | 20             | ns   |

| t <sub>DDD</sub>     | Write Data Valid to Read Data Valid <sup>[14]</sup> |      | 25             |      | 30             | ns   |

| t <sub>WDD</sub>     | Write Pulse to Data Delay[14]]                      |      | 30             |      | 40             | ns   |

| INTERRUPT TIMI       | NG                                                  | •    | •              | •    | •              | •    |

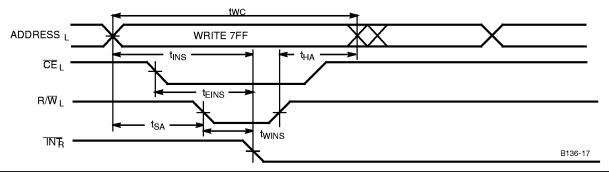

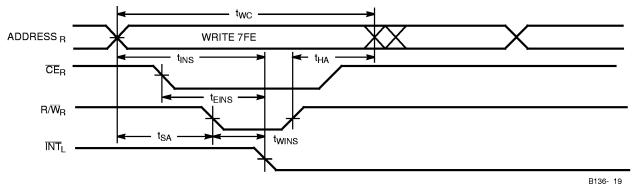

| t <sub>WINS</sub>    | R/W to INTERRUPT Set Time                           |      | 15             |      | 20             | ns   |

| t <sub>EINS</sub>    | CE to INTERRUPT Set Time                            |      | 15             |      | 20             | ns   |

| t <sub>INS</sub>     | Address to INTERRUPT Set Time                       |      | 15             |      | 20             | ns   |

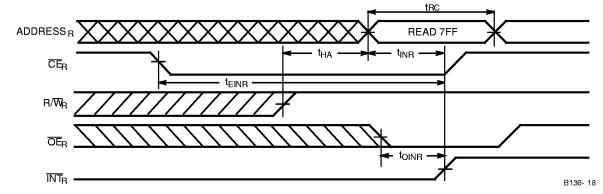

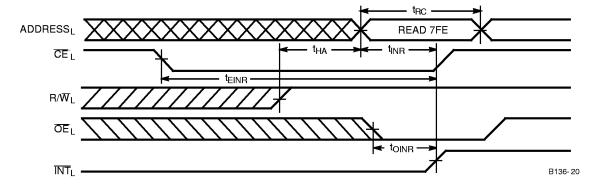

| t <sub>OINR</sub>    | OE to INTERRUPT Reset Time <sup>[12]</sup>          |      | 15             |      | 20             | ns   |

| t <sub>EINR</sub>    | CE to INTERRUPT Reset Time <sup>[12]</sup>          |      | 15             |      | 20             | ns   |

| t <sub>INR</sub>     | Address to INTERRUPT Reset Time[[†2]                |      | 15             |      | 20             | ns   |

#### Notes:

- Notes:

Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V and output loading of the specified loL/loH, and 30-pF load capacitance.

AC test conditions use VoH = 1.6V and VoL = 1.4V.

At any given temperature and voltage condition for any given device, t<sub>HZCE</sub> is less than t<sub>LZCE</sub> and t<sub>HZOE</sub> is less than t<sub>LZCE</sub>.

t<sub>LZCE</sub>, t<sub>LZWE</sub>, t<sub>HZOE</sub>, t<sub>HZOE</sub>, t<sub>HZCE</sub>, and t<sub>HZWE</sub> are tested with C<sub>L</sub> = 5pF as in part (b) of AC Test Loads. Transition is measured ±±500 mV from steady-state voltage.

The internal write time of the memory is defined by the overlap of CE LOW and RW LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write.

These parameters are measured from the input signal changing, until the output pin goes to a high-impedance state.

CY7B146 only.

For information on port-to-port delay through RAM cells, from writing port to reading port, refer to the Read Timing with Port-to-Port Delay timing diagram.

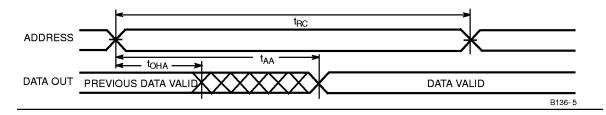

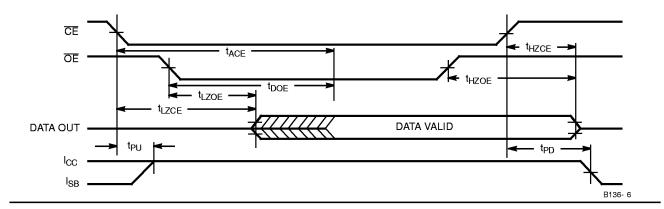

## **Switching Waveforms**

Read Cycle No. 1 (Either Port-Address Access) [15,16]

Read Cycle No. 2 (Either Port-CE/OE) [15,17]

#### Notes:

- R/W is HIGH for read cycle.

Device is continuously selected, CE = V<sub>IL</sub> and OE = V<sub>IL</sub>.

Address valid prior to or coincident with CE transition LOW.

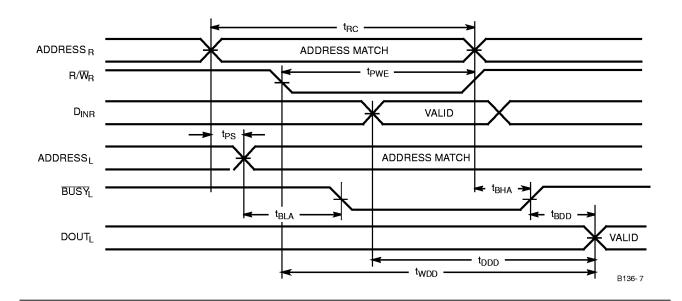

#### Read Cycle No.3 (Read with BUSY Master: CY7B136)

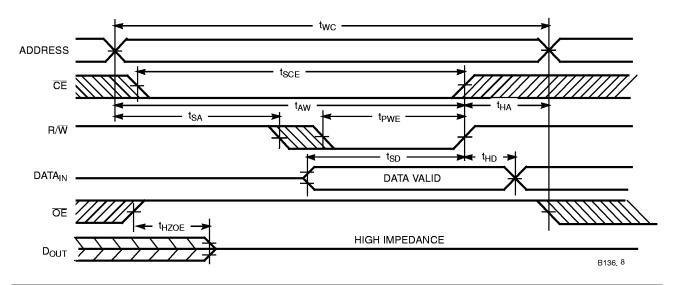

Write Cycle No. 1(OE Three-States Data I/Os-Either Port)[11,18]

#### Notes:

If OE is LOW during a RW controlled write cycle, the write pulse width must be the larger of t<sub>PWE</sub> or t<sub>HZWE</sub> + t<sub>SD</sub> to allow the data I/O pins to enter high impedance and for data to be placed on the bus for the required t<sub>SD</sub>.

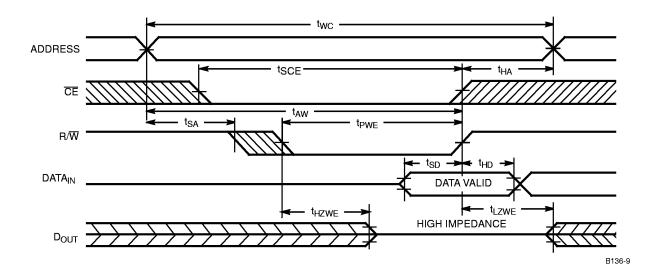

# Write Cycle No. 2 (R $\overline{\text{/W}}$ Three-States Data I/Os — Either Port) $^{[11,\ 19]}$

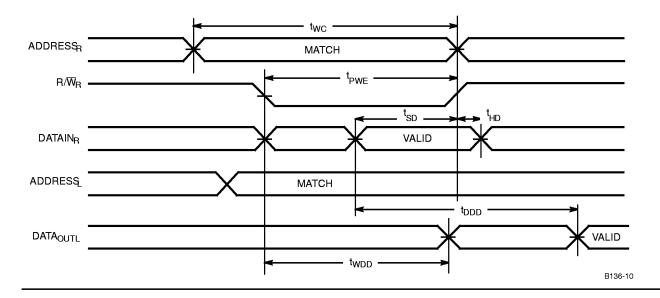

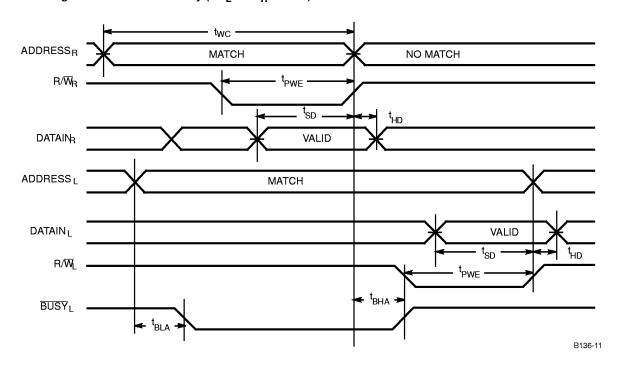

## Read Timing with Port-to-Port Delay ( $\overline{CE}_L = \overline{CE}_R = LOW$ , $\overline{BUSY} = HIGH$ for the Writing Port)

#### Notes:

19. If the  $\overline{\text{CE}}$  LOW transition occurs simultaneously with or after the  $\overline{\text{RW}}$  LOW transition, the outputs remain in a high-impedance state.

## Write Timing with Port–to–Port Delay ( $\overline{CE}_L + \overline{CE}_R = LOW$ )

## Busy Timing Diagram No. 1 (CE Arbitration)

# CE<sub>L</sub> Valid First: $\mathsf{ADDRESS}_{\mathsf{L},\mathsf{R}}$ ADDRESS MATCH CEL . < tps → CER . ← t<sub>BHC</sub> t<sub>BLC</sub> BUSY R B136- 12 $\overline{\text{CE}}_{R}$ Valid First: $\mathsf{ADDRESS}_{\mathsf{L},\mathsf{R}}$ ADDRESS MATCH CER . tPS → CEL . ← t<sub>BHC</sub> → BUSY<sub>L</sub> -B136-13

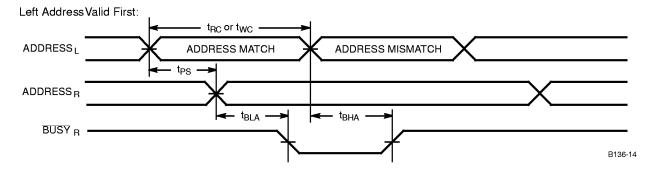

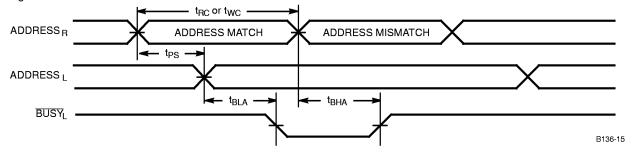

#### **Busy Timing Diagram No.2 (AddressArbitration)**

#### Right AddressValid First:

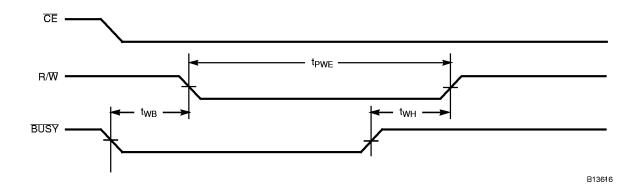

## Busy Timing Diagram No.3 (Write with BUSY, Slave:CY7B146)

## **Interrupt Timing Diagrams**

#### Left Side Sets INT R:

Right Side Clears INT R:

## Right Side Sets INT L:

## Left Side Clears INT L:

#### **Architecture**

The CY7B136 (master) and CY7B146 (slave) are 2048-byte deep dual-port RAMs, with two independent sets of address signals, common I/O data signals, and control signals. By convention, the two ports are called the left port and the right port. The subscript R or L on the signal name identifies the port.

The upper two memory locations (7FF, 7FE) are special locations and may be used as "mailboxes" for passing messages between the ports. Location 7FF is the mailbox for the right port and location 7FE is the mailbox for the left port. When one port writes to the other port's mailbox, an interrupt is generated to the owner of the mailbox. When the owner reads the mailbox, the interrupt is reset.

The address and control signals provide independent, asynchronous, random access to any location in the memory. It is possible that both ports may attempt to access the same memory location at the same time. If this contention occurs, a circuit in the master called an arbiter decides which port temporarily "owns" the memory location. The losing port receives a BUSY signal, which notifies it that the memory location is owned by the other port and that the operation it attempted to perform may not be successful.

The two BUSY signals are outputs from the master and inputs to the slave.

#### Contention, Arbitration and Resolution— The Significance of BUSY

When contention occurs, the arbiter decides which port wins (owns) the memory location and which port loses. The decision is on a "first-come-first-served" basis. In order for contention to occur, both ports must address the same memory location and have their respective chip enables active. If one port precedes the other by an amount of time greater than or equal to  $t_{PS}$  (port set-up for priority;equal to five nanoseconds) it is guaranteed to win the arbitration. If contention occurs within the  $t_{PS}$  interval, it is not possible to predict which port will win, but one will win and the other will lose.

There are two ports and each may be either reading or writing, and each may win or lose, so there are eight combinations. They are listed in *Table 1*. and identified as cases one through eight. In cases one and two, both ports are reading, the losing port receives a BUSY, the read is allowed to occur, and the data read by both ports is valid. In case three, the left port wins and reads valid data, and the write attempted by the right port is inhibited. In cases four and five, when the winning port is writing, the write is completed, but the data read by the losing port may be invalid. Case six is similar to case three; the right port successfully reads and the write attempt by the left port is inhibited. In cases seven and eight the winning port successfully writes and the attempted write by the losing port is inhibited.

In cases four and five, where the losing port is reading, if the port signals are asynchronous to each other, the data read may be the old data, the new data, or some random combination of the two sets of data. In cases seven and eight the losing port is prevented from writing. The commonality between these four cases is that the losing port receives a busy signal, which tells it that either (1) the operation it attempted was not successful, or (2) that the data it read may not be valid. In

either situation, the operation should be repeated after the busy signal becomes inactive.

#### Flow-Through Operation

The CY7B136/146 have a flow-through architecture that facilitates repeating (actually extending) an operation when a BUSY is received by a losing port. The BUSY signal should be interpreted as a NOT READY. If a BUSY to a port is active, the port should wait for BUSY to go inactive, and then extend the operation it was performing for another cycle. The timing diagram titled, "Read Timing with Port-to-Port Delay" illustrates the case where the right port is writing to an address and the left port reads the same address. The data that the right port has just written flows through to the left, and is valid either  $t_{WDD}$  after the falling edge of the write strobe of the left port, or  $t_{DDD}$  after the data being written becomes stable.

The timing diagram titled, "Write Timing with Port-to-Port Delay" illustrates the case where the right port is writing to an address and the left port wants to write to the same address. If the left port extends its write strobe for a minimum time of  $t_{PWE}$  after the BUSY signal to it goes inactive, its write will be successful; it writes over the data just written by the right port.

#### **Data Bus Width Expansion Using Slaves**

One master and as many slaves as necessary may be connected in parallel to expand the data bus width in byte increments

Two masters must not be connected in parallel because, if the time interval between which they address the same location is less than  $t_{PS}$ , both could end up waiting for the other to release the BUSY to it.

Therefore, only one master must arbitrate, and it can drive as many slaves as required. The write strobe to the slaves must be delayed an amount of time equal to at least  $t_{BLA}$ . This insures that the slave is not inadvertently written to before the outcome of the arbitration is determined.

Table 1. Operation.

|      | Operati | on Port | Winning |                                           |

|------|---------|---------|---------|-------------------------------------------|

| Case | L       | R       | Port    | Result                                    |

| 1    | R       | R       | L       | Both Read                                 |

| 2    | R       | R       | R       | Both Read                                 |

| 3    | R       | W       | L       | L Reads OK,<br>R Write Inhibited          |

| 4    | R       | W       | R       | R Writes OK<br>L Data May Be Invalid      |

| 5    | W       | R       | L       | L writes OK<br>R Data May Be In-<br>valid |

| 6    | W       | R       | R       | R Reads OK<br>L Write Inhibited           |

| 7    | W       | W       | L       | L Writes OK<br>R Write Inhibited          |

| 8    | W       | W       | R       | R Writes OK<br>L Write Inhibited          |

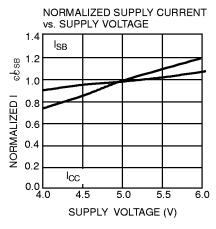

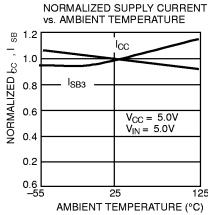

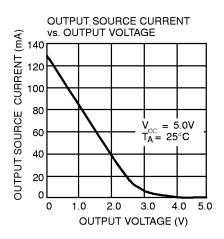

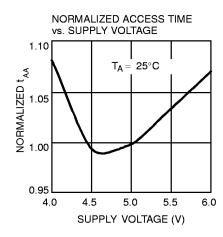

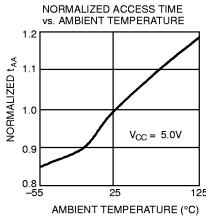

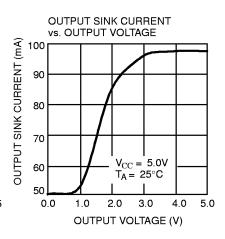

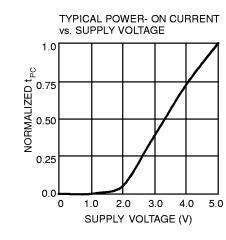

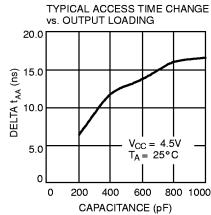

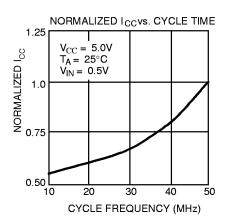

#### Typical DC and AC Characteristics

## **Ordering Information**

| Speed<br>(ns) | Ordering Code                 | Package<br>Name | Package Type                        | Operating<br>Range |

|---------------|-------------------------------|-----------------|-------------------------------------|--------------------|

| 15            | CY7B136-15JC                  | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

| 20            | CY7B136-20JC                  | J69             | 52-Lead Plastic Leaded Chip Carrier | Commercial         |

|               | CY7B136-20JI                  | J69             | 52-Lead Plastic Leaded Chip Carrier | Industrial         |

| _             |                               |                 |                                     |                    |

| Speed<br>(ns) | Ordering Code                 | Package<br>Name | Package Type                        | Operating<br>Range |

|               | Ordering Code<br>CY7B146-15JC |                 | 52-Lead Plastic Leaded Chip Carrier |                    |

| (ns)          |                               | Name            | <del>-</del>                        | Range              |

Document #: 38-00464

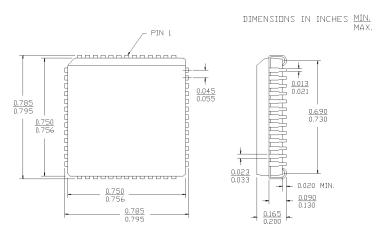

#### **Package Diagram**

#### 52-Lead Plastic Leaded Chip Carrier J69