# **Preliminary**

**RF9678**

#### W-CDMA TRANSMIT MODULATOR AND IF AGC

#### Typical Applications

- W-CDMA Systems

- EDGE Systems

- CDMA Systems

- TDMA Systems

#### **Product Description**

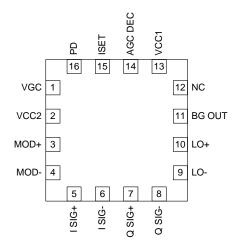

The RF9678 is an integrated complete quadrature modulator and IF AGC amplifier designed for the transmit section of W-CDMA applications. It is designed to modulate baseband I and Q signals, and amplify the resulting IF signals while providing 55dB of gain control range. This circuit is designed as part of RFMD's single mode W-CDMA Chipset, which also includes the RF2679 W-CDMA Receive IF AGC and Demodulator. The IC is manufactured on an advanced Silicon Bi-CMOS process. and is supplied in a16-pin leadless chip carrier.

Optimum Technology Matching® Applied

Si BJT GaAs HBT GaAs MESFET Si Bi-CMOS SiGe HBT Si CMOS

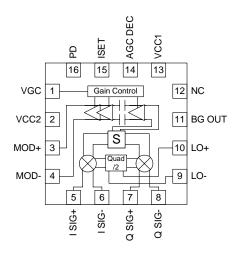

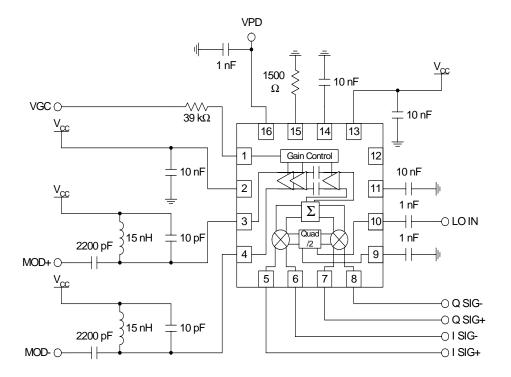

Functional Block Diagram

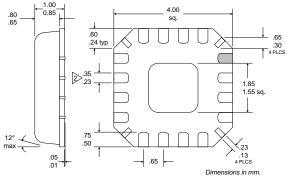

#### NOTES:

- 1> Shaded Pin is Lead 1.

- Dimension applies to plated terminal and is measured between 0.02 mm and 0.25 mm from terminal end.

- Pin 1 identifier must exist on top surface of package by identification mark or feature on the package body. Exact shape and size is optional

- Package Warpage: 0.05 max.

Die thickness allowable: 0.305 mm max.

Package Style: LCC, 16-Pin, 4x4

#### **Features**

- Digitally Controlled Power Down Modes

- 2.7V to 3.3V Operation

- Digital LO Quadrature Divider

- AGC Linearity/Current Consumption Var.

- IF AGC Amp with 55dB Gain Control

#### Ordering Information

RF9678 W-CDMA Transmit Modulator and IF AGC RF9678 PCBA Fully Assembled Evaluation Board

RF Micro Devices, Inc. Tel (336) 664 1233 7628 Thorndike Road Fax (336) 664 0454 Greensboro, NC 27409, USA http://www.rfmd.com

#### **Absolute Maximum Ratings**

| Parameter                             | Rating                     | Unit     |

|---------------------------------------|----------------------------|----------|

| Supply Voltage                        | -0.5 to +5                 | $V_{DC}$ |

| Power Down Voltage (V <sub>PD</sub> ) | -0.5 to $V_{\rm CC}$ + 0.7 | V        |

| I and Q Levels, per pin               | 1.2                        | $V_{PP}$ |

| LO1 Level, balanced                   | +3                         | dBm      |

| Operating Ambient Temperature         | -40 to +85                 | °C       |

| Storage Temperature                   | -40 to +150                | °C       |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                                | Specification        |           | Unit | Condition |                                                                                                |

|------------------------------------------|----------------------|-----------|------|-----------|------------------------------------------------------------------------------------------------|

| Farameter                                | Min.                 | Тур.      | Max. | Unit      | Condition                                                                                      |

| Overall                                  |                      |           |      |           | T=25 °C, $V_{CC}$ =3.0V; $Z_{LOAD}$ =200Ω;<br>I=Q=500m $V_{PP}$ , 1000m $V_{PP}$ Differential; |

|                                          |                      |           |      |           | Output externally matched                                                                      |

| I/Q Input Frequency Range                |                      | 0 to 10   |      | MHz       | Balanced                                                                                       |

| I/Q Input Impedance                      |                      | 20        |      | kΩ        | Balanced                                                                                       |

| I/Q Input Reference Level                |                      | 1.3       |      | $V_{DC}$  | Per Pin                                                                                        |

| LO1 Frequency Range                      |                      | 0 to 1200 |      | MHz       |                                                                                                |

| LO1 Input Level                          | -15                  | -8        | -5   | dBm       | Specifications                                                                                 |

| LO1 Input Impedance                      |                      | 200       |      | Ω         | Balanced (Evaluation Board Schematic)                                                          |

|                                          |                      | 2         |      | kΩ        | Balanced, IC input                                                                             |

| Sideband Suppression                     | 45                   | 50        |      | dBc       | I/Q Amplitude adjusted to within ±20mV                                                         |

|                                          | 25                   | 30        |      | dBc       | Unadjusted                                                                                     |

| Carrier Suppression                      | 45                   | 50        |      | dBc       | I/Q DC Offset adjusted to within ±20 mV                                                        |

|                                          | 20                   | 28        |      | dBc       | Unadjusted                                                                                     |

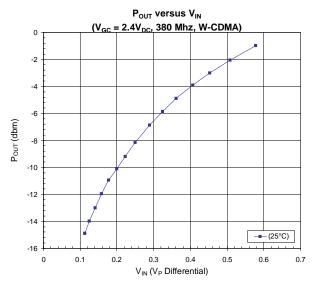

| IF=380MHz                                |                      |           |      |           | I=Q=500mV <sub>PP</sub> , 1000mV <sub>PP</sub> Differential;                                   |

| Mary Code of Daniel W. CDMA              | 0                    | 4.5       |      | dD        | LO1=760 MHz; Output externally matched                                                         |

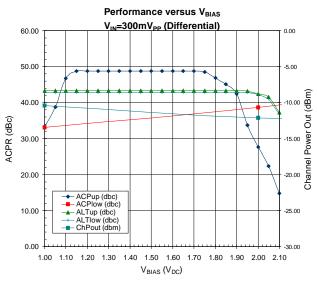

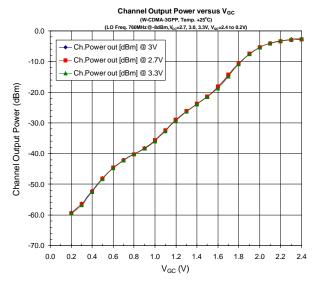

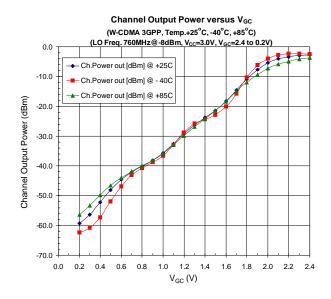

| Max Output Power, W-CDMA<br>Mode         | -6                   | -4.5      | -3   | dBm       | W-CDMA ACPR=-50dBc, V <sub>GC</sub> =2.4V <sub>DC</sub> ,                                      |

|                                          | 00                   | 50        | 50   | -ID       | T=-20°C to +85°C                                                                               |

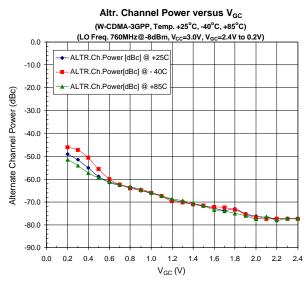

| Min Output Power, CDMA Mode              | -63                  | -59       | -56  | dBm       | $V_{GC}=0.2V_{DC}$                                                                             |

| Output Power Accuracy                    | -3                   |           | +3   | dB        | T=-20 to +85 °C, Ref=25 °C                                                                     |

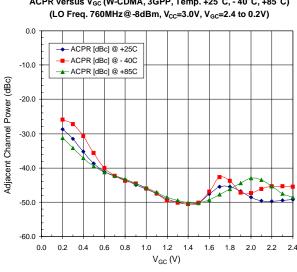

| Adjacent Channel Power Rejection @ 5MHz  |                      |           | -46  | dBc       | W-CDMA Modulation, $V_{GC}=0.2V_{DC}$ to                                                       |

|                                          |                      |           |      |           | 2.4V <sub>DC</sub>                                                                             |

| Adjacent Channel Power Rejection @ 10MHz |                      |           | -56  | dBc       | W-CDMA Modulation, $V_{GC}$ =0.2 $V_{DC}$ to 2.4 $V_{DC}$                                      |

| Output Noise Power                       |                      | -135      |      | dBm/Hz    | @ 20MHz offset, V <sub>GC</sub> =2.4V <sub>DC</sub>                                            |

| Output Impedance                         |                      | 200       |      | Ω         | Balanced                                                                                       |

| ·                                        |                      | 200       |      |           | I=Q=700mV <sub>PP</sub> , 1400mV <sub>PP</sub> Differential;                                   |

| IF=570MHz                                |                      |           |      |           | LO1=1140MHz; Output externally matched                                                         |

| Max Output Power, W-CDMA                 |                      | -4        |      | dBm       | W-CDMA ACPR=-50dBc, V <sub>GC</sub> =2.4V <sub>DC</sub> ,                                      |

| Mode                                     |                      |           |      |           | T=-20°C to +85°C                                                                               |

| Adjacent Channel Power Rejec-            |                      |           | -46  | dBc       | W-CDMA Modulation, V <sub>GC</sub> =0.2V <sub>DC</sub> to                                      |

| tion @ 5MHz                              |                      |           |      |           | 2.4V <sub>DC</sub>                                                                             |

| Adjacent Channel Power Rejec-            |                      |           | -56  | dBc       | W-CDMA Modulation, V <sub>GC</sub> =0.2V <sub>DC</sub> to                                      |

| tion @ 10MHz                             |                      |           |      |           | 2.4V <sub>DC</sub>                                                                             |

| Power Supply                             |                      |           |      |           |                                                                                                |

| Supply Voltage                           | 2.7                  | 3.0       | 3.3  | V         |                                                                                                |

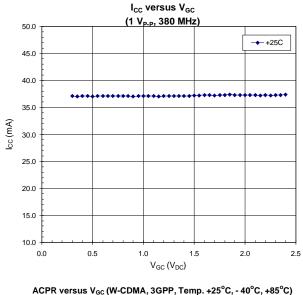

| Current Consumption                      | 30                   | 39        | 46   | mA        | Over temperature                                                                               |

| Power Down Current                       |                      |           | <10  | μΑ        |                                                                                                |

| V <sub>PD</sub> HIGH Voltage             | V <sub>CC</sub> -1.0 |           |      | V         |                                                                                                |

| V <sub>PD</sub> LOW Voltage              |                      |           | 0.9  | V         |                                                                                                |

| Gain Control Range                       | 0.2                  |           | 2.4  | V         |                                                                                                |

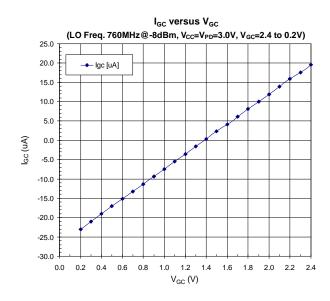

| V <sub>GC</sub> Current                  |                      |           | 40   | μΑ        |                                                                                                |

5-92 Rev A4 010622

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Interface Schematic        |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1   | VGC      | Analog gain control for AGC amplifiers. Valid control voltage ranges are from $0.2 V_{DC}$ to $2.4 V_{DC}$ . The gain range for the AGC is 55dB. These voltages are valid ONLY for a $39  \mathrm{k}\Omega$ source impedance. A DC voltage less than or equal to the maximum allowable $V_{CC}$ may be applied to this pin when no voltage is applied to the $V_{CC}$ pins.                                                                                                                                                                      | VGC O                      |

| 2   | VCC2     | DC supply. This pin should be bypassed to ground with a 10nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

| 3   | MOD+     | Same as pin 4, except complementary output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See pin 4.                 |

| 4   | MOD-     | One half of the balanced AGC output port. The impedance of this port is $200\Omega$ balanced. This pin requires an inductor to $V_{CC}$ to achieve full dynamic range. In order to maximize gain, this inductor should be a high-Q type and should be parallel resonated out with a capacitor (see application schematic). This pin is NOT DC blocked. A blocking capacitor of 2200pF is needed when this pin is connected to a DC path. An appropriate matching network may be needed if an IF filter is used.                                  | BIAS BIAS MOD OUT-MOD OUT+ |

| 5   | I SIG+   | One half of the balanced baseband input to the I mixer. This pin is DC-coupled and must be supplied with 1.3VDC to bias the input transistor. Input impedance of this pin is $10k\Omega$ minimum. For maximum carrier suppression, DC voltage on this pin relative to ISIG- DC voltage may be adjusted. (In case a balun is needed, a seperate balun board (RD0102 PCBA) could be ordered as an accessory.)                                                                                                                                      | See pin 8.                 |

| 6   | I SIG-   | One half of the balanced baseband input to the I mixer. This pin is DC-coupled and must be supplied with 1.3VDC to bias the input transistor. Input impedance of this pin is $10k\Omega$ minimum. For maximum carrier suppression, DC voltage on this pin relative to ISIG+ DC voltage may be adjusted.                                                                                                                                                                                                                                          | I SIG+ O I SIG-            |

| 7   | Q SIG+   | One half of the balanced baseband input to the Q mixer. This pin is DC-coupled and must be supplied with 1.3 VDC to bias the input transistor. Input impedance of this pin is $10  \mathrm{k}\Omega$ minimum. For maximum carrier suppression, DC voltage on this pin relative to QSIG- DC voltage may be adjusted.                                                                                                                                                                                                                              | See pin 10.                |

| 8   | Q SIG-   | One half of the balanced baseband input to the Q mixer. This pin is DC-coupled and must be supplied with 1.3VDC to bias the input transistor. Input impedance of this pin is $10k\Omega$ minimum. For maximum carrier suppression, DC voltage on this pin relative to QSIG+ DC voltage may be adjusted.                                                                                                                                                                                                                                          | Q SIG+ O Q SIG-            |

| 9   | LO-      | One half of the balanced modulator LO1 input. In single-ended applications ( $100\Omega$ input impedance), this pin is AC grounded with a 1nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                         | See pin 10.                |

| 10  | LO+      | One half of the balanced modulator LO1 input. The other half of the input, LO1-, is AC grounded for single-ended input applications. The frequency on these pins is divided by a factor of 2, hence the carrier frequency for the modulator becomes one half of the applied frequency. The single-ended input impedance is $1\mathrm{k}\Omega$ (balanced is $2\mathrm{k}\Omega$ ). This pin is NOT internally DC blocked. An external blocking capacitor (1nF recommended) must be provided if the pin is connected to a device with DC present. | BIAS BIAS LO1-, FM-        |

| 11  | BG OUT   | Bandgap voltage reference. This voltage, constant over temperature and supply variation, is used to bias internal circuits. A 10nF external bypass capacitor is required.                                                                                                                                                                                                                                                                                                                                                                        |                            |

| 12  | NC       | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| 13  | VCC1     | DC supply. This pin should be bypassed to ground with a 10nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

| 14  | AGC DEC  | AGC decoupling pin. An external bypass capacitor of 10nF capacitor is required. The trace length between the pin and the bypass capacitors should be minimized. The ground side of the bypass capacitors should connect immediately to ground plane.                                                                                                                                                                                                                                                                                             |                            |

Preliminary

| Pin         | Function | Description                                                                                                                                                                                                                                                                                                                                                                                         | Interface Schematic |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 15          | ISET     | Connected to ground through an external resistor. The value can be varied to change the current in the AGC for optimum linearity and current consumption.                                                                                                                                                                                                                                           |                     |

| 16          | PD       | Power down control for overall circuit. When logic "high" ( $\geq$ V <sub>CC</sub> -0.7V), all circuits are operating; when logic "low" ( $\leq$ 0.5V), all circuits are turned off. The input impedance of this pin is >10k $\Omega$ . A DC voltage less than or equal to the maximum allowable V <sub>CC</sub> may be applied to this pin when no voltage is applied to the V <sub>CC</sub> pins. | PD O                |

| Pkg<br>Base | GND      | Ground connection. The backside of the package should be soldered to a top side ground pad which is connected to the ground plane with multiple vias.                                                                                                                                                                                                                                               |                     |

5-94 Rev A4 010622

Preliminary RF9678

### **Application Notes**

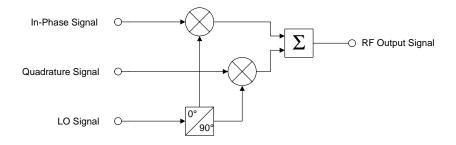

Quadrature modulator performance can be correlated to a set of specifications known as Carrier and Sideband Suppression. In addition, Sideband Suppression can be correlated with the amplitude and phase balance of the In-Phase (I) and Quadrature (Q) signals and Carrier Suppression can be correlated to the DC offset between the I and Q signals (see Figure 1). For a more thorough discussion of the theory and mathematics behind these specifications refer to RF Micro Devices application note AN0001.

Figure 1. Quadrature Modulator Block Diagram

#### Effects of Carrier Suppression and Sideband Suppression on W-CDMA (QPSK) Modulation

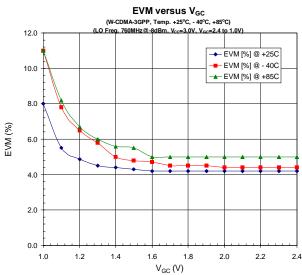

W-CDMA signals may be displayed on a vector signal analyzer as a collection of points called a constellation. Each point in the constellation is called a symbol and is representative of a bit sequence. In QPSK modulation, there are four symbols and each symbol is representative of two data bits (see Figure 2). The I and Q signals are added together to create a vector of precise phase and amplitude. The vector is then sampled at a rate called the symbol rate and it's position at these intervals corresponds to the target symbol locations. Errors in the phase and amplitude of the I and Q signals will translate to errors in the vector's phase and amplitude. This phase and amplitude error will result in a displacement of the vector from it's target symbol point. A measurement of this error is called the Error Vector Magnitude (EVM) and it represents the magnitude of the displacement of the actual vector from it's target location.

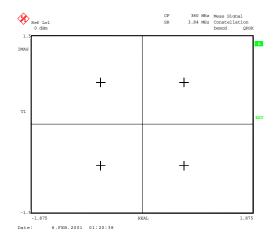

Figure 2. W-CDMA (QPSK) Constellation

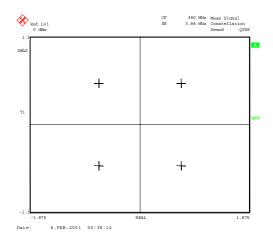

QPSK constellation points exist on a circle of constant radius around the origin. Amplitude errors result in symbol points being displaced either inside or outside of their target locations on this circle. Phase errors result in symbol points being displaced on an arc either to the left or right of their target location. Finally, DC offset errors cause the origin to shift, resulting in a constant I and Q offset of all target points (see Figure 3).

Figure 3. DC Offset Error (Carrier Feedthrough)

As is shown above, the EVM performance of a modulator can be correlated to it's carrier and sideband suppression performance.

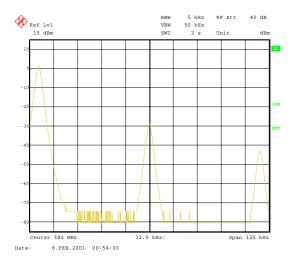

#### **Unadjusted Performance**

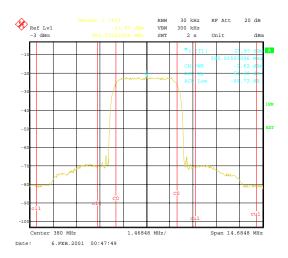

A Wideband CDMA signal is a noise-like signal occupying a channel bandwidth of 3.84MHz. When viewed on a spectrum analyzer the channel appears as a plateau raised above the noise floor (see Figure 4). In some cases, it is normal to see a spike over the center of the W-CDMA plateau. This will occur when the absolute power level of the unadjusted carrier feedthrough is higher than that of the W-CDMA channel level. The cause of this phenomenon can be understood by examining the relative powers of the carrier signal and the W-CDMA channel power.

For Example, a 1Hz channel with a power of 0dBm has an absolute power level of 0dBm when viewed on a spectrum analyzer. When that 0dBm channel power is spread over a 3.84MHz channel, as in W-CDMA, it results in an absolute channel power level of -65.8dBm (-10\*log (BW)). The absolute channel level displayed on the spectrum analyzer will increase with the resolution bandwidth setting on the instrument although the integrated channel power will remain constant. A resolution bandwidth (RBW) of 30kHz will increase the displayed power level by 44.7dB (+10\*log(RBW)) to -21.0dBm. With a desired signal output power of +2.0dBm and a carrier suppression of >20dBc, the absolute carrier level can be as high as -18.0dBm (P<sub>OUT</sub>-Suppression=Carrier Level). This will result in a 3dB carrier spike above the W-CDMA channel level (see Figure 4). (Note: The relative height of the carrier spike above the W-CDMA channel level is directly related to the RBW of the spectrum analyzer being used. The example above assumes a 30kHz RBW.)

The following equations may be used to calculate W-CDMA channel and carrier feedthrough levels.

W-CDMA Channel Level=Channel Power (Integrated over BW)-[10\*log\*(BW)]+[10\*log\*(RBW)]

Carrier Feedthrough=P<sub>OUT</sub> (Desired Sideband)-Carrier Suppression

The next section describes a procedure that may be used to dramatically reduce carrier feedthrough by tuning or optimizing the modulator input signals.

5-96 Rev A4 010622

Preliminary RF9678

Figure 4. W-CDMA Spectral Plot

#### **Adjusted Performance**

In theory, an ideal quadrature modulator will completely suppress the carrier and sideband signals. In practice, due to process and packaging effects, real quadrature modulators lack the balance necessary to completely cancel the carrier and sideband signals. The imbalance caused by process and packaging effects is usually very small and may be corrected by preadjusting the input signals to the modulator. This process of adjusting the input signals to minimize the carrier and sideband suppression is known as optimization.

Sideband suppression results from the summing together of the I and Q channel mixer outputs. In an ideal quadrature modulator, at the summing point the sideband signals from the I and Q mixers are 180° out of phase and have equal magnitudes. In a real modulator, the amplitude and phase are not exactly balanced and 100% cancellation does not occur. The problem is corrected by introducing amplitude and phase corrections before applying a signal to the modulator. Maximum sideband suppression is achieved when the amplitude and phase errors introduced by the modulator are compensated for.

Complete carrier suppression occurs when there is no DC offset between the mixer signal input and the mixer reference voltage (i.e., ISIG+ and ISIG-). In real devices, zero DC offset is difficult to achieve. This problem is corrected by introducing a DC offset of equal and opposite magnitude before applying the signal to the modulator. The internal error is thereby canceled and maximum carrier suppression is achieved.

#### Procedure for RF9678 Quadrature Modulator/AGC Optimization

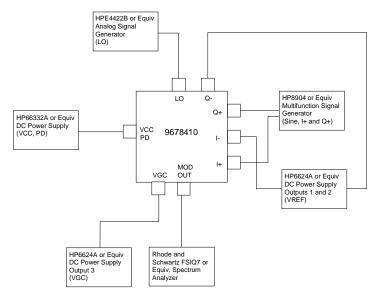

1) Configure the test bench as shown in Figure 5.

Figure 5. RF9678 Test Setup

- 2) Apply  $V_{CC}$  to the part. ( $V_{CC}$ =3.0 V)

- 3) Set gain control to maximum. (V<sub>GC</sub>=2.4V)

- 4) Apply the LO signal. (760MHz@-5dBm, for an IF out of 380MHz)

- 5) Apply the I+ and Q+ signals: (Single Ended)

I Signal: 150kHz@ 500mVp, Phase=0°, 1.3V DC Offset

Q signal: 150kHz@ 500mVp, Phase = 90°, 1.3V DC Offset

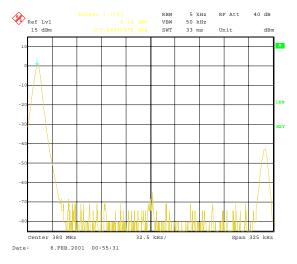

- 6) Set the DC levels at  $I_{SIG}$  and  $Q_{SIG}$  input pins to the nominal value (1.3 V). The output spectrum should look similar to Figure 6.

Figure 6. Unassigned Single Sideband Output

5-98 Rev A4 010622

Preliminary RF9678

#### **Carrier Suppression Optimization**

7) While maintaining a constant DC level (1.3V) on the "ISIG-" pin, adjust the DC level of the "ISIG+" input in as small an increment (~1.0mV) as the test equipment will allow. Observe the output on the spectrum analyzer. Adjust the DC level until the carrier signal is at a minimum. Typically, the minimum will occur within a ±20mV window of the reference voltage (1.3±0.02V).

- 8) While maintaining a constant DC level (1.3V) on the "QSIG-" pin, adjust the DC level of the "QSIG+" input in as small an increment as the test equipment will allow (1.0mV). Observe the output on the spectrum analyzer. Adjust the DC level until the carrier signal is at a minimum. Typically, the minimum will occur within a ±20mV window of the reference voltage (1.3±0.02V).

- 9) Repeating Steps 7 and 8 may yield slightly better suppression. The output spectrum should look similar to Figure 7. (Note the suppressed carrier signal.)

Figure 7. Optimized Carrier Suppression

#### **Sideband Suppression Optimization**

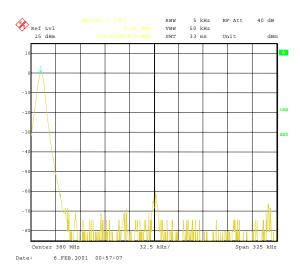

- 10) Adjust the AC amplitude of the "ISIG+" signal in as small an increment as the test equipment will allow (~1mV). Observe the output of the spectrum analyzer. Adjust the AC amplitude of the signal until the sideband signal is at a minimum. The minimum sideband signal level should occur within ±20mV adjustment. (0.500±0.02V)

- 11) Adjust the AC amplitude of the "QSIG+" signal in as small an increment as the test equipment will allow (~1mV). Observe the output of the spectrum analyzer. Adjust the AC amplitude of the signal until the sideband signal is at a minimum. The minimum sideband signal level should occur within ±20mV adjustment (0.500±0.02V).

- 12) Adjust the phase of the "QSIG+" signal in as small an increment as the test equipment will allow ( $^{\circ}0.1^{\circ}$ ). Observe the output of the spectrum analyzer. Adjust the phase of the "QSIG+" signal until the sideband suppression is at a minimum. The sideband signal should reach a minimum within  $\pm 1^{\circ}$  of adjustment ( $90\pm 1^{\circ}$ ).

- 13) The device is now optimized for maximum carrier and sideband suppression. The output spectrum should look similar to Figure 8. (Note the suppressed carrier and sideband signals.)

Figure 8. Optimized Carrier and Sideband Suppression

5-100 Rev A4 010622

# Pin Out

# **Application Schematic**

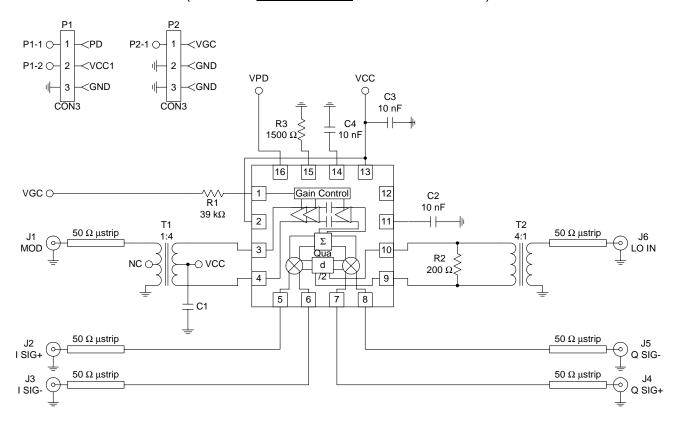

## **Evaluation Board Schematic**

(Download Bill of Materials from www.rfmd.com.)

5-102 Rev A4 010622

# 5

# MODULATORS AND UPCONVERTERS

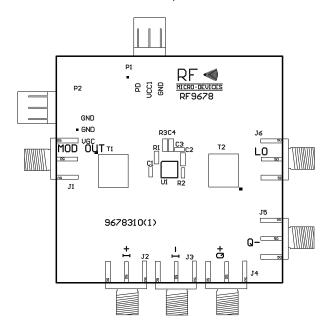

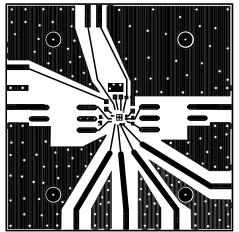

# Evaluation Board Layout Board Size 2.0" x 2.0"

Board Thickness 0.031", Board Material FR-4

5-104 Rev A4 010622

5

MODULATORS AND UPCONVERTERS

5-106 Rev A4 010622