# 4 Mb (512K x 8) ZEROPOWER SRAM

### NOT FOR NEW DESIGN

- INTEGRATED LOW POWER SRAMS, POWER-FAIL CONTROL CIRCUIT and BATTERY

- CONVENTIONAL SRAM OPERATION; UNLIMITED WRITE CYCLES

- 5 YEARS of DATA RETENTION in the ABSENCE of POWER

- AUTOMATIC POWER-FAIL CHIP DESELECT and WRITE PROTECTION

- WRITE PROTECT VOLTAGES:

- $-M48Z512:4.5V \le V_{PFD} \le 4.75V$

- $M48Z512Y:4.2V \le V_{PFD} \le 4.50V$

- BATTERY INTERNALLY ISOLATED UNTIL POWER IS APPLIED

- PIN and FUNCTION COMPATIBLE with JEDEC STANDARD 512K x 8 SRAMs

- The M48Z512/512Y will be replaced shortly by the new version of this product (M48Z512A/512AY) which will maintain the same features and improve data retention to 10 years and speed grade of 70ns

# DESCRIPTION

The M48Z512/512Y 512K x 8 ZEROPOWER RAM is a non-volatile 4,194,304 bit Static RAM organized as 524,288 words by 8 bits. The device combines two internal lithium batteries and a full CMOS SRAMs in a plastic 32 pin DIP long Module.

Table 1. Signal Names

| A0-A18          | Address Inputs        |

|-----------------|-----------------------|

| DQ0-DQ7         | Data Inputs / Outputs |

| Ē               | Chip Enable           |

| G               | Output Enable         |

| w               | Write Enable          |

| Vcc             | Supply Voltage        |

| V <sub>SS</sub> | Ground                |

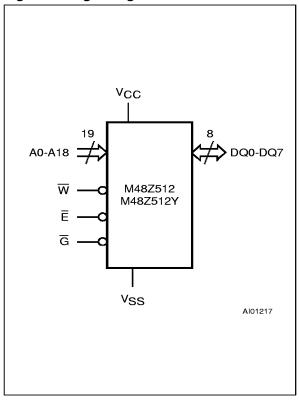

Figure 1. Logic Diagram

April 1997 1/12

This is information on a product still in production but not recommended for new designs

Table 2. Absolute Maximum Ratings

| Symbol            | Parameter                                 | Value     | Unit |

|-------------------|-------------------------------------------|-----------|------|

| T <sub>A</sub>    | Ambient Operating Temperature             | 0 to 70   | °C   |

| T <sub>STG</sub>  | Storage Temperature (V <sub>CC</sub> Off) | -40 to 70 | °C   |

| T <sub>BIAS</sub> | Temperature Under Bias                    | -10 to 70 | °C   |

| T <sub>SLD</sub>  | Lead Soldering Temperature for 10 seconds | 260       | °C   |

| V <sub>IO</sub>   | Input or Output Voltages                  | -0.3 to 7 | V    |

| Vcc               | Supply Voltage                            | –0.3 to 7 | V    |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to the absolute maximum ratings conditions for extended periods of time may affect reliability

CAUTION: Negative undershoots below -0.3 volts are not allowed on any pin while in the Battery Back-up mode.

Table 3. Operating Modes

| Mode     | V <sub>CC</sub>                           | Ē               | G               | w               | DQ0-DQ7         | Power                |

|----------|-------------------------------------------|-----------------|-----------------|-----------------|-----------------|----------------------|

| Deselect |                                           | V <sub>IH</sub> | Х               | Х               | High Z          | Standby              |

| Write    | 4.75V to 5.5V<br>or                       | V <sub>IL</sub> | Х               | V <sub>IL</sub> | D <sub>IN</sub> | Active               |

| Read     | 4.5V to 5.5V                              | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Dout            | Active               |

| Read     |                                           | VIL             | V <sub>IH</sub> | V <sub>IH</sub> | High Z          | Active               |

| Deselect | V <sub>SO</sub> to V <sub>PFD</sub> (min) | Х               | Х               | Х               | High Z          | CMOS Standby         |

| Deselect | ≤ V <sub>SO</sub>                         | Х               | Х               | Х               | High Z          | Battery Back-up Mode |

Note:  $X = V_{IH}$  or  $V_{IL}$

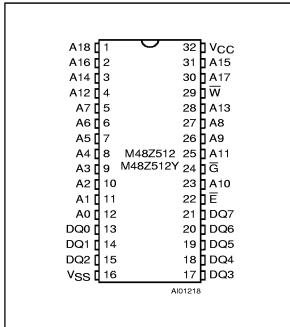

Figure 2. DIP Pin Connections

# **DESCRIPTION** (cont'd)

The ZEROPOWER RAM directly replaces industry standard SRAMs. It also fits into many EPROM and EEPROM sockets, providing the nonvolatility of PROMs without any requirement for special write timing or limitations on the number of writes that can be performed.

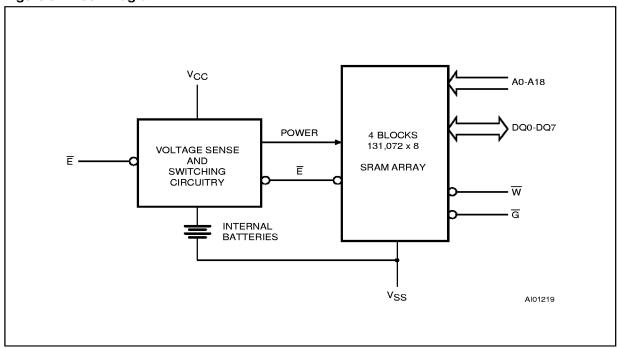

The M48Z512/512Y has its own Power-fail Detect Circuit. The control circuitry constantly monitors the single 5V supply for an out of tolerance condition. When V<sub>CC</sub> is out of tolerance, the circuit write protects the SRAM, providing a high degree of data security in the midst of unpredictable system operations brought on by low V<sub>CC</sub>. As V<sub>CC</sub> falls below approximately 3V, the control circuitry connects the batteries which sustain data until valid power returns.

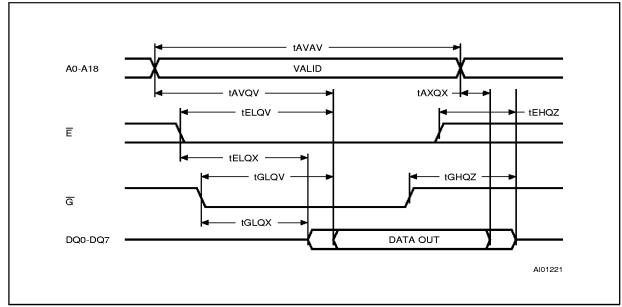

#### **READ MODE**

The M48Z512/512Y is in the Read Mode whenever  $\overline{W}$  (Write Enable) is high and  $\overline{E}$  (Chip Enable) is low. The device architecture allows ripple-through access of data from eight of 4,194,304 locations in the static storage array. Thus, the unique address specified by the 19 Address Inputs defines which

Figure 3. Block Diagram

one of the 524,288 bytes of data is to be accessed. Valid data will be available at the Data I/O pins within  $t_{AVQV}$  (Address Access Time) after the last address input signal is stable, providing that the  $\overline{E}$  (Chip Enable) and  $\overline{G}$  (Output Enable) access times are also satisfied. If the  $\overline{E}$  and  $\overline{G}$  access times are not met, valid data will be available after the later of Chip Enable Access Time ( $t_{ELQV}$ ) or Output Enable Access Time ( $t_{ELQV}$ ).

The state of the eight three-state Data I/O signals is controlled by  $\overline{E}$  and  $\overline{G}$ . If the outputs are activated before  $t_{AVQV}$ , the data lines will be driven to an indeterminate state until  $t_{AVQV}$ . If the Address Inputs are changed while  $\overline{E}$  and  $\overline{G}$  remain low, output data will remain valid for  $t_{AXQX}$  (Output Data Hold Time) but will go indeterminate until the next Address Access.

### WRITE MODE

The M48Z512/512Y is in the Write Mode whenever  $\overline{W}$  and  $\overline{E}$  are active. The start of a write is referenced from the latter occurring falling edge of  $\overline{W}$  or  $\overline{E}$ . A write is terminated by the earlier rising edge of  $\overline{W}$  or  $\overline{E}$ .

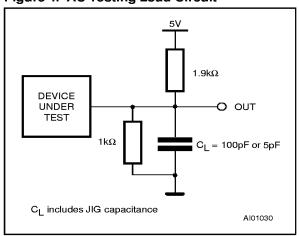

**Table 4. AC Measurement Conditions**

| Input Rise and Fall Times             | ≤ 5ns   |

|---------------------------------------|---------|

| Input Pulse Voltages                  | 0 to 3V |

| Input and Output Timing Ref. Voltages | 1.5V    |

Note that Output Hi-Z is defined as the point where data is no longer driven.

Figure 4. AC Testing Load Circuit

47/

# Table 5. Capacitance $^{(1, 2)}$ (T<sub>A</sub> = 25 °C, f = 1 MHz)

| Symbol              | Parameter                  | Test Condition                | Min | Max | Unit |

|---------------------|----------------------------|-------------------------------|-----|-----|------|

| CIN                 | Input Capacitance          | $V_{IN} = 0V$                 |     | 40  | pF   |

| C <sub>IO</sub> (3) | Input / Output Capacitance | V <sub>OUT</sub> = <b>0</b> V |     | 40  | pF   |

Notes: 1. Effective capacitance measured with power supply at 5V. 2. Sampled only, not 100% tested. 3. Outputs deselected

# Table 6. DC Characteristics

$(T_A = 0 \text{ to } 70^{\circ}\text{C}; \ V_{CC} = 4.75\text{V to } 5.5\text{V or } 4.5\text{V to } 5.5\text{V})$

| Symbol                         | Parameter                     | Test Condition                         | Min  | Max                   | Unit |

|--------------------------------|-------------------------------|----------------------------------------|------|-----------------------|------|

| I <sub>LI</sub> <sup>(1)</sup> | Input Leakage Current         | $0V \le V_{IN} \le V_{CC}$             |      | ±4                    | μΑ   |

| I <sub>LO</sub> <sup>(1)</sup> | Output Leakage Current        | $0V \le V_{OUT} \le V_{CC}$            |      | ±4                    | μΑ   |

| Icc                            | Supply Current                | $\overline{E} = V_{IL}$ , Outputs open |      | 115                   | mA   |

| Icc <sub>1</sub>               | Supply Current (Standby) TTL  | E = VIH                                |      | 17                    | mA   |

| I <sub>CC2</sub>               | Supply Current (Standby) CMOS | $\overline{E} \ge V_{CC} - 0.2V$       |      | 5                     | mA   |

| VIL                            | Input Low Voltage             |                                        | -0.3 | 0.8                   | ٧    |

| V <sub>IH</sub>                | Input High Voltage            |                                        | 2.2  | V <sub>CC</sub> + 0.3 | ٧    |

| V <sub>OL</sub>                | Output Low Voltage            | I <sub>OL</sub> = 2.1mA                |      | 0.4                   | ٧    |

| V <sub>OH</sub>                | Output High Voltage           | I <sub>OH</sub> = -1mA                 | 2.4  |                       | ٧    |

Note: 1. Outputs deselected.

# Table 7. Power Down/Up Trip Points DC Characteristics (1) $(T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Symbol                         | Parameter                              | Min | Тур | Max  | Unit     |

|--------------------------------|----------------------------------------|-----|-----|------|----------|

| V <sub>PFD</sub>               | Power-fail Deselect Voltage (M48Z512)  | 4.5 | 4.6 | 4.75 | ٧        |

| V <sub>PFD</sub>               | Power-fail Deselect Voltage (M48Z512Y) | 4.2 | 4.3 | 4.5  | <b>V</b> |

| V <sub>SO</sub>                | Battery Back-up Switchover Voltage     |     | 3   |      | ٧        |

| t <sub>DR</sub> <sup>(2)</sup> | Data Retention Time                    | 10  |     |      | YEARS    |

Notes: 1. All voltages referenced to Vss. 2. @ 25°C

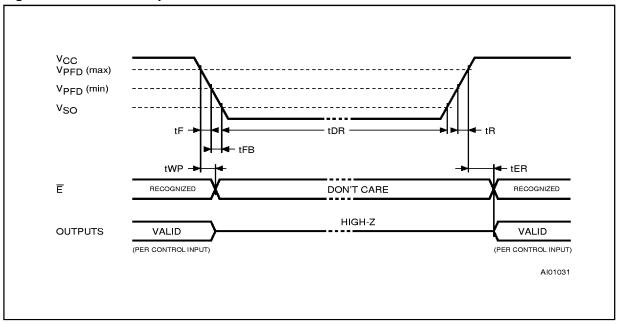

Table 8. Power Down/Up Mode AC Characteristics ( $T_A = 0 \ to \ 70\,^{\circ}C$ )

| Symbol                        | Parameter                                                                  | Min | Max | Unit |

|-------------------------------|----------------------------------------------------------------------------|-----|-----|------|

| t <sub>F</sub> <sup>(1)</sup> | V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> Fall Time | 300 |     | μs   |

| t <sub>FB</sub> (2)           | V <sub>PFD</sub> (min) to V <sub>SO</sub> V <sub>CC</sub> Fall Time        | 10  |     | μs   |

| t <sub>WP</sub>               | Write Protect Time from V <sub>CC</sub> = V <sub>PFD</sub>                 | 40  | 150 | μs   |

| t <sub>R</sub>                | V <sub>SO</sub> to V <sub>PFD</sub> (max) V <sub>CC</sub> Rise Time        | 0   |     | μs   |

| ter                           | E Recovery Time                                                            | 40  | 120 | ms   |

Notes: 1. V<sub>PFD</sub> (max) to V<sub>PFD</sub> (min) fall time of less than t<sub>F</sub> may result in deselection/write protection not occurring until 200 μs after V<sub>CC</sub> passes V<sub>PFD</sub> (min).

Figure 5. Power Down/Up Mode AC Waveforms

<sup>2.</sup>  $V_{\text{PFD}}$  (min) to  $V_{\text{SO}}$  fall time of less than  $t_{\text{FB}}$  may cause corruption of RAM data.

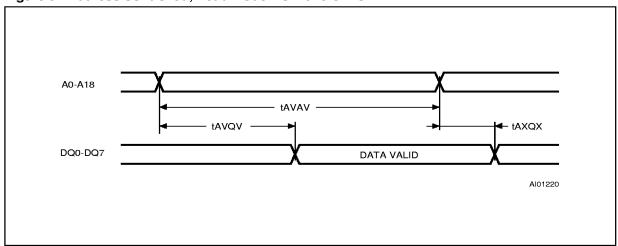

Table 9. Read Mode AC Characteristics ( $T_A = 0 \text{ to } 70 \,^{\circ}\text{C}$ ;  $V_{CC} = 4.75 \text{V to } 5.5 \text{V or } 4.5 \text{V to } 5.5 \text{V}$ )

| Symbol                | Parameter                               | -85<br>Min Max |    | -85 -120 |     | Unit |

|-----------------------|-----------------------------------------|----------------|----|----------|-----|------|

|                       |                                         |                |    | Min      | Max |      |

| t <sub>AVAV</sub>     | Read Cycle Time                         | 85             |    | 120      |     | ns   |

| t <sub>AVQV</sub> (1) | Address Valid to Output Valid           |                | 85 |          | 120 | ns   |

| t <sub>ELQV</sub> (1) | Chip Enable Low to Output Valid         |                | 85 |          | 120 | ns   |

| t <sub>GLQV</sub> (1) | Output Enable Low to Output Valid       |                | 45 |          | 60  | ns   |

| t <sub>ELQX</sub> (2) | Chip Enable Low to Output Transition    | 5              |    | 5        |     | ns   |

| t <sub>GLQX</sub> (2) | Output Enable Low to Output Transition  | 0              |    | 0        |     | ns   |

| t <sub>EHQZ</sub> (2) | Chip Enable High to Output Hi-Z         |                | 35 |          | 45  | ns   |

| t <sub>GHQZ</sub> (2) | Output Enable High to Output Hi-Z       |                | 25 |          | 35  | ns   |

| taxqx (1)             | Address Transition to Output Transition | 5              |    | 5        |     | ns   |

Notes: 1. C<sub>L</sub> = 100pF (see Figure 4). 2. C<sub>L</sub> = 5pF (see Figure 4)

Figure 6. Address Controlled, Read Mode AC Waveforms

**Note:** Chip Enable  $(\overline{E})$  and Output Enable  $(\overline{G})$  = Low, Write Enable  $(\overline{W})$  = High.

Figure 7. Chip Enable or Output Enable Controlled, Read Mode AC Waveforms

**Note:** Write Enable  $(\overline{W})$  = High.

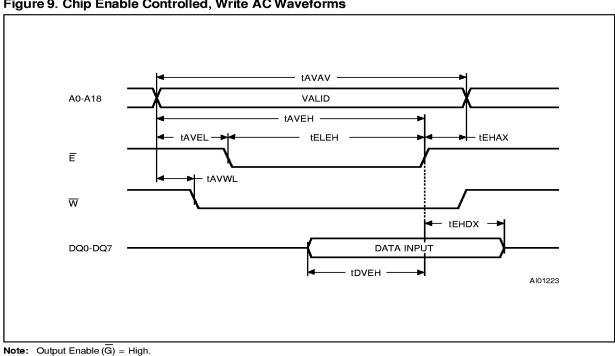

### WRITE MODE (cont'd)

The addresses must be held valid throughout the cycle.  $\overline{E}$  or  $\overline{W}$  must return high for minimum of  $t_{EHAX}$  from  $\overline{E}$  or  $t_{WHAX}$  from  $\overline{W}$  prior to the initiation of another read or write cycle. Data-in must be valid  $t_{DVEH}$  or  $t_{WHDX}$  prior to the end of write and remain valid for  $t_{EHDX}$  or  $t_{WHDX}$  afterward.  $\overline{G}$  should be kept high during write cycles to avoid bus contention; although, if the output bus has been activated by a low on  $\overline{E}$  and  $\overline{G}$ , a low on  $\overline{W}$  will disable the outputs  $t_{WLOZ}$  after  $\overline{W}$  falls.

## **DATA RETENTION MODE**

With valid V<sub>CC</sub> applied, the M48Z512/512Y operates as a conventional BYTEWIDE™ static RAM. Should the supply voltage decay, the RAM will automatically power-fail deselect, write protecting

itself  $t_{WP}$  after  $V_{CC}$  falls below  $V_{PFD}$ . All outputs become high impedance, and all inputs are treated as "don't care."

If power fail detection occurs during a valid access, the memory cycle continues to completion. If the memory cycle fails to terminate within the time  $t_{WP}$ , write protection takes place. When  $V_{CC}$  drops below  $V_{SO}$ , the control circuit switches power to the internal energy source which preserves data.

The internal coin cells will maintain data in the M48Z512/512Y after the initial application of  $V_{CC}$  for an accumulated period of at least 5 years when  $V_{CC}$  is less than  $V_{SO}$ . As system power returns and  $V_{CC}$  rises above  $V_{SO}$ , the batteries are disconnected, and the power supply is switched to external  $V_{CC}$ . Write protection continues for  $t_{ER}$  after  $V_{CC}$  reaches  $V_{PFD}$  to allow for processor stabilization. After  $t_{ER}$ , normal RAM operation can resume.

Table 10. Write Mode AC Characteristics ( $T_A = 0 \text{ to } 70 \,^{\circ}\text{C}$ ;  $V_{CC} = 4.75 \text{V to } 5.5 \text{V or } 4.5 \text{V to } 5.5 \text{V}$ )

| Symbol                  | Parameter                               | M48Z512 / M48Z512Y |     |      |     |      |

|-------------------------|-----------------------------------------|--------------------|-----|------|-----|------|

|                         |                                         | -4                 | 85  | -120 |     | Unit |

|                         |                                         | Min                | Max | Min  | Max |      |

| t <sub>AVAV</sub>       | Write Cycle Time                        | 85                 |     | 120  |     | ns   |

| t <sub>AVWL</sub>       | Address Valid to Write Enable Low       | 0                  |     | 0    |     | ns   |

| tavel                   | Address Valid to Chip Enable Low        | 0                  |     | 0    |     | ns   |

| $t_{WLWH}$              | Write Enable Pulse Width                | 65                 |     | 85   |     | ns   |

| t <sub>ELEH</sub>       | Chip Enable Low to Chip Enable High     | 75                 |     | 100  |     | ns   |

| t <sub>WHAX</sub>       | Write Enable High to Address Transition | 5                  |     | 5    |     | ns   |

| t <sub>EHAX</sub>       | Chip Enable High to Address Transition  | 15                 |     | 15   |     | ns   |

| t <sub>DVWH</sub>       | Input Valid to Write Enable High        | 35                 |     | 45   |     | ns   |

| t <sub>DVEH</sub>       | Input Valid to Chip Enable High         | 35                 |     | 45   |     | ns   |

| twHDX                   | Write Enable High to Input Transition   | 0                  |     | 0    |     | ns   |

| $t_{EHDX}$              | Chip Enable High to Input Transition    | 10                 |     | 10   |     | ns   |

| t <sub>WLQZ</sub> (1,2) | Write Enable Low to Output Hi-Z         |                    | 30  |      | 40  | ns   |

| t <sub>AVWH</sub>       | Address Valid to Write Enable High      | 75                 |     | 100  |     | ns   |

| t <sub>AVEH</sub>       | Address Valid to Chip Enable High       | 75                 |     | 100  |     | ns   |

| t <sub>WHQX</sub> (1,2) | Write Enable High to Output Transition  | 5                  |     | 5    |     | ns   |

477

Notes: 1. C\_= 5pF (see Figure 4).

2. If E goes low simultaneously with W going low, the outputs remain in the high-impedance state.

tAVAV A0-A18 VALID tAVWH -- tAVEL - tWHAX Ē tWLWH tAVWL  $\overline{\mathsf{w}}$ tWLQZ tWHQX tWHDX · DATA INPUT DQ0-DQ7 tDVWH AI01222

Figure 8. Write Enable Controlled, Write AC Waveforms

**Note:** Output Enable  $(\overline{G})$  = High.

Figure 9. Chip Enable Controlled, Write AC Waveforms

47/

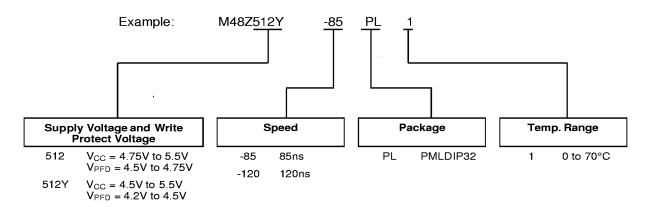

### ORDERING INFORMATION SCHEME

The M48Z512/512Y will be replaced shortly by the new version of this product (M48Z512A/512AY) which will maintain the same features and improve data retention to 10 years and speed grade of 70ns.

For a list of available options (Speed, etc...) or for further information or any aspect of this device, please contact the SGS-THOMSON Sales Office nearest to you.

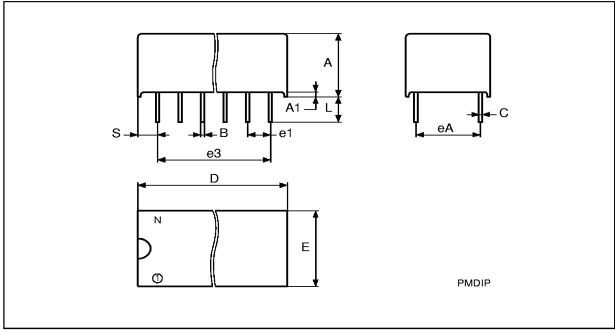

PMLDIP32 - 32 pin Plastic DIP Long Module

| Symb | mm  |       |       | inches |       |       |  |

|------|-----|-------|-------|--------|-------|-------|--|

| Symb | Тур | Min   | Max   | Тур    | p Min |       |  |

| Α    |     | 9.27  | 9.52  |        | 0.365 | 0.375 |  |

| A1   |     | 0.38  | _     |        | 0.015 | _     |  |

| В    |     | 0.43  | 0.59  |        | 0.017 | 0.023 |  |

| С    |     | 0.20  | 0.33  |        | 0.008 | 0.013 |  |

| D    |     | 52.58 | 53.34 |        | 2.070 | 2.100 |  |

| Е    |     | 18.03 | 18.80 |        | 0.710 | 0.740 |  |

| e1   |     | 2.29  | 2.79  |        | 0.090 | 0.110 |  |

| e3   |     | 34.29 | 41.91 |        | 1.350 | 1.650 |  |

| eA   |     | 14.99 | 16.00 |        | 0.590 | 0.630 |  |

| L    |     | 3.05  | 3.81  |        | 0.120 | 0.150 |  |

| S    |     | 6.99  | 7.87  |        | 0.275 | 0.310 |  |

| N    |     | 32    |       |        | 32    |       |  |

PMLDIP32

Drawing is not to scale.