## MC68605

## Technical Summary

## X.25 Protocol Controller

The MC68605 X.25 protocol controller (XPC) is an intelligent HCMOS communications protocol controller that implements the 1984 International Telegraph and Telephone Consultative Committee (CCITT) X.25 Recommendation data link access procedure (LAPB). It supports full-duplex point-to-point serial communication at up to 10 Mbps and relieves the host processor of managing the communications link by providing sequencing using HDLC framing, error control, retransmission based upon a cyclic redundancy check (CRC), and flow control using the receive-not-ready supervisory frame. The XPC directly supports the physical level interfaces (Recommendation X.21 physical level, X.21 bis, and V-series) and also provides an efficient interface to the packet level for information and control exchange. Key features of the XPC include:

- Fully Implements X.25 Recommendation LAPB Procedure by Independently Generating Link-Level Commands and Responses

- Option To Implement X.75 Recommendation

- Optional Transparent Operation (Monitor Mode) where XPC Provides High-Level/Synchronous Data Link Control (HDLC/SDLC) Framing Functions for User-Generated Frames

- Performs Direct Memory Access (DMA) Transfer of Information Frames to and from Memory Using Two On-Chip 22-Byte FIFOs

- Primary Communication through Shared Memory Structures with a Powerful Command Set to Off-Load Data Link Management

- Flexible Rx/Tx Linked Memory Structures Minimize Host Intervention and Simplify Memory Management

- Basic (Modulo 8) and Extended (Modulo 128) Operation

- Automatic Comparison of the Programmable Local and Remote Addresses

- Detects Programmable Time-Out and Retries Limit Conditions

- 16- or 32-Bit CRC Generation and Checking

This document contains information on a new product. Specifications and information herein are subject to change without notice.

**MOTOROLA**

M68000 FAMILY REFERENCE MANUAL

8-55

8

- Standard Modem Interface

- NRZ or NRZI Encoding/Decoding

- Vectored Interrupts and Status Reporting

- Built-In Diagnostics Provide Local Loopback and External Loopback Testing

- Up to 10-Mbps Synchronous Serial Data Rate

- 12.5- and 10-MHz System Clock Versions

- 8- and 16-Bit Data Bus Support

- 32-Bit Address Bus with Virtual Address Capability

- M68000 Family Asynchronous Bus Structure

- Programmable Byte Ordering of Data for Alternate Memory Organization Schemes

#### **GENERAL DESCRIPTION**

The XPC supports high-speed X.25 communications between host computers, between host computers and remote units, and between remote units. The XPC also supports a transparent operation mode that does not apply the LAPB procedure. Data is passed between the XPC and the host processor through shared memory structures, permitting a minimum command set for host processor/XPC communication. The XPC is also a full M68000 bus master, providing on-chip DMA capability for management of memory tables and frame buffers. Since the XPC data bus interface is configurable, the XPC can handle both 8- and 16-bit data transfers.

When the X.25 mode is selected by the user, the XPC is configured as a combined station for full-duplex point-to-point communication. The XPC supports a nonoperational mode and two operational modes as defined by the LAPB procedure. The nonoperational mode is asynchronous disconnect mode (ADM). In this balanced data link mode, the combined station is logically disconnected from the data link and is not permitted to transmit or accept information. Operational modes include asynchronous balanced mode (ABM) and asynchronous balanced mode extended (ABME). A balanced data link allows a combined station to send a command or initiate a response frame transmission without receiving explicit permission from the other station. In ABM/ABME, the XPC performs the following operations:

Transmission of a chain of information (I) frames when instructed by the host,

8-56

M68000 FAMILY REFERENCE MANUAL

- Transmission of supervisory (S) frames as defined by the X.25 LAPB Recommendation,

- 3. Transmission of unnumbered (U) commands as required or when instructed by the host, and

- 4. Transmission of unnumbered (U) responses as defined by the X.25 LAPB Recommendation.

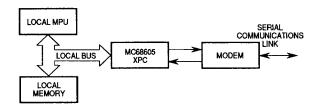

When the transparent mode is selected, the XPC can be configured as a master, a slave, or a combined station for full-duplex operation. The XPC can support any HDLC/SDLC-defined operational mode (see Figure 1). All frames are user generated and are transmitted only when instructed by the host.

Figure 1. XPC System Configuration

#### **INTERNAL REGISTERS**

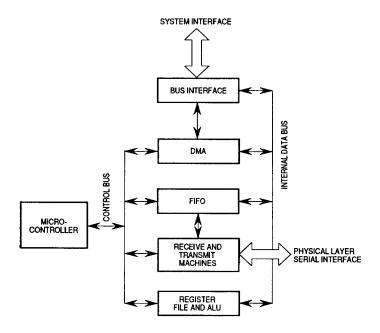

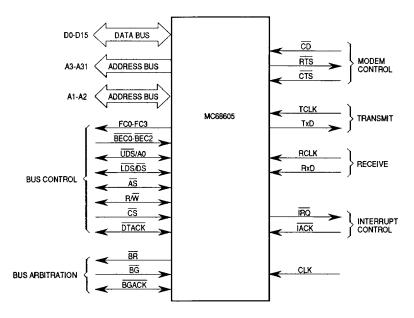

The XPC has four functional blocks: serial, DMA, microcode controller, and register file/arithmetic logic unit (ALU). Each section contains user-visible and nonvisible registers that define and control the operation of the XPC. A block diagram of the XPC is shown in Figure 2.

**MOTOROLA**

M68000 FAMILY REFERENCE MANUAL

Figure 2. Block Diagram

Because the XPC communicates with the host primarily through shared memory, minimal host-processor-accessible registers are required. Registers in the XPC fall into two groups. One group is directly accessible by the user, and the other group is indirectly accessible through the station table. The directly accessible registers include the command register, semaphore register, interrupt vector register, and data register. The complete register set is shown in Table 1.

**M68000 FAMILY REFERENCE MANUAL**

Table 1. XPC Register Set

| Directly Accessible Registers   |                                                                         |      |  |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------|------|--|--|--|--|--|

| Register                        | Register Description                                                    |      |  |  |  |  |  |

| Command                         | 8-Bit Write Only                                                        |      |  |  |  |  |  |

| Semaphore                       | 8-Bit Read Only                                                         |      |  |  |  |  |  |

| Interrupt Vector                | 8-Bit Write Only, Read on Host<br>Processor Interrupt Acknowledge Cycle |      |  |  |  |  |  |

| Data                            | 32-Bit Write Only                                                       | ′    |  |  |  |  |  |

| Indirectly Accessible Registers |                                                                         |      |  |  |  |  |  |

| Reg                             | Mnemonic                                                                |      |  |  |  |  |  |

| Station Table Poi               | nter                                                                    | STP  |  |  |  |  |  |

| Station Table Fur               | nction Code                                                             | STFC |  |  |  |  |  |

| Local Address                   |                                                                         | LA   |  |  |  |  |  |

| Remote Address                  |                                                                         | RA   |  |  |  |  |  |

| Hardware Config                 | uration                                                                 | HC   |  |  |  |  |  |

| Station Configura               | ation                                                                   | sc   |  |  |  |  |  |

| Option Bits                     |                                                                         | ОВ   |  |  |  |  |  |

| Mode Descriptor                 |                                                                         | MD   |  |  |  |  |  |

| Frame Reject Des                | scriptor                                                                | FRD  |  |  |  |  |  |

| Rx/Host Status                  |                                                                         | RHS  |  |  |  |  |  |

| Tx/Link Status                  | -                                                                       | TLS  |  |  |  |  |  |

| Register                      | Mnemonic |

|-------------------------------|----------|

| V(S)                          | V(S)     |

| V(R)                          | V(R)     |

| Time Scale Divider            | TSD      |

| Retries Count                 | RC       |

| Transmit Table Pointer        | TTP      |

| Transmit Table Function Code  | TTFC     |

| Transmit Buffer Pointer       | ТВР      |

| Transmit Buffer Function Code | TBFC     |

| Transmit Buffer Count         | TBC      |

| Receive Table Pointer         | RTP      |

| Receive Table Function Code   | RTFC     |

| Receive Buffer Pointer        | RBP      |

| Receive Buffer Function Code  | RBFC     |

| Receive Buffer Count          | RBC      |

| Time-Out Preset               | TOP      |

| Retries Limit                 | RL       |

| Outstanding Frames Limit      | OFL      |

| Pad Time Select               | PTS      |

| Last Received N(R)            | LRN      |

## **SHARED MEMORY STRUCTURES**

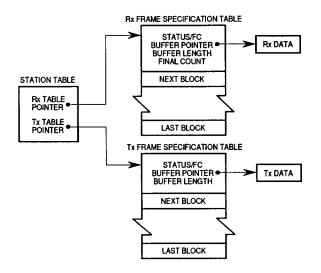

The host processor communicates with the XPC using three tables located in shared memory (see Figure 3). The station table allows the host processor to initialize and update the XPC operating parameters and table pointers and to receive status and error information. The transmit frame specification table queues frames to be transmitted by the XPC, and the receive frame specification table queues available receive buffers for the XPC to store received information frames. The XPC is given a pointer to the station table during initialization. The transmit frame specification table and receive frame specification table pointers are contained in the station table.

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

Figure 3. Shared Memory Tables

#### STATION TABLE

The station table format is shown in Figure 4. The first 19 words of the station table are written by the host processor and are read by the XPC. This portion of the table contains the XPC operating information. The XPC accesses this table area as the result of a host processor command. The next 22 words of the table are written by the XPC and read by the host processor. Some of these entries are written by the XPC as the result of a command while other entries are updated by the XPC when a change occurs. When the XPC accesses the table as the result of a host processor command, it sets the semaphore register to \$FF upon completion of the last access. While the XPC is processing a command, the semaphore register is \$FE.

M68000 FAMILY REFERENCE MANUAL

| WORD | 15 12       | . 11                      | 3 7 4           | 3 0       |  |  |  |  |  |

|------|-------------|---------------------------|-----------------|-----------|--|--|--|--|--|

| 0    |             | OPTION BITS               |                 |           |  |  |  |  |  |

| 1    |             | TIME-0                    | JT PRESET       |           |  |  |  |  |  |

| 2    | TIME SCA    | LE DIVIDER                | PAD TIN         | 1E SELECT |  |  |  |  |  |

| 3    | OUTSTANDING | FRAMES LIMIT              | RETRIE          | S LIMIT   |  |  |  |  |  |

| 4    |             | Rx/HOST                   | MASK BITS       |           |  |  |  |  |  |

| 5    |             | Tx/LINK                   | MASK BITS       |           |  |  |  |  |  |

| 6    |             | Rx/HOST STATUS CLEAR BITS |                 |           |  |  |  |  |  |

| 7    |             | Tx/LINK STATUS CLEAR BITS |                 |           |  |  |  |  |  |

| 8    | 0000        | 0000                      | LOCAL ADDRESS   |           |  |  |  |  |  |

| 9    | 0000        | 0000                      | REMOTE          | ADDRESS   |  |  |  |  |  |

| 10   | 0000        | 0000                      | 0000            | RTFC      |  |  |  |  |  |

| 11   | RE          | CEIVE TABLE PO            | INTER — HIGH W  | ORD       |  |  |  |  |  |

| 12   | RI          | CEIVE TABLE PO            | INTER — LOW W   | ORD       |  |  |  |  |  |

| 13   | 0000        | 0000                      | 0000            | TTFC      |  |  |  |  |  |

| 14   | TRA         | NSMIT TABLE P             | OINTER — HIGH \ | WORD      |  |  |  |  |  |

| 15   | TRA         | NSMIT TABLE F             | OINTER LOW V    | VORD      |  |  |  |  |  |

| 16   | 0000        | 0000                      | 0000            | DAFC      |  |  |  |  |  |

| 17   |             | DUMP AREA POII            | NTER — HIGH WO  | RD        |  |  |  |  |  |

| 18   |             | DUMP AREA POI             | NTER — LOW WO   | RD        |  |  |  |  |  |

HOST PROCESSOR AREA: READ BY THE XPC; WRITTEN BY HOST PROCESSOR

|                                         | Rx/HOST        | STATUS         |           |  |  |  |  |  |  |  |

|-----------------------------------------|----------------|----------------|-----------|--|--|--|--|--|--|--|

|                                         | Tx/LINK STATUS |                |           |  |  |  |  |  |  |  |

| MODE DESCRIPTOR FRAME REJECT DESCRIPTOR |                |                |           |  |  |  |  |  |  |  |

| V(                                      | S)             | V(             | R)        |  |  |  |  |  |  |  |

| 0000                                    | 0000           | 0000           | FUFC      |  |  |  |  |  |  |  |

| FIRST UN                                | IACKNOWLEDGE   | POINTER HIG    | H WORD    |  |  |  |  |  |  |  |

| FIRST UN                                | IACKNOWLEDGE!  | POINTER — LO   | W WORD    |  |  |  |  |  |  |  |

| 0000                                    | 0000           | 0000           | TFC       |  |  |  |  |  |  |  |

| T                                       | RANSMIT POINT  | ER — HIGH WOR  | D         |  |  |  |  |  |  |  |

| T                                       | RANSMIT POINT  | ER — LOW WOR   | D         |  |  |  |  |  |  |  |

| 0000                                    | 0000           | 0000           | RTFC      |  |  |  |  |  |  |  |

|                                         | RECEIVE POINTE | R — HIGH WORD  |           |  |  |  |  |  |  |  |

|                                         | RECEIVE POINTE | R — LOW WORD   |           |  |  |  |  |  |  |  |

| 0000                                    | 0000           | 0000           | REFC      |  |  |  |  |  |  |  |

| RECEIVE BU                              | JS/ADDRESS ERR | OR POINTER — F | HIGH WORD |  |  |  |  |  |  |  |

| RECEIVE BI                              | US/ADDRESS ERR | OR POINTER — L | .OW WORD  |  |  |  |  |  |  |  |

| 0000                                    | 0000           | 0000           | TEFC      |  |  |  |  |  |  |  |

| TRANSMIT E                              | BUS/ADDRESS ER | ROR POINTER    | HIGH WORD |  |  |  |  |  |  |  |

| TRANSMIT E                              | BUS/ADDRESS ER | ROR POINTER —  | LOW WORD  |  |  |  |  |  |  |  |

| RECEIVE                                 | D FRMR INFORM  | IATION FIELD   | WORD 1    |  |  |  |  |  |  |  |

| RECEIVE                                 | D FRMR INFORM  | MATION FIELD — | WORD 2    |  |  |  |  |  |  |  |

| RECEIVE                                 | D FRMR INFORM  | MATION FIELD — | WORD 3    |  |  |  |  |  |  |  |

XPC AREA: READ BY THE HOST PROCESSOR; WRITTEN BY THE XPC

Figure 4. Station Table Structure

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

#### TRANSMIT FRAME SPECIFICATION TABLE

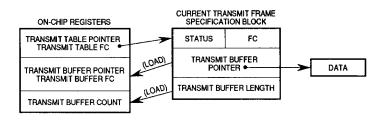

The transmit frame specification table queues transmit frames for the XPC. These frames are stored in memory buffers located throughout memory. The transmit frame specification table contains a sequential list of transmit frame specification blocks. The transmit frame specification blocks describe the location of transmit buffers and provide information about the transmit queue. The transmit table pointer location in the station table points to the first transmit frame specification block (see Figure 5).

Figure 5. Transmit Frame Specification Table

When the host processor instructs the XPC to load transmit table pointer, the XPC loads the transmit table pointer and transmit table function code registers from the corresponding station table entries. The transmit table pointer register then has the address of the first transmit frame specification block. Before the transmission of each frame, the XPC accesses the current transmit frame specification block to load the transmit buffer function code, transmit buffer address, and transmit buffer length into the corresponding internal registers. The XPC presents a transmit buffer address and function code to the system to load the information contained in the transmit buffer.

During transparent operation, the XPC accesses the next transmit frame specification block and transmits the corresponding frame buffer until the end of the transmit frame specification table is reached. The XPC updates its internal V(S) register after the transmission of each frame. When all frames have been transmitted, the XPC sets the information frames acknowledged (IFAK) bit in the Tx/link status register.

During X.25 operation, the XPC accesses the next transmit frame specification block and transmits the corresponding frame buffer according to the X.25 Recommendation until reaching either the outstanding frames limit or the end of the transmit frame specification table. The XPC updates its internal V(S) registers after the transmission of an information frame. The XPC monitors the N(R) of incoming frames until all transmitted frames have been acknowledged.

M68000 FAMILY REFERENCE MANUAL

After all frames have been acknowledged, the XPC sets the IFAK bit in the Tx/link status register.

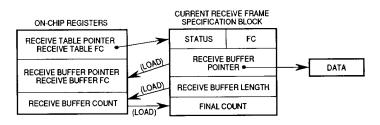

#### RECEIVE FRAME SPECIFICATION TABLE

The receive frame specification table queues receive buffers for the XPC. These buffers are stored throughout memory. The receive frame specification table contains a sequential list of receive frame specification blocks. The receive frame specification blocks describe the location of the receive buffers and provide information about the queue. The receive table pointer in the station table points to the first receive frame specification block (see Figure 6).

Figure 6. Receive Frame Specification Table

When the host processor instructs the XPC to load receive table pointer, the XPC loads the receive table function code and receive table pointer registers from the corresponding station table entries. The receive table pointer register then contains the address of the first receive frame specification block. The XPC accesses the receive frame specification block to load the receive buffer function code, receive buffer address, and the receive buffer length into its internal registers. The XPC then presents the receive buffer address and function code to the system to store the received information field in the memory buffer. After reception of a frame, the XPC writes the number of unused bytes in the final count entry in the current receive frame specification block and updates its internal V(R) register. Next, the XPC sets the receive information frame (RXI) bit in the Rx/host status register. The XPC accesses the next receive frame specification block to store incoming frames until reaching the end of the receive frame specification table.

To decrease the possibility of a receive-not-ready condition due to a lack of available receive buffers, a method is provided for linking receive frame specification tables. When the end of table (EOT) bit is set in a receive frame specification block, the XPC inspects the link bit value. If the link bit is set, then the XPC loads the receive table pointer and function code registers from the cor-

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

responding station table locations. The XPC then sets the receive table ended (RTE) bit in the Rx/host status register and issues an interrupt if enabled. The link operation can be used to implement a cyclical queue by using the original receive table pointer and function code values in the station table. However, the user must read filled receive buffers expediently to ensure that the XPC does not overwrite the buffers with incoming frames.

#### **COMMAND SET**

The host processor issues commands to the XPC to perform various functions by writing to the XPC command register. There are 23 commands that fall in the following four categories:

- 1. Initialization

- 2. Table Handling

- 3. Link Handling

- 4. Test/Diagnostics

#### INITIALIZATION COMMANDS

Initialization commands configure the XPC for operation after a hardware or software reset. The four initialization commands specify various system attributes, communication protocol options, and the location of the station table in memory.

#### Reset

The RESET command and hardware reset causes the following actions:

- Reset the Receive Channel and Isolate RxD

- Reset the Transmit Channel, Negate RTS, and Transmit Ones

- Immediately Relinquish the System Bus

- Set the Interrupt Vector Register to \$0F

- Disable Transmit and Receive Memory Buffers

- Clear All Rx/Host and Tx/Link Status Bits

- Clear All Hardware and Station Configuration Bits

- Clear All Option Bits

- Clear All Mode Descriptor and Frame Reject Descriptor Bits

- Zero Station Table Pointer and Station Table Function Code Registers

- Zero Transmit Table Pointer and Transmit Table Function Code Registers

- Zero Receive Table Pointer and Receive Table Function Code Registers

- Zero Remote Address and Local Address Registers

- Zero V(R), V(S), and Last Received N(R) Registers

- Zero Preset Values and Retries Count Register

M68000 FAMILY REFERENCE MANUAL

## **Set Station Configuration**

The SET STATION CONFIGURATION command specifies protocol parameters. The command has the following format:

| 7 | 6 | 5 | 4 | 3    | 2 | 1    | 0 |

|---|---|---|---|------|---|------|---|

| 1 | 0 | 1 | 0 | ECRC | 0 | ECNT | 0 |

ECRC — Extended CRC

0 = 16-Bit CRC

CRC CCITT  $(X^{16} + X^{12} + X^5 + 1)$

1 = 32-Bit CRC

$$(X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + 11 + X^{10} + X^{8} + X^{7} + X^{5} + X^{4} + X^{2} + X^{1} + 1)$$

ECNT — Extended Control

0 = Basic Control Field Format (Modulo 8)

1 = Extended Control Field Format (Modulo 128)

## **Set Hardware Configuration**

The SET HARDWARE CONFIGURATION command defines the data decoding/ encoding scheme, DMA burst control, data organization in memory, and data bus size. The format of the command is as follows:

| 7 | 6 | 5 | 4    | 3    | 2 | 11    | 0    |

|---|---|---|------|------|---|-------|------|

| 1 | 1 | 0 | NRZI | BRSC | 0 | DORGM | BUSW |

NRZI — Non-Return to Zero Invert

0 = NRZ Decoding/Encoding

1 = NRZI Decoding/Encoding

BRSC — Burst Control

0 = DMA Burst is Unlimited

1 = DMA Burst is Limited to Eight Successive Memory Cycles

DORGM - Data Organization in Memory for a 16-Bit Data Bus System

- 0 = Data in Memory is Organized with High-Order Byte in Lower Memory Address (Motorola and IBM® Convention)

- 1 = Data in Memory is Organized with Low-Order Byte in Lower Memory Address (DEC® and Intel® Convention)

(This capability is available only for I-frame buffers and not for parameters or tables.)

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

8-65

۶

BUSW — Bus Width 0 = 8-Bit Data Bus 1 = 16-Bit Data Bus

#### **Load Function Code**

The LOAD FUNCTION CODE command writes the function code value in the data register into the station table function code register. This command is issued after the host processor has written the function code to the data register.

#### **Load Station Table Pointer**

The LOAD STATION TABLE POINTER command writes the station table address from the data register into the station table pointer register. This command is issued after the host processor has written the station table pointer to the data register.

#### **TABLE HANDLING COMMANDS**

The 11 table handling commands cause the XPC to access the station table, transmit frame specification table, or receive frame specification table.

## **Load Option Bits**

The LOAD OPTION BITS command loads the option set from the station table into the option bits register.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8      |

|----|----|----|----|----|----|---|--------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | X.75   |

| 7  | 6  | 5  | 4  | 3  | 2  | 1 | 0      |

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | CRCNOA |

X.75 — X.75 Option

0 = X.25 Operation

1 = X.75 Operation

IBM is a trademark of International Business Machines. DEC is a trademark of Digital Equipment Corporation. Intel is a trademark of Intel Corporation.

M68000 FAMILY REFERENCE MANUAL

MOTOROLA

#### CRCNOA — CRC Bypass Option

- 0 = Non-octet aligned frames or frames with a CRC error are not accepted.

- 1 = Non-octet aligned frames or frames with a CRC error are accepted.

#### **Load Addresses**

The LOAD ADDRESSES command loads the local and remote addresses from the station table into the internal XPC registers. After these registers are loaded, the XPC is ready to establish the link. The XPC monitors the receive line and transmits continuous flags.

#### **Load Preset Values**

The LOAD PRESET VALUES command loads the time-out preset value, time scale divider, pad time select, outstanding frames limit, and retries limit from the station table into the respective XPC internal registers.

#### **Load Transmit Table Pointer**

The LOAD TRANSMIT TABLE POINTER command loads the transmit table pointer and the transmit table function code from the station table into the corresponding XPC registers and enables the transmission of a chain of information frames.

#### **Continue Transmit**

The CONTINUE TRANSMIT command (\$95) is used to extend the transmit queue after adding entries to the transmit frame specification table. The user should set EOT in the transmit status location of the last added entry and then clear EOT at the previous end of table. Finally, the user should issue the CONTINUE TRANSMIT command to the XPC. This command is useful in the case where the XPC has already detected the previous EOT and will not read a new table entry. Instead, it is waiting for all transmitted frames to be acknowledged; during this period, it will not accept a new load transmit table pointer command.

#### **Load Receive Table Pointer**

The LOAD RECEIVE TABLE POINTER command loads the receive table pointer and the receive table function code from the station table into the corresponding XPC registers and enables the reception of information frames.

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

#### **Load Station Parameters**

The LOAD STATION PARAMETERS command combines the load option bits, load preset values, and load addresses commands.

#### **Update Status**

The UPDATE STATUS command allows the host to request current XPC status information.

#### Clear Tx/Link Status

The CLEAR Tx/LINK STATUS command clears the status bits in the Tx/link status register as specified by the Tx/link status clear bits in the station table.

#### Clear Rx/Host Status

The CLEAR Rx/LINK STATUS command clears the Rx/host status register as specified by the Rx/host status clear bits in the station table.

#### Clear Status

The CLEAR STATUS command clears both the Tx/link and Rx/host status bits in the respective XPC registers as specified by the Tx/link status clear bits and the Rx/host status clear bits in the station table.

## **Dump Parameters**

The DUMP PARAMETERS command writes the following XPC parameters into the corresponding status table locations in the order given: Rx/host status, Tx/link status, mode descriptor, frame reject descriptor, V(R), V(S), first unacknowledged transmit block function code and pointer, next transmit block function code and pointer, and next receive block function code and pointer.

#### LINK HANDLING COMMANDS

The two link handling commands cause the XPC to set the link to a new operation mode and to automatically handle communication on both channels according to the predefined configuration and option bits.

8-68

**M68000 FAMILY REFERENCE MANUAL**

#### Start Link

The START LINK command initiates the link setup procedure.

### Stop Link

The STOP LINK command initiates the link disconnect procedure.

#### TEST/DIAGNOSTICS

The five commands in the text/diagnostics category test the XPC circuit and run diagnostics on the link.

### **Dump Registers**

The DUMP REGISTERS command writes the XPC registers to a user-specified dump area in external memory.

#### **DMA Transfer**

The DMA TRANSFER command tests the handling of parallel data. The XPC reads the data from a transmit memory buffer and writes it to a receive memory buffer. The XPC transfers data from the transmit buffer to the receive buffer via the data register without using the internal transmit or receive FIFOs. The serial link is not affected by this operation.

## **Serial Loopback**

The SERIAL LOOPBACK command tests the handling of parallel and serial data. The XPC reads data from the transmit memory buffer into the transmit FIFO. The data is then serialized and shifted internally into the receive FIFO and onto the TxD line. Finally, the data is stored in the receive memory buffer. RTS is not active during serial loopback.

#### **Monitor**

The MONITOR COMMAND allows the XPC to check the communication channel by reading/writing the entire frame from/to memory. The monitor command may be used to perform an external loopback test of the system or to implement any HDLC/SDLC operation mode where all frames are user generated. The XPC transmits and/or receives multiple information frames using the transmit and receive frame specification tables until receiving an end monitor command.

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

The user places the address, control, and data (if any) fields in each transmit buffer. The XPC only provides framing, zero insertion, and CRC for each frame. On the receive side, the XPC strips off flags, handles zero deletion, and writes the address, control and data fields into the receive buffer. The received CRC is also appended to the end of each memory buffer and is verified by the XPC.

#### **End Monitor**

The END MONITOR command terminates the monitor command.

# XPC IMPLEMENTATION OF LAPB PROTOCOL

#### INITIALIZATION PROCEDURE

The XPC enters the initialization procedure as the result of a hardware or software reset. During this initialization, the station table address and function code, system configuration information, and XPC interrupt vector are loaded by the XPC under the direction of the host, as shown in the following sample program. Internal XPC registers directly accessed during the initialization procedure are the command register (CR), data register (DR), interrupt vector register (IV), and semaphore register (SR).

#### RESET

Repeat: Read Semaphore Register Until It Is FF

Write CR: Set Hardware Configuration

Repeat: Read Semaphore Register Until It Is FF

Write CR: Set Station Configuration

Repeat: Read Semaphore Register Until It Is FF

Write DR: 4-Bit Function Code Value for Station Table Access

Write CR: Load Function Code

Repeat: Read Semaphore Register Until It Is FF

Write DR: 32-Bit Address of Station Table

Write CR: Load Station Table Pointer

Repeat: Read Semaphore Register Until It Is FF

Write IV: Load Interrupt Vector

Write CR: Load Station Table Parameters

Repeat: Read Semaphore Register Until It Is FF

M68000 FAMILY REFERENCE MANUAL

#### NOTE

The XPC will not come out of hardware or software reset without the system clock and the transmit clock. The transmit clock is used to initialize the serial section of the chip.

#### INFORMATION FRAME TRANSMISSION

After the XPC enters ABM or ABME, the host processor can instruct the XPC to transmit a chain of information frames by issuing the LOAD TRANSMIT TABLE POINTER command. In response, the XPC loads the transmit table pointer and the transmit table function code from the station table into its internal registers. Next, the XPC loads the first transmit buffer pointer, transmit buffer function code, and transmit buffer count from the transmit frame specification table into the corresponding XPC registers. The XPC is now ready to build the first frame.

The remote address is copied from the remote address register into the XPC transmit FIFO. Next the control field is generated and placed in the FIFO. The information field pointed to by the transmit buffer pointer register is then read from the memory buffer into the transmit FIFO until the transmit buffer count is satisfied. A frame check sequence is attached to complete the frame. Zero insertion is performed throughout the transmission. After frame transmission, V(S) is updated and timer T1 is started (if it is not already running) to determine when the programmed time period permitted for a reply to be received has elapsed.

This transmission sequence repeats for each frame until the end of the transmit chain is reached or until the outstanding frames limit is reached. The XPC continues to transmit any available information frames even when the XPC receiver is in the busy condition. The XPC prematurely terminates frame transmission if a link command interrupts the information frame transmission or an error condition arises.

Transmission begins when six bytes are present in the transmit FIFO. Transmission can begin when less than six bytes are present in the FIFO if the entire frame is less than six bytes in length. Between frames, the XPC transmits the user-selected number of pad flags. Additional flags are transmitted if the required number of bytes are not present in the transmit FIFO. While transmitting an information frame, the XPC requests the bus when there are at least six empty bytes in the transmit FIFO unless the last byte of the frame has been loaded into the FIFO.

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

The host processor enables information reception by instructing the XPC to LOAD RECEIVE TABLE POINTER. The XPC will load the receive table pointer and function code into its internal registers. Next, the receive buffer pointer, receive buffer, function code, and the receive buffer count are loaded into the corresponding XPC registers. The XPC is now ready to receive information (I) frames.

The address field of an incoming I-frame is compared to the local address register and the remote address register. If the address does not match the local or remote address, the frame is ignored. If the address field matches the remote address, a frame reject (FRMR) is transmitted and the invalid or unimplemented control field (W) bit of the frame reject descriptor (FRD) register is set. If the address field matches the local address, the frame is accepted by the XPC, and the received N(R) acknowledges previously transmitted I-frames.

Next, the send sequence number, N(S), of the incoming frame is compared to the XPC internal receive state variable, V(R). If the frame is in sequence, then the information field is transferred through the receive FIFO to the receive memory buffer. Out-of-sequence frames are rejected.

Lastly, the XPC performs a CRC check on the incoming information frame. If an error-free frame is received, the XPC acknowledges the frame reception with a supervisory frame (receive ready, RR, or receive not ready, RNR) or with an updated receive sequence number, N(R), in the next information frame.

Zero deletion is performed throughout the reception process. The XPC requests the bus when six bytes are present in the receive FIFO. Only a single frame can reside in the receive FIFO. Frames are received in sequence as long as memory buffers are available.

## **XPC STATE DIAGRAM**

The XPC state diagram (see Figure 7) is a detailed description of the XPC implementation of the LAPB procedure. The state diagram defines the various XPC states based on command frames received (no errors), response frames received (no errors), and miscellaneous inputs received. For example, if the command received was an RR with the poll bit set to one while in the remote station busy condition (state 9), then the XPC responds with an RR with the final bit set to a one and changes to information transfer (state 5).

8-72

M68000 FAMILY REFERENCE MANUAL

| STATE                                                                    | I FRAME<br>WITH    | I FRAME<br>W/O POLL | RR<br>WITH           | RR<br>W/O POLL      | REJ<br>WITH<br>POLL  | REJ<br>W/O POLL    | RNR<br>WITH<br>POLL  | RNR<br>W/D POLL       | SABM<br>WITH OR<br>W/O POLL | DISC.<br>WITH OR<br>W/O POLL |

|--------------------------------------------------------------------------|--------------------|---------------------|----------------------|---------------------|----------------------|--------------------|----------------------|-----------------------|-----------------------------|------------------------------|

| S1<br>DISCONNECTED                                                       | POLL DM, F = 1     | _                   | POLL DM, F = 1       | _                   | DM, F = 1            | _                  | DM, F = 1            |                       | UA, F = P<br>TO S5          | DM, F=P                      |

| S2<br>LINK SETUP                                                         |                    | _                   |                      | _                   | _                    |                    |                      | _                     | UA, F = P                   | DM, F= P<br>T0 S1            |

| S3<br>FRAME REJECT                                                       | FRMR,<br>F = 1     | FRMR,<br>F=0        | FRMR,<br>F = 1       | FRMR,<br>F = 0      | FRMR,<br>F = 1       | FRMR,<br>F = 0     | FRMR,<br>F = 1       | FRMR,<br>F=0          | UA, F = P<br>TO S5          | UA, F = P<br>TO S1           |

| S4<br>DISCONNECT<br>REQUEST                                              | _                  | _                   | _                    | _                   | _                    | -                  | _                    | _                     | DM, F = P<br>TO S1          | UA, F=P                      |

| S5<br>INFORMATION<br>TRANSFER                                            | RR, F = 1          | **                  | RR, F = 1            | **                  | RR, F=1              | **                 | RR, F = 1<br>TO S9   | RR, F = 0<br>TO S9    | UA, F = P                   | UA, F=P<br>TO \$1            |

| S6<br>REJ FRAME<br>SENT                                                  | RR, F = 1<br>TO S5 | **<br>TO S5         | RR, F=1              | **                  | RR, F = 1            | **                 | RR, F = 1<br>TO S14  | RR, F = 0<br>TO S14   | UA, F = P<br>TO \$5         | UA, F = P<br>TO S1           |

| S7<br>WAITING   FRAME<br>ACKNOWLEDGE-<br>MENT                            | RR, F = 1          | RR, F=0             | RR, F = 1            | RR, F=0             | RR, F = 1            | RR, F = 0          | RR, F = 1<br>TO S12  | RR, F = 0<br>TO \$12  | UA, F = P<br>TO S5          | UA, F = P<br>TO \$1          |

| S8<br>STATION<br>BUSY                                                    | RNR, F = 1         | RNR, F = 0          | RNR, F = 1           | *N                  | RNR, F = 1           | *N                 | RNR, F = 1<br>TO S10 | RNR, F = 0<br>TO \$10 | UA, F = P                   | UA, F=P<br>TO S1             |

| S9<br>REMOTE<br>STATION BUSY                                             | RR, F = 1          | RR, F=0             | RR, F = 1<br>TO \$5  | **<br>TO S5         | RR, F = 1<br>TO S5   | 70 S5              | RR, F = 1            | RR, F=0               | UA, F = P<br>TO \$5         | UA, F = P<br>TO S1           |

| S10<br>BOTH STATIONS<br>BUSY                                             | RNR, F = 1         | RNR, F=0            | RNR, F=1<br>TO S8    | *N<br>TO S8         | RNR, F = 1<br>TO S8  | *N<br>TO \$8       | RNR, F = 1           | RNR, F = 0            | UA, F = P<br>TO S8          | UA, F = P<br>TO S1           |

| S11<br>WAITING I FRAME<br>ACKNOWLEDGE-<br>MENT AND STA-<br>TION BUSY     | RNR, F = 1         | RNR, F=0            | RNR, F=1             | RNR, F = 0          | RNR, F = 1           | RNR, F = 0         | RNR, F = 1<br>TO S13 | RNR, F=0<br>TO S13    | UA, F = P<br>TO \$8         | UA, F = P<br>TO S1           |

| S12 WAITING I FRAME ACKNOWLEDGE- MENT AND RE- MOTE STATION BUSY          | RR, F=1            | RR, F=0             | RR, F=1<br>TO S7     | RR, F=0<br>TO S7    | RR, F = 1<br>TO S7   | RR, F=0<br>TO S7   | RR, F=1              | RR, F=0               | UA, F = P<br>TO S5          | UA, F=P<br>TO S1             |

| S13<br>WAITING I FRAME<br>ACKNOWLEDGE-<br>MENT AND BOTH<br>STATIONS BUSY | RNR, F = 1         | RNR, F = 0          | RNR, F = 1<br>TO S11 | RNR, F=0<br>TO \$11 | RNR, F = 1<br>TO S11 | RNR, F=0<br>TO S11 | RNR, F = 1           | RNR, F = 0            | UA, F=P<br>TO S8            | UA, F = P<br>TO S1           |

| S14<br>REJ FRAME SENT<br>AND REMOTE<br>STATION BUSY                      | RR, F = 1<br>TO S9 | RR, F=0<br>TO S9    | RR, F = 1<br>TO S6   | TO S6               | RR, F=1<br>TO S6     | **<br>TO S6        | RR, F = 1            | RR, F = 0             | UA, F = P<br>TO S5          | UA, F = P<br>TO \$1          |

<sup>\*\*</sup> If I available then Tx I frame else Tx RR, F = 0

Figure 7. XPC State Diagram

**MOTOROLA** M68000 FAMILY REFERENCE MANUAL

<sup>\*\*</sup> If I available then Tx I frame else Tx RR, F=0

\*\* If I available then Tx I frame else do nothing

\*N If I available then Tx I frame else Tx RNR, F=0

\*\*N If F=1 then Tx RNR, F=1 else if I available then Tx I frame else Tx RNR, F=0

\*\*N If P=1 then Tx FRMR, F=1 else if P=0 then Tx FRMR, F=0 else do nothing

\*DM If P=1 then Tx DM, F=1 else do nothing

\*J If no REJ FRAME is outstanding then transmit REJ, F=P else if P=1 then Tx RR, F=1 else do nothing

\*\*J If the I field of a correctly received frame has been discarded (due to the busy condition) then Tx REJ, F=0 else Tx RR, F=0

\*\*Parallel Standard Standar

<sup>--</sup> Do nothing

X This event never occurs in this state

UNXF Unexpected final bit

| STATE                                                                          | RR<br>WITH<br>FINAL     | RR<br>W/O<br>FINAL | REJ<br>WITH<br>FINAL    | REJ<br>W/O<br>FINAL | RNR<br>WITH<br>FINAL    | RNR<br>W/0<br>FINAL | UA WITH<br>OR W/O<br>FINAL | DM<br>WITH<br>FINAL | DM<br>W/O<br>FINAL | FRMR<br>WITH OR<br>W/O FINAL | LOCAL<br>START<br>COMMAND |

|--------------------------------------------------------------------------------|-------------------------|--------------------|-------------------------|---------------------|-------------------------|---------------------|----------------------------|---------------------|--------------------|------------------------------|---------------------------|

| S1<br>DISCONNECTED                                                             | -                       | _                  | _                       | _                   | _                       | -                   |                            | SABM<br>TO \$2      | SABM<br>TO S2      | _                            | SABM<br>TO S2             |

| S2<br>LINK SETUP                                                               | _                       | _                  | -                       | _                   | -                       | _                   | TO S5                      | TO \$1              |                    | _                            | x                         |

| S3<br>FRAME REJECT                                                             | _                       | _                  | _                       | _                   | -                       | _                   | _                          | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S4<br>DISCONNECT<br>REQUEST                                                    | _                       | _                  | _                       | _                   | _                       | _                   | TO S1                      | TO S1               | _                  | _                            | х                         |

| S5<br>INFORMATION<br>TRANSFER                                                  | (UNXF)<br>SABM<br>TO S2 | ***                | (UNXF)<br>SABM<br>TO S2 | ***                 | (UNXF)<br>SABM<br>TO S2 | TO S9               | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S6<br>REJ FRAME<br>SENT                                                        | (UNXF)<br>SABM<br>TO S2 | ***                | (UNXF)<br>SABM<br>TO S2 | ***                 | (UNXF)<br>SABM<br>TO S2 | TO S14              | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S7<br>WAITING I FRAME<br>ACKNOWLEDGE-<br>MENT                                  | ***<br>TO \$5           | _                  | ***<br>TO S5            | -                   | TO S9                   | TO S12              | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S8<br>STATION<br>BUSY                                                          | (UNXF)<br>SABM<br>TO S2 | ***                | (UNXF)<br>SABM<br>S2    | ***                 | (UNXF)<br>SABM<br>TO S2 | TO S10              | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO \$2     | SABM<br>TO S2                | SABM<br>TO S2             |

| S9<br>REMOTE<br>STATION BUSY                                                   | (UNXF)<br>SABM<br>TO S2 | ***<br>TO S5       | (UNXF)<br>SABM<br>TO S2 | ***<br>TO S5        | (UNXF)<br>SABM<br>TO S2 | _                   | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S10<br>BOTH STATIONS<br>BUSY                                                   | (UNXF)<br>SABM<br>TO S2 | ***<br>TO S8       | (UNXF)<br>SABM<br>TO S2 | ***<br>TO S8        | (UNXF)<br>SABM<br>TO S2 | _                   | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| STI<br>WAITING I FRAME<br>ACKNOWLEDGE-<br>MENT AND STA-<br>TION BUSY           | ***<br>TO S8            | _                  | ***<br>TO S8            |                     | TO \$10                 | TO \$13             | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S12<br>WAITING I FRAME<br>ACKNOWLEDGE-<br>MENT AND RE-<br>MOTE STATION<br>BUSY | ***<br>T0 S5            | _<br>TO \$7        | ***<br>TO S5            | TO \$7              | TO S9                   |                     | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S13<br>WAITING I FRAME<br>ACKNOWLEDGE-<br>MENT AND BOTH<br>STATIONS BUSY       | ***<br>T0 S8            | TO S11             | ***<br>TO S8            | TO S11              | TO \$10                 | _                   | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

| S14<br>REJ FRAME SENT<br>AND REMOTE<br>STATION BUSY                            | (UNXF)<br>SABM<br>TO S2 | TO \$6             | (UNXF)<br>SABM<br>TO S2 | ***<br>TO S6        | (UNXF)<br>SABM<br>TO S2 |                     | SABM<br>TO S2              | SABM<br>TO S2       | SABM<br>TO S2      | SABM<br>TO S2                | SABM<br>TO S2             |

Figure 7. XPC State Diagram (Continued)

8-74

M68000 FAMILY REFERENCE MANUAL

| STATE                                                                          | LOCAL<br>STOP<br>COMMAND | STATION<br>BECOMES<br>BUSY | BUSY<br>CONDITION<br>CLEAR | T1<br>EXPIRES        | N2×T1<br>1S<br>EXCEEDED | NS<br>SEQUENCE<br>ERROR  | INVALID<br>NR<br>RECEIVED | UNRECOGNIZED<br>FRAME<br>RECEIVED |

|--------------------------------------------------------------------------------|--------------------------|----------------------------|----------------------------|----------------------|-------------------------|--------------------------|---------------------------|-----------------------------------|

| S1<br>DISCONNECTED                                                             | DISC<br>TO S4            | х                          | _                          | x                    | х                       | *DM                      | *DM                       | *DM                               |

| S2<br>LINK SETUP                                                               | х                        | х                          | _                          | SABM                 | TO S1                   | -                        |                           |                                   |

| S3<br>FRAME REJECT                                                             | DISC<br>TO S4            | х                          | -                          | FRMR<br>F = 0        | SABM<br>TO S2           | *FR                      | *FR                       | *FR                               |

| S4<br>DISCONNECT<br>REQUEST                                                    | х                        | х                          | _                          | DISC                 | TO \$1                  | -                        | _                         | _                                 |

| S5<br>INFORMATION<br>TRANSFER                                                  | DISC<br>TO S4            | RNR, F = P<br>TO S8        | х                          | RR, P = 1<br>TO S7   | SABM<br>TO S2           | *J<br>TO \$6             | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S6<br>REJ FRAME<br>SENT                                                        | DISC<br>TO S4            | RNR, F = P<br>TO S8        | x                          | RR, P = 1<br>TO S7   | SABM<br>TO S2           | IF P = 1<br>Tx RR, F = 1 | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S7<br>WAITING I FRAME<br>ACKNOWLEDGE-<br>MENT                                  | DISC<br>TO S4            | RNR, F = P<br>TO S11       | x                          | RR, P = 1            | SABM<br>TO S2           | *J                       | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S8<br>STATION<br>BUSY                                                          | DISC<br>TO S4            | х                          | **J<br>TO S5               | RNR, P = 1<br>TO S11 | SABM<br>TO S2           | RNR, F = P               | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S9<br>REMOTE<br>STATION BUSY                                                   | DISC<br>TO S4            | RNR, F = P<br>TO S10       | х                          | RR, P = 1<br>TO \$12 | SABM<br>TO S2           | *J<br>TO \$14            | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO \$3                 |

| S10<br>BOTH STATIONS<br>BUSY                                                   | DISC<br>TO S4            | x                          | **J<br>TO S9               | RNR, P=1<br>TO S13   | SABM<br>TO \$2          | RNR, F≃P                 | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S11<br>WAITING I FRAMI<br>ACKNOWLEDGE-<br>MENT AND STA-<br>TION BUSY           | DISC<br>TO S4            | x                          | **J<br>T0 S7               | RNR, P = 1           | SABM<br>TO S2           | RNR, F = P               | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S12<br>WAITING I FRAMI<br>ACKNOWLEDGE-<br>MENT AND RE-<br>MOTE STATION<br>BUSY | DISC<br>TO S4            | RNR, F = F<br>TO S13       | х                          | RR, P = 1            | SABM<br>TO S2           | *J                       | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S13<br>WAITING   FRAM<br>ACKNOWLEDGE-<br>MENT AND BOTH<br>STATIONS BUSY        | TO SA                    | x                          | **J<br>TO S12              | RNR, P=1             | SABM<br>TO S2           | RNR, F = P               | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO S3                  |

| S14<br>REJ FRAME SENT<br>AND REMOTE<br>STATION BUSY                            | DISC<br>TO S4            | RNR, F= F<br>TO S10        | x                          | RR, P = 1<br>TO S12  | SABM<br>TO S2           | IF P = 1<br>Tx RR, F =   | FRMR(Z)<br>TO S3          | FRMR(W)<br>TO \$3                 |

Figure 7. XPC State Diagram (Concluded)

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

# XPC TRANSPARENT MODE OF OPERATION

The XPC transparent mode of operation can be used to implement a variety of bit-oriented protocols. The following paragraphs describe the XPC transparent mode of operation.

#### **INITIALIZATION PROCEDURE**

The XPC enters the initialization procedure as the result of a hardware or software reset. During initialization, the station table address and function code, system configuration information, and the XPC interrupt vector should be loaded by the XPC under the direction of the host. Note that the XPC will not come out of hardware or software reset without the system clock and the transmit clock. The transmit clock is used to initialize the serial section of the chip.

#### **ENTERING TRANSPARENT OPERATION**

Transparent operation is entered when the host issues the MONITOR command. After the monitor command, the XPC asserts RTS, transmits flags, and monitors RxD. Since handshaking between nodes is not possible before the monitor command is executed, the host processor at each node must issue the monitor command to enable communication between the two nodes.

## FRAME TRANSMISSION

After the MONITOR command is issued, the XPC begins transmission of frames only after receiving a LOAD TRANSMIT TABLE POINTER command from the host. All frames are user generated and may contain user-provided address, control, and/or data fields. After the host issues the LOAD TRANSMIT TABLE POINTER command, the XPC loads the transmit table pointer and the transmit table function code from the station table into its internal registers. Next, the XPC loads the first transmit buffer pointer, transmit buffer function code, and transmit buffer count from the transmit frame specification table into the corresponding XPC registers. The XPC is now ready to transmit the first frame.

The frame pointed to by the transmit buffer pointer register is read from the memory buffer into the transmit FIFO until the transmit buffer count is satisfied. An XPC-generated frame check sequence is then attached to complete the frame. After each frame transmission, the internal V(S) register is incremented without regard to the frame type. This transmission sequence repeats for each frame until the end of the transmit chain is reached. Zero insertion is performed throughout the transmission process.

8-76

M68000 FAMILY REFERENCE MANUAL

In transparent operation, the XPC transmits frames until the end of the transmit specification table is reached. After the last frame is transmitted, the XPC sets the IFAK bit in the Tx/link status register to indicate the end of the transmit table. The XPC does not analyze any incoming frames for acknowledgements or link control information during transparent operation. The only errors reported in the Tx/link status register are address error, bus error, clear-to-send lost, and underrun.

Transmission begins when six bytes are present in the transmit FIFO. Transmission can begin when less than six bytes are present in the FIFO if the entire frame is less than six bytes in length. Between frames, the XPC transmits the user-selected number of pad flags. Additional pad flags are transmitted if the required number of bytes are not present in the transmit FIFO for transmission to begin. While transmitting a frame, the XPC requests the bus when there are at least six empty bytes in the transmit FIFO unless the last byte of the frame has been loaded into the FIFO.

#### FRAME RECEPTION

The host processor enables frame reception by instructing the XPC to LOAD RECEIVE TABLE POINTER. The XPC then loads the receive table pointer and function code into its internal registers. Next, the receive buffer pointer, receive buffer function code, and the receive buffer count are loaded into the corresponding XPC registers. The XPC is now ready to receive frames.

The XPC does not analyze the address and control fields of incoming frames but does perform a CRC check on incoming frames. After the flags are stripped off, the entire frame, including CRC, is written into the current receive buffer, and the RXI bit is set in the Rx/host status register. If a frame is received with a CRC error, the XPC sets the E-bit in that frame's receive specification block. After a frame is received, the XPC increments V(R) without regard to frame type. Zero deletion is performed throughout the reception process.

In transparent operation, the XPC continues to receive frames until the end of the receive specification table is reached. The XPC then sets the RTE bit in the Rx/host status register.

The XPC requests the bus when there are six bytes in the receive FIFO. Only a single frame can reside in the receive FIFO. Frames are received in sequence as long as memory buffers are available.

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

## SIGNAL DESCRIPTION

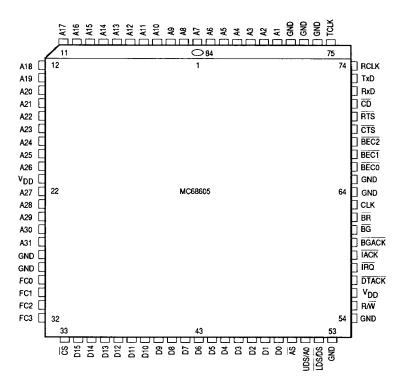

The input and output signals can be functionally organized into the groups shown in Figure 8.

Figure 8. Functional Signal Groups

8-78

## **ELECTRICAL SPECIFICATIONS**

#### **MAXIMUM RATINGS**

| Rating                                             | Symbol           | Value              | Unit |

|----------------------------------------------------|------------------|--------------------|------|

| Supply Voltage                                     | $V_{DD}$         | -0.3 to +7.0       | V    |

| Input Voltage                                      | Vin              | -0.3  to  +7.0     | V    |

| Operating Temperature Range<br>MC68605<br>MC68605I | ТА               | 0 to 70<br>0 to 85 | °C   |

| Storage Temperature Range                          | T <sub>stg</sub> | - 55 to +150       | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximumrated voltages to this highimpedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or VDD).

#### THERMAL CHARACTERISTICS

| Characteristic                                         | Symbol | Value     | Unit |

|--------------------------------------------------------|--------|-----------|------|

| Thermal Resistance for PGA Thermal Resistance for PLCC | θJΑ    | 33<br>TBD | °C/W |

$$TJ = TA + (PD \cdot \theta JA)$$

$$PD = (VDD \cdot IDD) + PI/O$$

where:

PI/O is the power dissipation on pins (user determined) which can be neglected in most cases.

For  $T_A = 70^{\circ}\text{C}$  and  $P_D = 0.55 \text{ W}$  @ 12.5 MHz,  $T_J = 88^{\circ}\text{C}$

#### **POWER CONSIDERATIONS**

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{1}$$

where:

T<sub>A</sub> = Ambient Temperature, °C

θ<sub>IA</sub> = Package Thermal Resistance, Junction-to-Ambient, °C/W

$P_D = P_{INT} + P_{PORT}$

$P_{INT} = I_{DD} \times V_{DD}$ , Watts — Chip Internal Power

$P_{I/O}$  = Power Dissipation on Input and Output Pins, Watts — User Deter-

mined

For most applications PI/O < PINT and can be neglected.

If

$$P_{I/O}$$

is neglected, an approximate relationship between  $P_D$  and  $T_J$  is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

(2)

MOTOROLA

M68000 FAMILY REFERENCE MANUAL

$$K = P_D \cdot (T_A + 273^{\circ}C) + \theta JA \cdot P_D^2$$

(3)

where K is a constant pertaining to the particular part. K can be determined from Equation (3) by measuring PD (at equilibrium) for a known TA. Using this value of K, the values of PD and TJ can be obtained by solving Equations (1) and (2) iteratively for any value of TA.

## DC ELECTRICAL CHARACTERISTICS

All specifications are valid under the following conditions:  $V_{DD} = 4.75 \text{ V}$  to 5.25 V,  $V_{SS} = 0 \text{ V}$ ,  $T_A = T_L$  to  $T_H$  and 130 pF total capacitance on output pins.

| Characteristic                                                                                                                                                                                                                                                                                                | Symbol          | Min                   | Max                  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|----------------------|------|

| Input High Voltage (Except System Clock)                                                                                                                                                                                                                                                                      | ViH             | 2.0                   | V <sub>DD</sub>      | V    |

| Input Low Voltge (Except System Clock)                                                                                                                                                                                                                                                                        | VIL             | V <sub>SS</sub> - 0.3 | 0.8                  | V    |

| Input High Voltage (System Clock)                                                                                                                                                                                                                                                                             | VCIH            | 2.4                   | V <sub>DD</sub>      | V    |

| Input Low Voltage (System Clock)                                                                                                                                                                                                                                                                              | VCIL            | V <sub>SS</sub> - 0.3 | 0.5                  | V    |

| Input Leakage Current                                                                                                                                                                                                                                                                                         | lin             | _                     | 20                   | μА   |

| Input Capacitance                                                                                                                                                                                                                                                                                             | C <sub>in</sub> | _                     | 13                   | pF   |

| Three-State Leakage Current (2.4/0.5 V)                                                                                                                                                                                                                                                                       | †TSI            | _                     | 20                   | μА   |

| Open-Drain Leakage Current (2.4 V)                                                                                                                                                                                                                                                                            | lop             | _                     | 20                   | μА   |

| Output High Voltage (IOH = 400 μA)                                                                                                                                                                                                                                                                            | VOH             | 2.4                   |                      | v    |

| Output Low Voltage (IOL = 3.2 mA) A1-A31, FC0-FC3, $\overline{RTS}$ , $\overline{TXD}$ , $\overline{UDS}$ /A0 as A0 (IOL = 5.3 mA) D0-D15, $\overline{AS}$ , $\overline{LDS}$ , $\overline{UDS}$ /A0 as $\overline{UDS}$ , $\overline{DTACK}$ , $\overline{BGACK}$ , $R/W$ $\overline{BR}$ , $\overline{IRO}$ | V <sub>OL</sub> | _<br>_                | 0.5<br>0.5<br>0.5    | ٧    |

| Power Dissipation                                                                                                                                                                                                                                                                                             | PD              |                       | 0.50<br>0.55<br>0.65 | w    |

8

8-80

M68000 FAMILY REFERENCE MANUAL

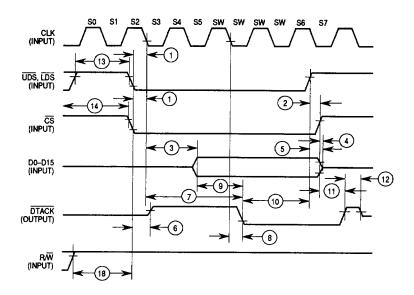

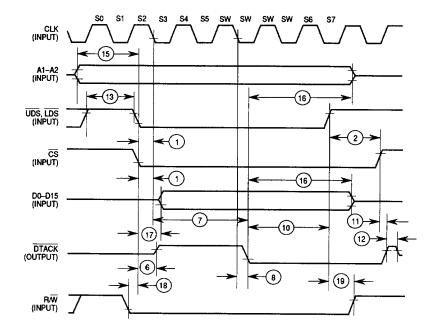

## **AC ELECTRICAL CHARACTERISTICS**

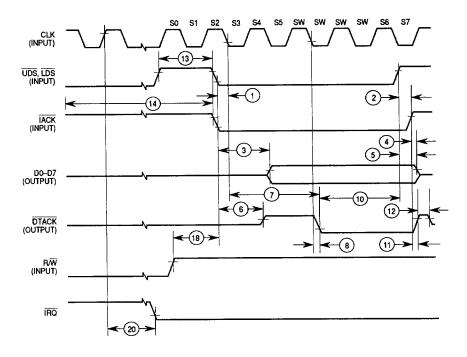

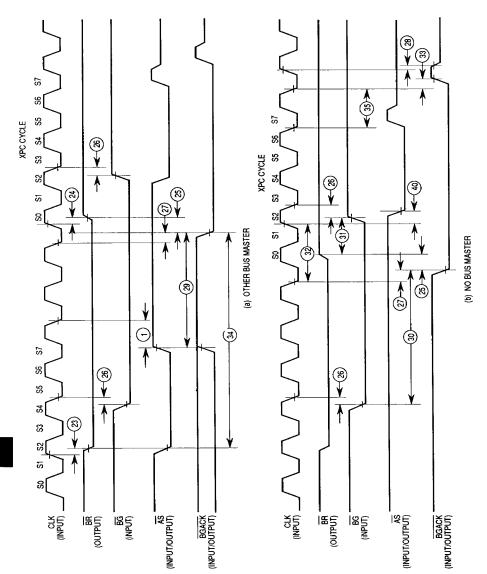

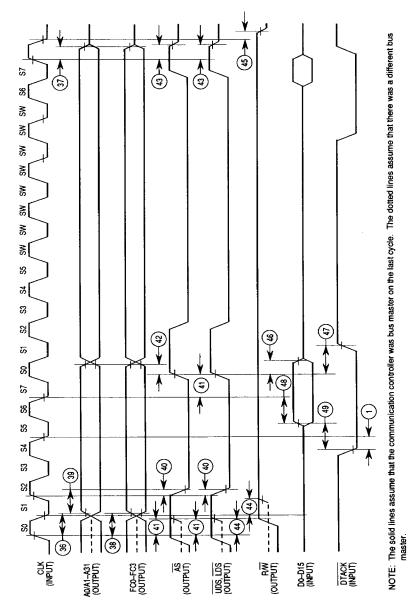

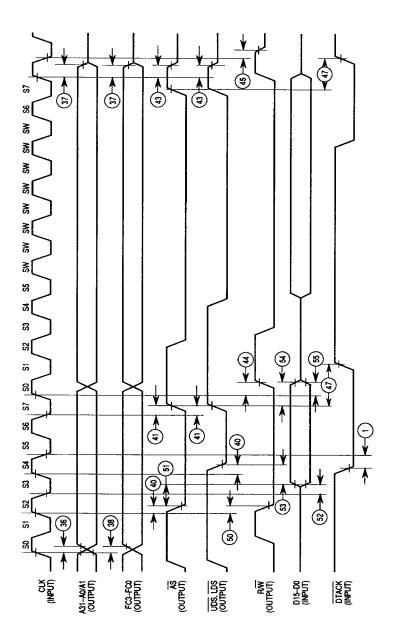

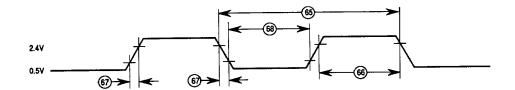

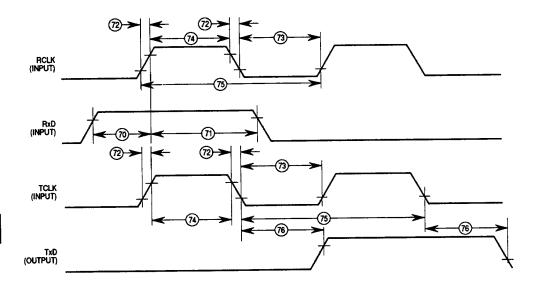

High and low outputs are measured at 2.0 V minimum and 0.8 V maximum, respectively. High and low inputs are driven to 2.4 V and 0.5 V, respectively, for AC test purposes. However, input specifications are still measured from 2.0 V to 0.8 V. All specifications are valid under the following conditions: VDD = 4.75 V to 5.25 V, VSS = 0 V, TA = TL to TH, output load = 130 pF, and output current as specified in **DC ELECTRICAL CHARACTERISTICS**; see Figures 9–20.

|      |                                                                                         | 10 MHz    |              | 12.5 MHz                                     |              | 16.67     |             |                 |  |

|------|-----------------------------------------------------------------------------------------|-----------|--------------|----------------------------------------------|--------------|-----------|-------------|-----------------|--|

| Num. | Characteristic                                                                          | Min       | Max          | Min                                          | Max          | Min       | Max         | Unit            |  |

| 1    | Asynchronous Input Setup Time                                                           |           | _            | 20                                           | _            | 10        |             | ns              |  |

| 2    | UDS, LDS Inactive to CS, IACK Inactive                                                  | _         | 100          | _                                            | 80           | _         | 60          | ns              |  |

| 3    | CLK Low (on which UDS or LDS, CS or IACK Are Recognized) to Data-Out Valid (see Note 5) |           | 1/2<br>+ 150 | _                                            | 1/2<br>+ 120 | _         | 1/2<br>+ 90 | Cik. Per.<br>ns |  |

| 4    | CS or IACK High to Data-Out High Impedance                                              | _         | 60           | _                                            | 50           |           | 35          | ns              |  |

| 5    | LDS/DS High to Data-Out Hold Time (see Note 6)                                          | 0         | -            | 0                                            | -            | 0         |             | ns              |  |

| 6    | IACK or CS Low to DTACK High<br>(Driving Three-State DTACK High)                        | _         | 80           | _                                            | 70           |           | 60          | ns              |  |

| 7    | CLK Low (on which UDS or LDS, CS or IACK are Recognized) to DTACK Low (see Note 5)      |           | 2<br>+ 90    | _                                            | 2<br>+80     | _         | 2<br>+ 50   | Clk. Per.<br>ns |  |

| 8    | CLK Low to DTACK Low                                                                    |           | 90           |                                              | 80           |           | 50          | ns              |  |

| 9    | Data-Out Valid to DTACK Low                                                             | 20        | _            | 20                                           | _            | 20        |             | ns              |  |

| 10   | DTACK Low to UDS, LDS, CS, IACK High (Earliest)                                         | 100       |              | 80                                           |              | 60        |             | ns              |  |

| 11   | CS or IACK or Data Strobes (the Earliest) High to DTACK High (see Note 7)               | ı         | 60           | _                                            | 50           | _         | 40          | ns              |  |

| 12   | DTACK High to DTACK High Impedance<br>(At End of Bus Cycle)                             | _         | 50           |                                              | 50           |           | 40          | ns              |  |

| 13   | UDS, LDS Inactive Time                                                                  | 1         |              | 1                                            |              | 1         |             | Clk. Per.       |  |

| 14   | CS, IACK Inactive Time                                                                  | 0         |              | 0                                            |              | 0         |             | ns              |  |

| 15   | A1-A2 Valid to UDS, LDS, CS (the Latest) Low (Write)                                    | 30        |              | 20                                           |              | 20        |             | ns              |  |

| 16   | DTACK Low to Data and A1-A2 Hold Time                                                   | 100       |              | 80                                           |              | 60        |             | ns              |  |

| 17   | UDS or LDS, CS or IACK (the Latest) Low to Data-In Valid                                | _         | 80           |                                              | 70           | _         | 60          | ns              |  |

| 18   | R/W Valid to UDS or LDS, CS or IACK (Latest) Low                                        | 20        |              | 20                                           |              | 10        |             | ns              |  |

| 19   | UDS, LDS High to R/W High                                                               | 0         |              | 0                                            |              | 0         |             | ns              |  |

| 20   | CLK High to IRQ Low                                                                     |           | 100          |                                              | 80           |           | 60          | ns              |  |

| 21   | Reserved                                                                                |           |              |                                              | <u> </u>     |           | <u> </u>    | ļ               |  |

| 22   | Reserved                                                                                |           |              |                                              |              |           |             |                 |  |

| 23   | CLK High to BR Low                                                                      |           | 60           | <u>↓                                    </u> | 55           |           | 40          | ns              |  |

| 24   | CLK High to BR High Impedance                                                           |           | 55           | <u> </u>                                     | 50           |           | 40          | ns              |  |

| 25   | BGACK Low to BR High Impedance                                                          | 20        |              | 20                                           |              | 10        | <u> </u>    | ns              |  |

| 26   | BG Active Inactive to CLK Low Setup Time                                                | 20        |              | 20                                           |              | 10        | <u> </u>    | ns              |  |

| 27   | CLK Low to BGACK Low                                                                    |           | 60           | <u> </u>                                     | 55           |           | 40          | ns              |  |

| 28   | CLK High to BGACK High Impedance                                                        |           | 45           | <u> </u>                                     | 40           | <u> </u>  | 40          | ns              |  |

| 29   | AS and BGACK High (the Latest) to BGACK Low (When BG is Previously Asserted)            | 2<br>+ 20 | 3<br>+ 80    | 2<br>+ 20                                    | 3<br>+ 70    | 2<br>+ 10 | 3<br>+ 50   | Clk. Per.<br>ns |  |

| 30   | BG Low to BGACK Low (No Other Bus Master)                                               | 2<br>+ 20 | 3<br>+80     | 2<br>+ 20                                    | 3<br>+ 70    | 2<br>+ 10 | 3<br>+ 50   | Clk. Per.       |  |

| 31   | BR High Impedance to BG High                                                            | 0         |              | 0                                            |              | 0         |             | ns              |  |

**MOTOROLA**

M68000 FAMILY REFERENCE MANUAL

## AC ELECTRICAL CHARACTERISTICS (Continued)

| Num. | Characteristic                                                                                                                       | 10          | MHz         | 12.5        | MHz         | 16.67 MHz   |             | T         |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-----------|--|

|      | Characteristic                                                                                                                       | Min Max     |             | Min Ma      |             | Min         | Max         | Unit      |  |

| 32   | Clock on which BGACK Low to Clock on which AS Low                                                                                    | 1.5         | 1.5         | 1.5         | 1.5         | 1.5         | 1.5         | Clk. Per. |  |

| 33   | Clock Low to BGACK High                                                                                                              |             | 55          |             | 50          |             | 40          | ns        |  |

| 34   | CLK on which BR Low to CLK on which BGACK<br>Low (Assuming BG Is Active and BGACK and<br>AS are Inactive for at Least 2 CLK Periods) | 1.5         | 1.5         | 1.5         | 1.5         | 1.5         | 1.5         | Clk. Per. |  |

| 35   | CLK on which AS High to CLK on which BGACK High                                                                                      | _           | 1           | -           | 1           | -           | 1           | Clk. Per. |  |

| 36   | CLK High to Address Valid                                                                                                            | _           | 100         | _           | 80          |             | 60          | ns        |  |

| 37   | CLK High to Address/FC High Impedance                                                                                                | _           | 70          |             | 60          | _           | 50          | ns        |  |

| 38   | CLK High to FC Valid                                                                                                                 | _           | 60          |             | 55          | _           | 50          | ns        |  |

| 39   | Address Valid to AS Valid                                                                                                            | 20          | _           | 15          |             | 10          | _           | ns        |  |