DS07-13704-1E

## 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16LX MB90590 Series

# MB90594/591/F594A/F591/V590A

#### **■ DESCRIPTION**

The MB90590-series with two FULL-CAN interfaces and FLASH ROM is especially designed for automotive and industrial applications. Its main feature are two on board CAN Interfaces, which conform to V2.0 Part A and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal full CAN approach. With the new 0.5µm CMOS technology, Fujitsu now also offers on-chip FLASH-ROM program memory. An internal voltage booster removes the necessity for a second programming voltage.

An on board voltage regulator provides 3V to the internal MCU core. This creates a major advantage in terms of EMI and power consumption.

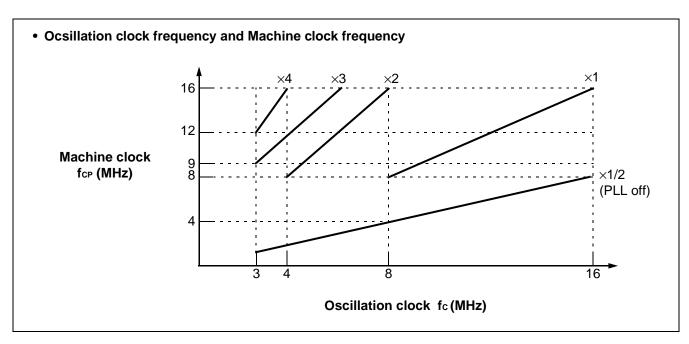

The internal PLL clock frequency multiplier provides an internal 62.5 nsec instruction cycle time from an external 4 MHz clock.

The unit features 4 Stepper Motor Controllers with high current outputs.

Furthermore it features a 6 channel Output Compare Unit and a 6 channel Input Capture Unit with a 16-bit free running timer. Three UARTs constitute additional functionality for communication purposes.

#### **■ FEATURES**

- 16-bit core CPU:4MHz external clock (16 MHz internal, 62.5 nsec instr. cycle time)

- New 0.5 μm CMOS Process Technology

- Internal voltage regulator supports 3V MCU core, offering low EMI and low power consumption figures

- Two FULL-CAN interfaces; conforming to Version 2.0 Part A and Part B, flexible message buffering (mailbox and FIFO buffering can be mixed)

- Powerful interrupt functions (8 progr. priority levels; 8 external interrupts)

(Continued)

#### **■ PACKAGE**

### (Continued)

- El<sup>2</sup>OS Automatic transfer function indep.of CPU; 16 ch. of intelligent I/O Services

- 18-bit Time-base counter

- Watchdog Timer

- 3 full duplex UARTs; support 10.4 KBaud (USA standard)

- Serial I/O: 1ch for synchronous data transfer

- A/D Converter: 8 ch. analog inputs (Resolution 10 bits or 8 bits)

- 16-bit reload timer 2ch

- ICU (Input capture) 16bit \* 6ch

- OCU (Output capture) 16bit \* 6ch

- 16-bit Programmable Pulse Generator 6ch

- Stepping Motor Controller 4ch

- Optimized instruction set for controller applications (bit, byte, word and long-word data types; 23 different addressing modes; barrel shift; variety of pointers)

- 4-byte instruction execution queue

- signed multiply (16bit\*16bit) and divide (32bit/16bit) instructions available

- Program Patch Function

- · Fast Interrupt processing

- Low Power Consumption 7 different power saving modes: (Sleep, Stop, CPU intermittent mode, Hardware standby,...)

- Sound Generator

- Real Time Watch Timer

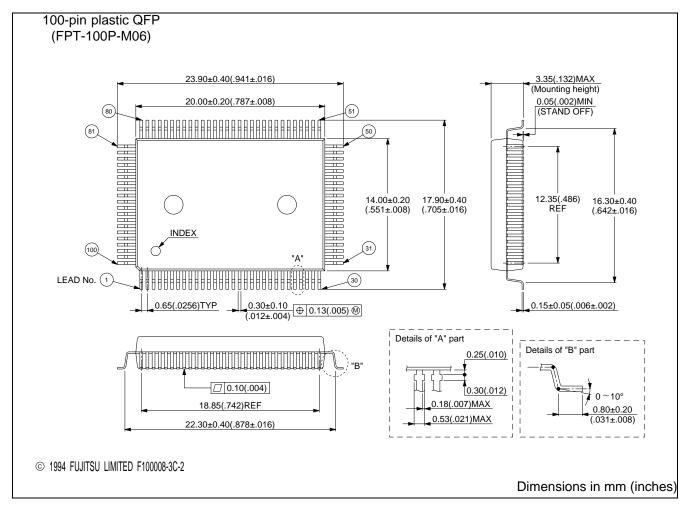

- Package: 100-pin plastic QFP

Controller Area Network (CAN) - License of Robert Bosch GmbH

### **■ PRODUCT LINEUP**

The following table provides a quick outlook of the MB90590 Series

| Features                                 | MB90V590A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MB90F594A/MB90F591                                                                                                                          | MB90594/MB90591            |  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| CPU                                      | F <sup>2</sup> MC-16LX CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                             |                            |  |  |  |

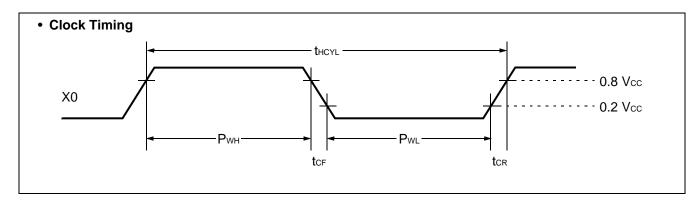

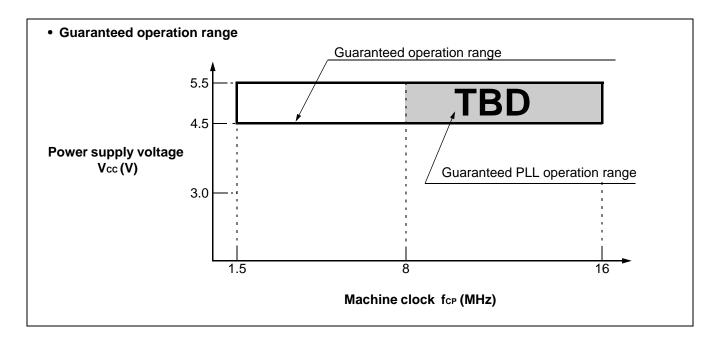

| System clock                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | er ( $\times$ 1, $\times$ 2, $\times$ 3, $\times$ 4, 1/2 when PLL stoution time: 62.5 ns (4 MHz osc. PLL $\times$ 4)                        |                            |  |  |  |

| ROM                                      | External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Boot-block<br>Flash memory 256/384 Kbytes<br>Hard-wired reset vector                                                                        | Mask ROM 256/384<br>Kbytes |  |  |  |

| RAM                                      | 6 Kbytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6/8 Kbytes                                                                                                                                  | 6/8 Kbytes                 |  |  |  |

| Technology                               | 0.5 μm CMOS with on-<br>chip voltage regulator for<br>internal power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.5 μm CMOS with on-chip voltage regulator for internal power supply + Flash memory with On-chip charge pump for programming voltage        |                            |  |  |  |

| Operating voltage range                  | 5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\pm$ 10% (Target for MB90F591 and MB90                                                                                                     | 591)                       |  |  |  |

| Temperature range                        | − 40 to 85 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                             |                            |  |  |  |

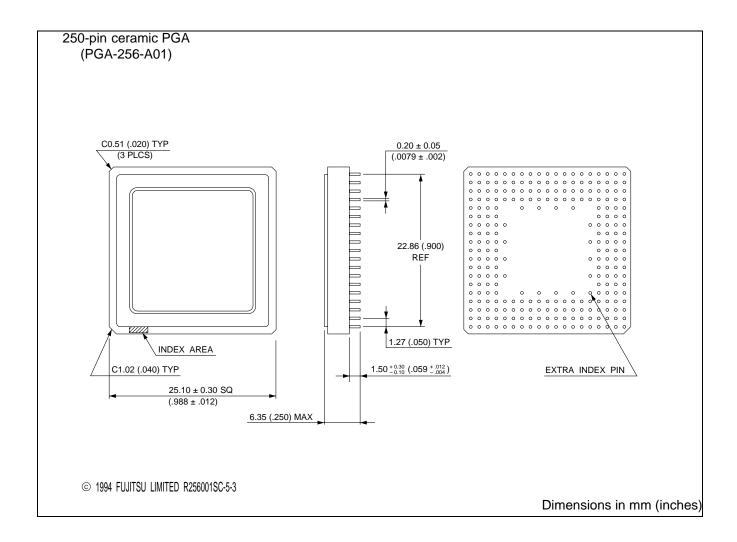

| Package                                  | PGA-256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | QFP-100                                                                                                                                     |                            |  |  |  |

| UART<br>(3 channels)                     | Baud rate: 4808/5208/961                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nchronous (with start/stop bit) transfer<br>5/10417/19230/38460/62500/500000bps<br>s (synchronous) at System clock = 16MH                   | ` •                        |  |  |  |

| Serial IO                                | Supports positive-edge an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | om MSB or LSB<br>nchronized transfer and external clock sy<br>d negative-edge clock synchronization<br>125K/500K/1Mbps at System clock = 16 |                            |  |  |  |

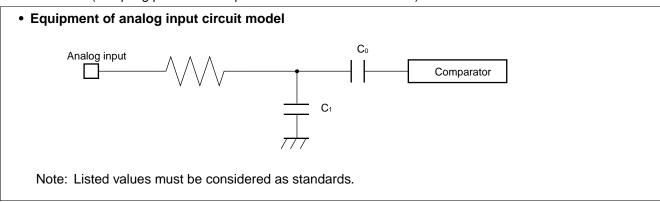

| A/D Converter                            | 10-bit or 8-bit resolution 8<br>Conversion time: 26.3μs (μ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                             |                            |  |  |  |

| 16-bit Reload<br>Timer<br>(2 channels)   | Operation clock frequency<br>Supports External Event C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | : fsys/2 <sup>1</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>5</sup> (fsys = System Count function                                             | clock frequency)           |  |  |  |

| Watch Timer                              | Directly operates with the Facility to correct oscillation Read/Write accessible Seguing Signals interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                             |                            |  |  |  |

| 16-bit IO Timer                          | Signals an interrupt when overflow Supports Timer Clear when a match with Output Compare(Channel 0) Operation clock freq.: fsys/2², fsys/2⁴, fsys/2⁴, fsys/2⁴, fsys/2⁵, fsys/2 |                                                                                                                                             |                            |  |  |  |

| 16-bit Output<br>Compare<br>(6 channels) | Six 16-bit compare registe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | a match with 16-bit IO Timer<br>rs<br>s can be used to generate an output sigr                                                              | nal                        |  |  |  |

| (Continued) Features                                         | MB90V590A                                                                                                                                                                                                              | MB90F594A/MB90F591                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MB90594/MB90591 |  |  |  |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| 16-bit<br>Input Capture<br>(6 channels)                      | Rising edge, falling edge or<br>Six 16-bit Capture registers<br>Signals an interrupt upon ex                                                                                                                           | rising & falling edge sensitive ternal event                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |  |  |  |  |

| 8/16-bit<br>Programma-ble<br>Pulse Gen-erator<br>(6channels) | Twelve 8-bit reload counters<br>Twelve 8-bit reload registers<br>Twelve 8-bit reload registers<br>A pair of 8-bit reload counter<br>8-bit prescaler plus 8-bit relo<br>6 output pins<br>Operation clock freq.: fsys, f | Supports 8-bit and 16-bit operation modes Twelve 8-bit reload counters Twelve 8-bit reload registers for L pulse width Twelve 8-bit reload registers for H pulse width A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler plus 8-bit reload counter 6 output pins Operation clock freq.: fsys, fsys/2 1, fsys/2 2, fsys/2 3, fsys/2 4 or 128µs@fosc=4MHz (fsys = System clock frequency, fosc = Oscillation clock frequency) |                 |  |  |  |  |

| CAN Interface<br>(2 channels)                                | Automatic re-transmission in<br>Automatic transmission resp<br>Prioritized 16 message buffe<br>Supports multiple messages<br>Flexible configuration of acc                                                             | Conforms to CAN Specification Version 2.0 Part A and B Automatic re-transmission in case of error Automatic transmission responding to Remote Frame Prioritized 16 message buffers for data and ID's Supports multiple messages Flexible configuration of acceptance filtering: Full bit compare / Full bit mask / Two partial bit masks                                                                                                                                       |                 |  |  |  |  |

| Stepper Motor<br>Controller<br>(4 channels)                  | Four high current outputs for Synchronized two 8-bit PWN Succeeds to MB89940 design                                                                                                                                    | l's for each channel                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| External Inter-rupt (8 channels)                             | Can be programmed edge s                                                                                                                                                                                               | ensitive or level sensitive                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Sound Gener-ator                                             |                                                                                                                                                                                                                        | ith tone frequency from 8-bit reload<br>2K, 15.6K, 7.8KHz at System clock<br>uency / 2 / (reload value + 1)                                                                                                                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| IO Ports                                                     | All push-pull outputs and sch                                                                                                                                                                                          | n be used as general purpose IO<br>nmitt trigger inputs<br>put/output or peripheral signal                                                                                                                                                                                                                                                                                                                                                                                     |                 |  |  |  |  |

| Flash Memory                                                 |                                                                                                                                                                                                                        | Supports automatic programming, Embedded Algorithm TM * Write/Erase/Erase-Suspend/Resume commands A flag indicating completion of the algorithm Number of erase cycles: 10,000 times Data retention time: 10 years Hard-wired reset vector available in order to point to a fixed boot sector in Flash Memory Flash Writer from Minato Electronics Inc. Boot block configuration Erase can be performed on each block Block protection with external programming voltage       |                 |  |  |  |  |

<sup>\*:</sup> Embedded Algorithm is a trade mark of Advanced Micro Devices Inc.

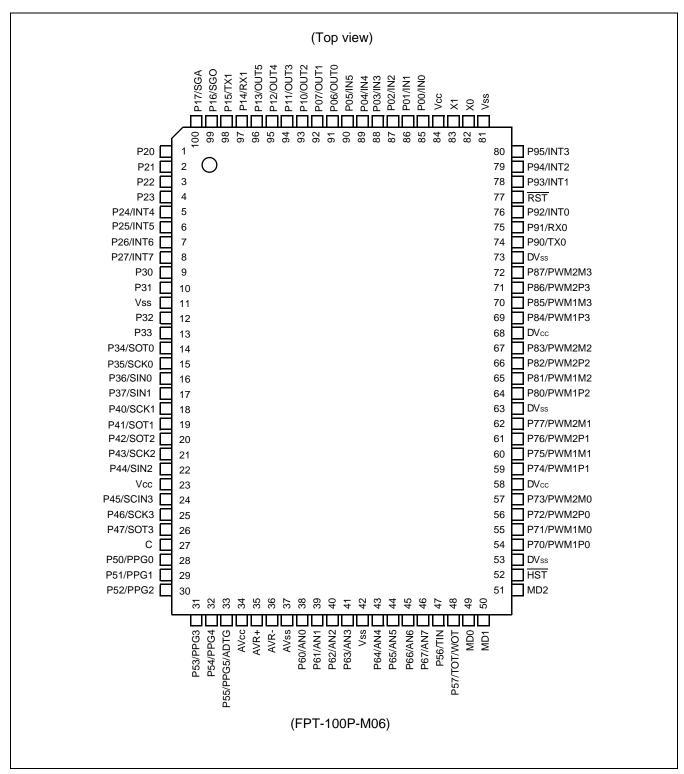

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| No.      | Pin name                 | Circuit type | Function                                                                                                                                     |

|----------|--------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 82       | X0                       | ۸            | Oscillation input                                                                                                                            |

| 83       | X1                       | А            | Oscillation output                                                                                                                           |

| 77       | RST                      | В            | Reset input                                                                                                                                  |

| 52       | HST                      | С            | Hardware standby input                                                                                                                       |

| 85 to 90 | P00 to P05               | D            | General purpose IO                                                                                                                           |

| 65 10 90 | IN0 to IN5               | D            | Inputs for the Input Captures                                                                                                                |

|          | P06 to P07<br>P10 to P13 |              | General purpose IO                                                                                                                           |

| 91 to 96 | OUT0 to OUT5             | D            | Outputs for the Output Compares.  To enable the signal outputs, the corresponding bits of the Port Direction registers should be set to "1". |

| 97       | P14                      | D            | General purpose IO                                                                                                                           |

| 97       | RX1                      | D            | RX input for CAN Interface 1                                                                                                                 |

|          | P15                      |              | General purpose IO                                                                                                                           |

| 98       | TX1                      | TX1 D        | TX output for CAN Interface 1. To enable the signal output, the corresponding bit of the Port Direction register should be set to "1".       |

|          | P16                      |              | General purpose IO                                                                                                                           |

| 99       | SGO                      | D            | SGO output for the Sound Generator. To enable the signal output, the corresponding bit of the Port Direction register should be set to "1".  |

|          | P17                      |              | General purpose IO                                                                                                                           |

| 100      | SGA                      | D            | SGA output for the Sound Generator. To enable the signal output, the corresponding bit of the Port Direction register should be set to "1".  |

| 1 to 4   | P20 to P23               | D            | General purpose IO                                                                                                                           |

| 5 to 8   | P24 to P27               | D            | General purpose IO                                                                                                                           |

| 3 10 0   | INT4 to INT7             | D            | External interrupt input for INT4 to INT7                                                                                                    |

| 9 to 10  | P30 to P31               | D            | General purpose IO                                                                                                                           |

| 12 to 13 | P32 to P33               | D            | General purpose IO                                                                                                                           |

|          | P34                      |              | General purpose IO                                                                                                                           |

| 14       | SOT0                     | D            | SOT output for UART 0.  To enable the signal output, the corresponding bit of the Port Direction register should be set to "1".              |

|          | P35                      |              | General purpose IO                                                                                                                           |

| 15       | SCK0                     | D            | SCK input/output for UART 0. To enable the signal output, the corresponding bit of the Port Direction register should be set to "1".         |

| No.             | Pin name                 | Circuit type | Function                                                                                                                                                                                                        |

|-----------------|--------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16              | P36                      | 0            | General purpose IO                                                                                                                                                                                              |

| 16              | SIN0                     | D            | SIN input for UART 0                                                                                                                                                                                            |

| 17 P37 SIN1 P40 |                          | D            | General purpose IO                                                                                                                                                                                              |

|                 |                          | D            | SIN input for UART 1                                                                                                                                                                                            |

| 10              | P40                      | D            | General purpose IO                                                                                                                                                                                              |

| 18 SCK1         |                          | U            | SCK input/output for UART 1                                                                                                                                                                                     |

| 19              | P41                      | D            | General purpose IO                                                                                                                                                                                              |

| 19              | SOT1                     | D            | SOT output for UART 1                                                                                                                                                                                           |

| 20              | P42                      | D            | General purpose IO                                                                                                                                                                                              |

| 20              | SOT2                     | D            | SOT output for UART 2                                                                                                                                                                                           |

| 21              | P43                      | D            | General purpose IO                                                                                                                                                                                              |

| 21              | SCK2                     | D            | SCK input/output for UART 2                                                                                                                                                                                     |

| 22              | P44                      | D            | General purpose IO                                                                                                                                                                                              |

| SIN2            |                          | D            | SIN input for UART 2                                                                                                                                                                                            |

| 24              | P45                      | D            | General purpose IO                                                                                                                                                                                              |

| 24              | SIN3                     | D            | SIN input for the Serial IO                                                                                                                                                                                     |

| 25              | P46                      | D            | General purpose IO                                                                                                                                                                                              |

| 25              | SCK3                     | D            | SCK input/output for the Serial IO                                                                                                                                                                              |

| 26              | P47                      | D            | General purpose IO                                                                                                                                                                                              |

| 20              | SOT3                     | D            | SOT output for the Serial IO                                                                                                                                                                                    |

|                 | P50 to P55               |              | General purpose IO                                                                                                                                                                                              |

| 28 to 33        | PPG0 to<br>PPG5,<br>ADTG | D            | Outputs for the Programmable Pulse Generators. Pin number 33 is also shared with ADTG input for the external trigger of the A/D Converter.                                                                      |

| 20 to 44        | P60 to P63               | F            | General purpose IO                                                                                                                                                                                              |

| 38 to 41        | AN0 to AN3               | E            | Inputs for the A/D Converter                                                                                                                                                                                    |

| 43 to 46        | P64 to P67               | F            | General purpose IO                                                                                                                                                                                              |

| 43 10 46        | AN4 to AN7               | E            | Inputs for the A/D Converter                                                                                                                                                                                    |

| P56             |                          | 0            | General purpose IO                                                                                                                                                                                              |

| 47              | TIN                      | D            | TIN input for the 16-bit Reload Timers                                                                                                                                                                          |

|                 | P57                      |              | General purpose IO                                                                                                                                                                                              |

| 48              | TOT/WOT                  | D            | TOT output for the 16-bit Reload Timers and WOT output for the Watch Timer. Only one of three output enable flags in these pheripheral blocks can be set at a time. Otherwise the output signal has no meaning. |

| No.            | Pin name                             | Circuit type | Function                                                                           |  |  |  |

|----------------|--------------------------------------|--------------|------------------------------------------------------------------------------------|--|--|--|

|                | P70 to P73                           |              | General purpose IO                                                                 |  |  |  |

| 54 to 57       | PWM1P0<br>PWM1M0<br>PWM2P0<br>PWM2M0 | F            | Output for Stepping Motor Controller channel 0.                                    |  |  |  |

|                | P74 to P77                           |              | General purpose IO                                                                 |  |  |  |

| 59 to 62       | PWM1P1<br>PWM1M1<br>PWM2P1<br>PWM2M1 | F            | Output for Stepping Motor Controller channel 1.                                    |  |  |  |

|                | P80 to P83                           |              | General purpose IO                                                                 |  |  |  |

| 64 to 67       | PWM1P2<br>PWM1M2<br>PWM2P2<br>PWM2M2 | F            | Output for Stepping Motor Controller channel 2.                                    |  |  |  |

|                | P84 to P87                           |              | General purpose IO                                                                 |  |  |  |

| 69 to 72       | PWM1P3<br>PWM1M3<br>PWM2P3<br>PWM2M3 | F            | Output for Stepping Motor Controller channel 3.                                    |  |  |  |

| 7.4            | P90                                  | <b>D</b>     | General purpose IO                                                                 |  |  |  |

| 74             | TX0                                  | D            | TX output for CAN Interface 0                                                      |  |  |  |

| 75             | P91                                  | D            | General purpose IO                                                                 |  |  |  |

| 75             | RX0                                  |              | RX input for CAN Interface 0                                                       |  |  |  |

| 76             | P92                                  | . D          | General purpose IO                                                                 |  |  |  |

| /0             | INT0                                 |              | External interrupt input for INT0                                                  |  |  |  |

| 78             | P93                                  | . D          | General purpose IO                                                                 |  |  |  |

| 70             | INT1                                 |              | External interrupt input for INT1                                                  |  |  |  |

| 79             | P94                                  | D            | General purpose IO                                                                 |  |  |  |

| 7.5            | INT2                                 |              | External interrupt input for INT2                                                  |  |  |  |

| 80             | P95                                  | D            | General purpose IO                                                                 |  |  |  |

| 00             | INT3                                 |              | External interrupt input for INT3                                                  |  |  |  |

| 58<br>68       | DVcc                                 |              | Dedicated power supply pins for the high current output buffers (Pin No. 54 to 72) |  |  |  |

| 53<br>63<br>73 | DVss                                 |              | Dedicated ground pins for the high current output buffers (Pin No. 54 to 72)       |  |  |  |

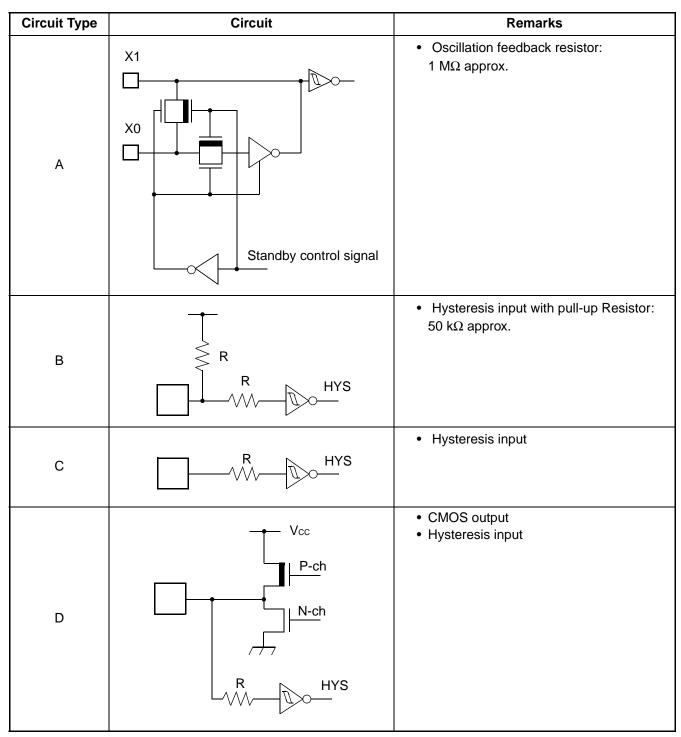

### **■ I/O CIRCUIT TYPE**

| Circuit Type | Circuit                                        | Remarks                                                                     |

|--------------|------------------------------------------------|-----------------------------------------------------------------------------|

| E            | Vcc<br>P-ch<br>N-ch<br>Analog input<br>HYS     | CMOS output     Hysteresis input     Analog input                           |

| F            | P-ch High current N-ch  HYS                    | CMOS high current output     Hysteresis input                               |

| G            | Vcc    P-ch   High current   N-ch   N-ch   HYS | CMOS high current output     Hysteresis input     Analog input  (Continued) |

| Circuit Type | Circuit | Remarks                                                                                                                                |

|--------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| Н            | R HYS   | <ul> <li>Hysteresis input with pull-down Resistor: 50 Kohm approx.</li> <li>Flash version does not have pull-down register.</li> </ul> |

#### **■ HANDLING DEVICES**

#### (1)Preventing latch-up

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than Vcc or lower than Vss is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between Vcc and Vss.

- The AVcc power supply is applied before the Vcc voltage.

Latch-up may increase the power supply current drastically, causing thermal damage to the device.

### (2)Handling unused input pins

Do not leave unused input pins open, as doing so may cause misoperation of the device. Use a pull-up or pull-down resistor.

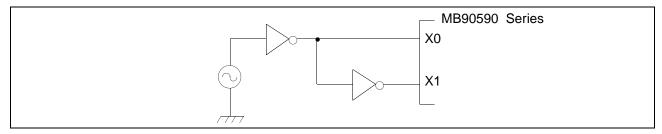

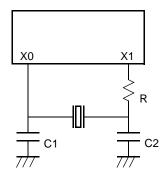

#### (3)Using external clock

To use external clock, drive the X0 and X1 pins in reverse phase.

Below is a diagram of how to use external clock.

Using external clock

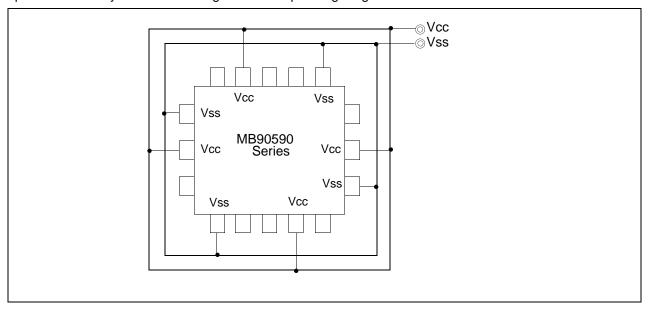

#### (4)Power supply pins (Vcc/Vss)

Ensure that all Vcc-level power supply pins are at the same potential. In addition, ensure the same for all Vss-level power supply pins. (See the figure below.) If there are more than one Vcc or Vss system, the device may operate incorrectly even within the guaranteed operating range.

#### (5) Pull-up/down resistors

The MB90590 Series does not support internal pull-up/down resistors. Use external components where needed.

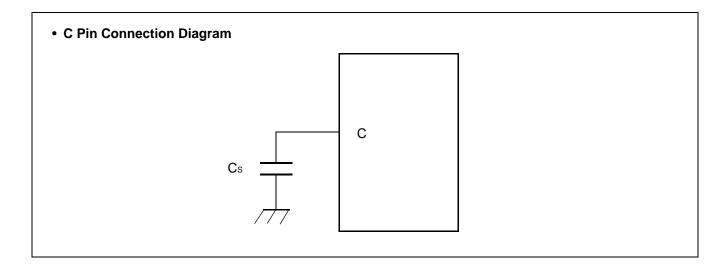

#### (6) Crystal Oscillator Circuit

Noises around X0 or X1 pins may be possible causes of abnormal operations. Make sure to provide bypass capacitors via shortest distance from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure, to the utmost effort, that lines of oscillation circuit not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board art work surrounding X0 and X1 pins with an grand area for stabilizing the operation.

#### (7) Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

Make sure to turn on the A/D converter power supply(AVcc, AVR + , AVR - ) and analog inputs (AN0 to AN7) after turning-on the digital power supply (Vcc).

Turn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure that the voltage not exceed AVR + or AVcc (turning on/off the analog and digital power supplies simultaneously is acceptable).

#### (8) Connection of Unused Pins of A/D Converter

Connect unused pins of A/D converter to AVcc = Vcc, AVss = AVR + = Vss.

#### (9) N.C. Pin

The N.C. (internally connected) pin must be opened for use.

#### (10) Notes on Energization

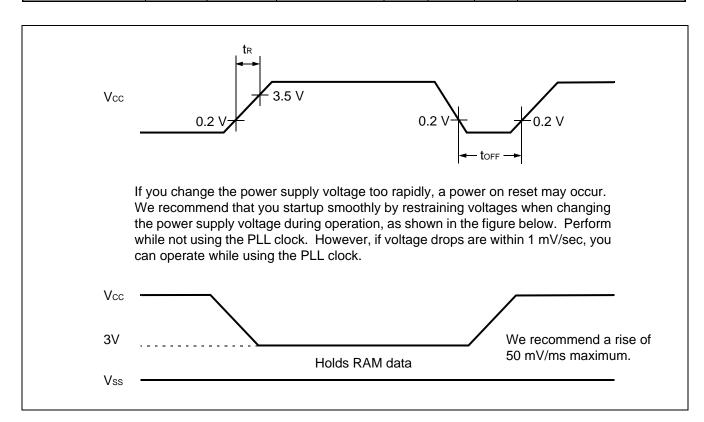

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at 50 or more ms (0.2 V to 2.7 V).

#### (11) Initialization

In the device, there are internal registers which is initialized only by a power-on reset. To initialize these registers turning on the power again.

#### (12) Directions of "DIV A, Ri" and "DIVW A, RWi" instructions

In the Signed multiplication and division instructions ("DIV A, Ri" and "DIVW A, RWi"), the value of the corresponding bank register (DTB, ADB, USB, SSB) is set in "00h".

If the values of the corresponding bank register (DTB,ADB,USB,SSB) are setting other than "00h", the remainder by the execution result of the instruction is not stored in the register of the instruction operand.

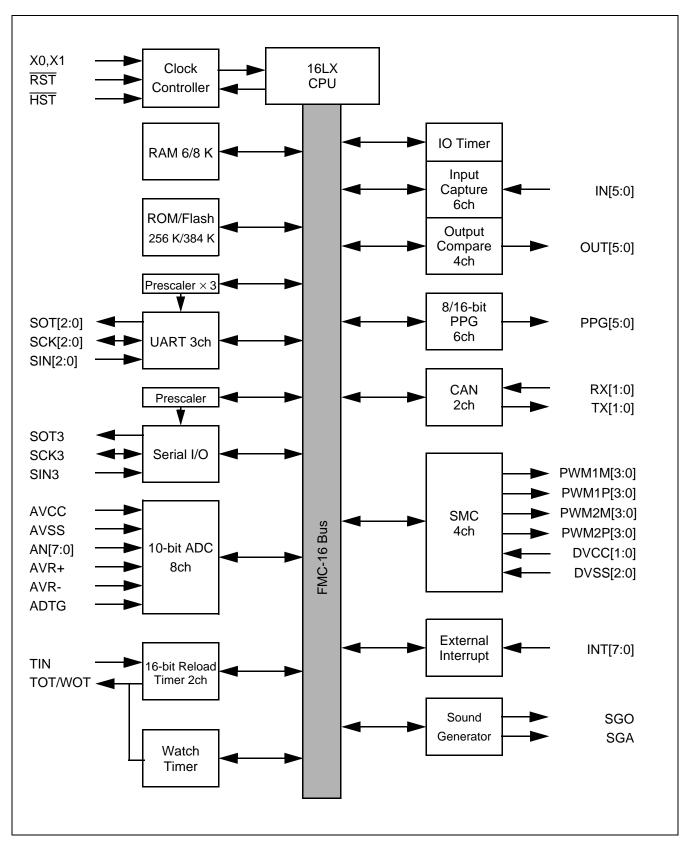

### **■ BLOCK DIAGRAM**

### **■ MEMORY SPACE**

The memory space of the MB90590 Series is shown below

|                                            | MB90V590A                 |                               | MB90594/F594A             |                                            | MB90591/F591             |

|--------------------------------------------|---------------------------|-------------------------------|---------------------------|--------------------------------------------|--------------------------|

| FFFFFFн<br>FF0000н                         | ROM (FF bank)             | FFFFFFн<br>FF0000н            | ROM (FF bank)             | FFFFFFн<br>FF0000н                         | ROM (FF bank)            |

| FEFFFFн<br>FE0000н                         | ROM (FE bank)             | FEFFFFн<br>FE0000н            | ROM (FE bank)             | FEFFFFн<br>FE0000н                         | ROM (FE bank)            |

| FDFFFF <sub>H</sub><br>FD0000 <sub>H</sub> | ROM (FD bank)             | FDFFFFH<br>FD0000H            | ROM (FD bank)             | FDFFFF <sub>H</sub><br>FD0000 <sub>H</sub> | ROM (FD bank)            |

| FCFFFH<br>FC0000H                          | ROM (FC bank)             | FCFFFFH<br>FC0000H            | ROM (FC bank)             | FCFFFH<br>FC0000H                          |                          |

| FBFFFFн<br>FB0000н                         | ROM (FB bank)             |                               |                           | FBFFFFн<br>FB0000н                         | ROM (FB bank)            |

| FAFFFFH<br>FA0000H                         | ROM (FA bank)             |                               |                           | FAFFFFн<br>FA0000н                         | ROM (FA bank)            |

| F9FFFн<br>F90000н                          | ROM (F9 bank)             |                               |                           | F9FFFFн<br>F90000н                         | ROM (F9 bank)            |

| 00FFFFн<br>004000н                         | ROM<br>(Image of FF bank) | 00FFFFн<br>004000н            | ROM<br>(Image of FF bank) | 00FFFFн<br>004000н                         | ROM<br>(Image of FF bank |

| 0028FFн<br>002100н<br>0020FFн              | RAM 2K                    |                               |                           | 0028FFн<br>002100н<br>0020FFн              | RAM 2K                   |

| 001FFFн<br>001900н<br>0018FFн              | Peripheral                | 001FFFн<br>001900н<br>0018FFн | Peripheral                | 001FFFн<br>001900н<br>0018FFн              | Peripheral               |

|                                            | RAM 6K                    |                               | RAM 6K                    |                                            | RAM 6K                   |

| 000100н                                    |                           | 000100н                       |                           | 000100н                                    |                          |

| 0000BFн<br>000000н                         | Peripheral                | 0000BFн<br>000000н            | Peripheral                | 0000BFн<br>000000н                         | Peripheral               |

### Memory space map

The high-order portion of bank 00 gives the image of the FF bank ROM to make the small model of the C compiler effective. Since the low-order 16 bits are the same, the table in ROM can be referenced without using the far specification in the pointer declaration.

For example, an attempt to access 00C000H accesses the value at FFC000H in ROM.

The ROM area in bank FF exceeds 48 Kbytes, and its entire image cannot be shown in bank 00.

The image between FF4000H and FFFFFH is visible in bank 00, while the image between FF0000H and FF3FFFH is visible only in bank FF.

### ■ I/O MAP

| Address    | Register                  | Abbreviation    | Access | Pripheral   | Initial value               |

|------------|---------------------------|-----------------|--------|-------------|-----------------------------|

| 00 н       | Port 0 data register      | PDR0            | R/W    | Port 0      | XXXXXXXXB                   |

| 01 н       | Port 1 data register      | PDR1            | R/W    | Port 1      | XXXXXXXXB                   |

| 02 н       | Port 2 data register      | PDR2            | R/W    | Port 2      | XXXXXXXX                    |

| 03 н       | Port 3 data register      | PDR3            | R/W    | Port 3      | XXXXXXXX                    |

| 04 н       | Port 4 data register      | PDR4            | R/W    | Port 4      | XXXXXXXXB                   |

| 05 н       | Port 5 data register      | PDR5            | R/W    | Port 5      | XXXXXXXX                    |

| 06 н       | Port 6 data register      | PDR6            | R/W    | Port 6      | XXXXXXXX                    |

| 07 н       | Port 7 data register      | PDR7            | R/W    | Port 7      | XXXXXXXX                    |

| 08 н       | Port 8 data register      | PDR8            | R/W    | Port 8      | XXXXXXXX                    |

| 09 н       | Port 9 data register      | PDR9            | R/W    | Port 9      | XXXXXXB                     |

| 0A to 0F н |                           | Reser           | ved    |             | 1                           |

| 10 н       | Port 0 direction register | DDR0            | R/W    | Port 0      | 0 0 0 0 0 0 0 0в            |

| 11 н       | Port 1 direction register | DDR1            | R/W    | Port 1      | 0 0 0 0 0 0 0 0в            |

| 12 н       | Port 2 direction register | DDR2            | R/W    | Port 2      | 0 0 0 0 0 0 0 0в            |

| 13 н       | Port 3 direction register | DDR3            | R/W    | Port 3      | 0 0 0 0 0 0 0 0в            |

| 14 н       | Port 4 direction register | DDR4            | R/W    | Port 4      | 0 0 0 0 0 0 0 0в            |

| 15 н       | Port 5 direction register | DDR5            | R/W    | Port 5      | 0 0 0 0 0 0 0 0в            |

| 16 н       | Port 6 direction register | DDR6            | R/W    | Port 6      | 0 0 0 0 0 0 0 0 В           |

| 17 н       | Port 7 direction register | DDR7            | R/W    | Port 7      | 0 0 0 0 0 0 0 0в            |

| 18 н       | Port 8 direction register | DDR8            | R/W    | Port 8      | 0 0 0 0 0 0 0 0в            |

| 19 н       | Port 9 direction register | DDR9            | R/W    | Port 9      | 000000                      |

| 1А н       |                           | Reser           | ved    |             |                             |

| 1В н       | Analog Input Enable       | ADER            | R/W    | Port 6, A/D | 11111111                    |

| 1С to 1F н |                           | Reser           | ved    |             |                             |

| 20 н       | Serial Mode Control 0     | UMC0            | R/W    |             | 0 0 0 0 0 1 0 Ов            |

| 21 н       | Status 0                  | USR0            | R/W    |             | 0 0 0 1 0 0 0 0в            |

| 22 н       | Input/Output Data 0       | UIDR0/<br>UODR0 | R/W    | UART0       | XXXXXXXXB                   |

| 23 н       | Rate and Datar 0          | URD0            | R/W    |             | 0 0 0 0 0 0 0X <sub>B</sub> |

| 24 н       | Serial Mode Control 1     | UMC1            | R/W    |             | 0 0 0 0 0 1 0 Ов            |

| 25 н       | Status 1                  | USR1            | R/W    | 1           | 0 0 0 1 0 0 0 0в            |

| 26 н       | Input/Output Data 1       | UIDR1/<br>UODR1 | R/W    | UART1       | XXXXXXXXB                   |

| 27 н       | Rate and Datar 1          | URD1            | R/W    |             | 0 0 0 0 0 0 0X <sub>B</sub> |