## Features

- Single power supply: 4.5V~5.5V

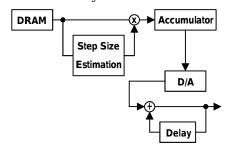

- ADM algorithm

- Auto playback with an echo effect

- DRAM options:

- 64K

- 256K

- Sampling rate options:

- 32K bps (bits per second)

- 16K bps

- Applications

- Toys

- Educations

- Recording capacity: 2, 4, 8, 16 seconds

- A built-in 2 stage microphone amplifier

- A built-in DRAM refresh circuit

- A voltage type D/A output

- A current type D/A output

- Auto power-off

- Low power dissipation

- Games

1

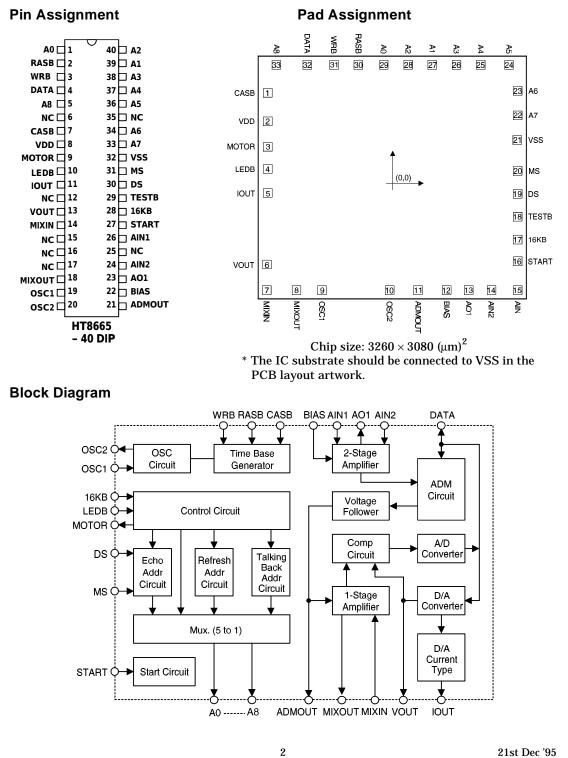

**General Description**

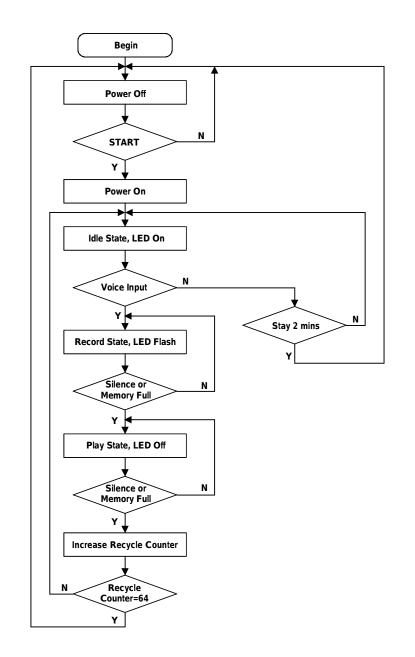

The HT8665 is a single chip CMOS LSI using an ADM algorithm. It is designed for applications on talking back with an echo effect. Functions of the IC consist of recording/playing and auto power off in addition to an echo effect. The IC starts recording when a sound input is detected, and stops to play back when silence lasts 0.5 seconds during recording. The auto power off function is activated once a REC/PLAY cycle has been implemented 64 times or an interval of silence exceeds 2 minutes. The HT8665 provides a recording capacity of 2 seconds at a 32K bps sampling rate for DRAM of 64K (8 seconds for DRAM of 256K) and 4 seconds at a 16K bps sampling rate (16 seconds for DRAM of 256Kb). A higher sampling rate results in sounds of better quality but sacrifices the recording time, and vice versa.

| Pad Coo | Pad Coordinates Unit: |          |         |          |         |  |  |

|---------|-----------------------|----------|---------|----------|---------|--|--|

| Pad No. | X                     | Y        | Pad No. | Х        | Y       |  |  |

| 1       | -1447.00              | 977.75   | 18      | 1447.00  | -452.75 |  |  |

| 2       | -1434.00              | 648.25   | 19      | 1447.00  | -189.75 |  |  |

| 3       | -1447.00              | 354.75   | 20      | 1447.00  | 75.25   |  |  |

| 4       | -1447.00              | 99.25    | 21      | 1442.00  | 434.25  |  |  |

| 5       | -1429.50              | -178.75  | 22      | 1447.00  | 718.75  |  |  |

| 6       | -1447.00              | -1004.75 | 23      | 1447.00  | 999.75  |  |  |

| 7       | -1450.00              | -1300.75 | 24      | 1346.00  | 1300.75 |  |  |

| 8       | -1106.50              | -1300.75 | 25      | 1020.00  | 1300.75 |  |  |

| 9       | -813.00               | -1300.75 | 26      | 741.00   | 1300.75 |  |  |

| 10      | -31.00                | -1300.75 | 27      | 460.00   | 1300.75 |  |  |

| 11      | 296.00                | -1300.75 | 28      | 181.00   | 1300.75 |  |  |

| 12      | 626.00                | -1300.75 | 29      | -100.00  | 1300.75 |  |  |

| 13      | 881.50                | -1300.75 | 30      | -393.00  | 1300.75 |  |  |

| 14      | 1143.50               | -1300.75 | 31      | -674.00  | 1300.75 |  |  |

| 15      | 1447.00               | -1305.75 | 32      | -983.50  | 1300.75 |  |  |

| 16      | 1447.00               | -965.25  | 33      | -1340.00 | 1300.75 |  |  |

| 17      | 1447.00               | -717.75  |         |          |         |  |  |

# **Pin Description**

| Pin No. | Pin Name | I/O | Internal<br>Connection | Description                                                                                   |  |

|---------|----------|-----|------------------------|-----------------------------------------------------------------------------------------------|--|

| 1       | A0       | 0   | CMOS                   | DRAM address output                                                                           |  |

| 2       | RASB     | 0   | CMOS                   | DRAM row address strobe                                                                       |  |

| 3       | WRB      | 0   | CMOS                   | DRAM write enable                                                                             |  |

| 4       | DATA     | I/O | CMOS                   | DRAM data input/output                                                                        |  |

| 5       | A8       | 0   | CMOS                   | DRAM address output                                                                           |  |

| 6       | NC       | —   | —                      | No connection                                                                                 |  |

| 7       | CASB     | 0   | CMOS                   | DRAM column address strobe                                                                    |  |

| 8       | VDD      | Ι   | _                      | Positive power supply                                                                         |  |

| 9       | MOTOR    | 0   | CMOS                   | Motor drive output (active high)                                                              |  |

| 10      | LEDB     | 0   | NMOS<br>Open Drain     | LED indicator:<br>Idle: LED is turned on;<br>Record: LED flashes;<br>Play: LED is turned off. |  |

| 11      | IOUT     | 0   | PMOS<br>Open Drain     | Current type audio output for an external transistor                                          |  |

3

<u>HT8665</u>

| Pin No. | Pin Name | I/O | Internal<br>Connection | Description                                                                                                                       |  |

|---------|----------|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| 12      | NC       | _   | _                      | No connection                                                                                                                     |  |

| 13      | VOUT     | 0   | _                      | Voltage type audio output for an external power AMP                                                                               |  |

| 14      | MIXIN    | Ι   | _                      | Echo mixer input                                                                                                                  |  |

| 15      | NC       | _   | _                      | No connection                                                                                                                     |  |

| 16      | NC       | _   | _                      | No connection                                                                                                                     |  |

| 17      | NC       | _   | _                      | No connection                                                                                                                     |  |

| 18      | MIXOUT   | 0   | _                      | Echo mixer output                                                                                                                 |  |

| 19      | OSC1     | Ι   | _                      | Oscillator input                                                                                                                  |  |

| 20      | OSC2     | 0   | _                      | Oscillator output                                                                                                                 |  |

| 21      | ADMOUT   | 0   | _                      | ADM D/A output                                                                                                                    |  |

| 22      | BIAS     | 0   | —                      | For OP bias de-coupling                                                                                                           |  |

| 23      | AO1      | 0   | _                      | Internal AMP first stage output                                                                                                   |  |

| 24      | AIN2     | Ι   | _                      | Internal AMP second stage input (inverting)                                                                                       |  |

| 25      | NC       | _   | _                      | No connection                                                                                                                     |  |

| 26      | AIN1     | Ι   | _                      | Internal AMP first stage input (inverting)                                                                                        |  |

| 27      | START    | 0   | CMOS                   | System start pin                                                                                                                  |  |

| 28      | 16KB     | I   | Pull-High              | Sampling rate selection:<br>Open/high: 32K bps;<br>Low: 16K bps                                                                   |  |

| 29      | TESTB    | Ι   | Pull-Low               | For IC test only                                                                                                                  |  |

| 30      | DS       | Ι   | Pull-High              | Echo delay time selection:<br>1. DRAM of 64K: Open/high: 256ms;<br>Low: 128ms<br>2. DRAM of 256K: Open/high: 512ms;<br>Low: 256ms |  |

| 31      | MS       | I   | Pull-High              | DRAM size selection:<br>Open/high: 64K;<br>Low: 256K                                                                              |  |

| 32      | VSS      | Ι   | _                      | Negative power supply (GND)                                                                                                       |  |

| 33      | A7       | 0   | CMOS                   | DRAM address output                                                                                                               |  |

| 34      | A6       | 0   | CMOS                   | DRAM address output                                                                                                               |  |

| 35      | NC       | _   | _                      | No connection                                                                                                                     |  |

| 36      | A5       | 0   | CMOS                   | DRAM address output                                                                                                               |  |

4

| Pin N | o. Pin Name | I/O | Internal<br>Connection | Description         |

|-------|-------------|-----|------------------------|---------------------|

| 37    | A4          | 0   | CMOS                   | DRAM address output |

| 38    | A3          | 0   | CMOS                   | DRAM address output |

| 39    | A1          | 0   | CMOS                   | DRAM address output |

| 40    | A2          | 0   | CMOS                   | DRAM address output |

## Absolute Maximum Ratings

| Supply Voltage | –0.3V to 6V                           |

|----------------|---------------------------------------|

| Input Voltage  | $V_{SS}0.3V$ to $V_{DD}\mbox{+-}0.3V$ |

| Storage Temperature –50°C to 125°C | , |

|------------------------------------|---|

| Operating Temperature20°C to 70°C  | , |

## **Electrical Characteristics**

| Symbol           | Parameter                | Te                       | st Condition                        | Min.         | <b>T</b> | Max.         | Unit |

|------------------|--------------------------|--------------------------|-------------------------------------|--------------|----------|--------------|------|

| Symbol           | r ai ainetei             | V <sub>DD</sub>          | Condition                           | IVIIII.      | Тур.     |              |      |

| VDD              | Operating Voltage        |                          | _                                   | 4.5          |          | 5.5          | V    |

| IOP              | Operating Current        | 5V                       | No load,<br>F <sub>OSC</sub> =1MKHz | _            | 3        | 6            | mA   |

| I <sub>OH1</sub> | IOUT Max. Source Current | 5V                       | $V_{OH}=0.5V$                       | -1.5         | -3       |              | mA   |

| IOH2             | MOTOR Source Current     | 5V                       | V <sub>OH</sub> =4.5                | -1           | -3.5     | _            | mA   |

| Iol              | LED Sink Current         | 5V                       | V <sub>OH</sub> =0.5V               | 3            | -3.5     |              | mA   |

| VIH              | "H" Input Voltage        | _                        | —                                   | $0.7 V_{DD}$ | —        | VDD          | V    |

| V <sub>IL</sub>  | "L" Input Voltage        | _                        | _                                   | 0            |          | $0.3 V_{DD}$ | V    |

| Vout             | Max. VOUT Output Voltage | 5V                       | RL>50K                              |              | 1.5      |              | VP-P |

| Fosc             | System Frequency         | 5V R <sub>OSC</sub> =27K |                                     | _            | 1        | _            | MHz  |

21st Dec '95

(Ta=25°C)

## **Functional Description**

The HT8665 is a single chip LSI with an external DRAM. It is designed for applications on talking back with an echo effect. The recording length of the IC is decided by the data rate along with the size of an external memory. Sounds input from an external microphone are coded through an internal ADM algorithm and saved in an external memory until the memory is full or an interval of silence lasts over 0.5 seconds. Once recording is terminated, the IC will play back the recorded sounds with an echo effect automatically.

#### **Record function**

The HT8665 provides 2 kinds of sampling rate as well as DRAM interfaces. The sampling rate (S.R.) along with DRAM determine the recording capacity as shown in the following table: (for  $F_{OSC}$ =640 KHz)

| MS (DRAM) | 16KB (S.R.) | Recording<br>Capacity |  |  |

|-----------|-------------|-----------------------|--|--|

| 1 (64Kb)  | 1 (32K bps) | 2 seconds             |  |  |

| 1 (64Kb)  | 0 (16K bps) | 4 seconds             |  |  |

| 0 (256Kb) | 1 (32K bps) | 8 seconds             |  |  |

| 0 (256Kb) | 0 (16K bps) | 16 seconds            |  |  |

Notes: "1" is connected to VDD or left open.

"0" is connected to VSS.

Recording starts whenever a sound input is detected. It then stops once silence is detected or the recording capacity is full. After that, talking back comes into play.

#### **Play function**

The HT8665 stops to play back the recorded sounds when an interval of silence lasts 0.5 seconds or the memory is full during recording. Its playing rate is the same as the rates of recording and echo effect. The echo delay time is settable by the DS pin as shown.

| DS<br>DRAM | 1     | 0     |  |

|------------|-------|-------|--|

| 64Kb       | 256ms | 128ms |  |

| 256Kb      | 512ms | 256ms |  |

#### **Power control**

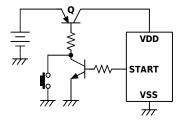

The HT8665 provides a START pin for power control. The START pin is of high impedance and switch Q is turned off at initial. After the START key is triggered, it will output a high level signal and switch Q is turned on. This pin outputs a low level signal and the power of LSI is switched off when a REC/PLAY cycle has been implemented 64 times or an interval of silence lasts over 2 minutes.

#### Motor

The HT8665 provides a motor driving pin. The motor is turned on during playing but off once talking back is terminated.

#### Status display

The HT8665 provides an LEDB pin to display its operation status. An external LED is switched on when the IC is in the standby state. It, on the other hand, is switched off when the IC is in the playing state. The LED will flash with the sound volume when the IC is in the recording state, but its intensity will vary inversely with the volume.

#### 6

HT8665

### Flowchart

21st Dec '95

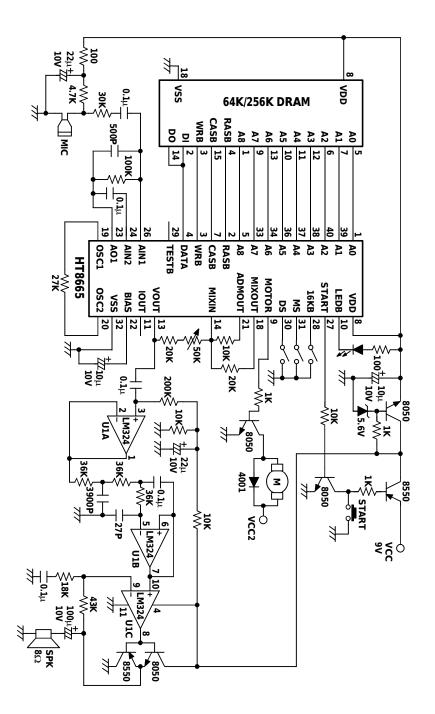

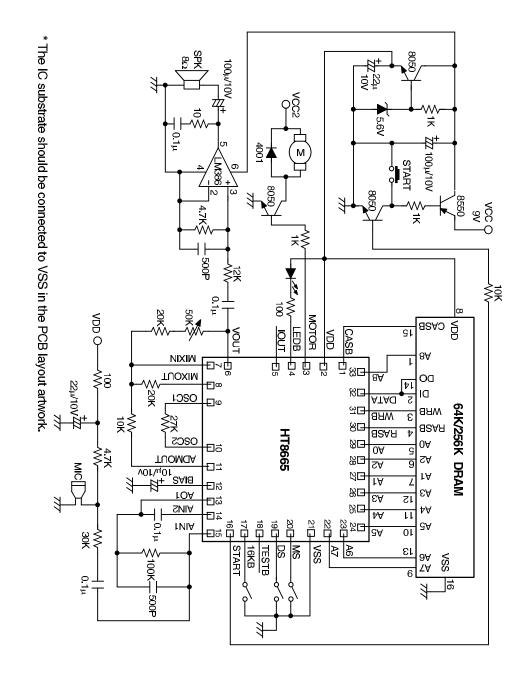

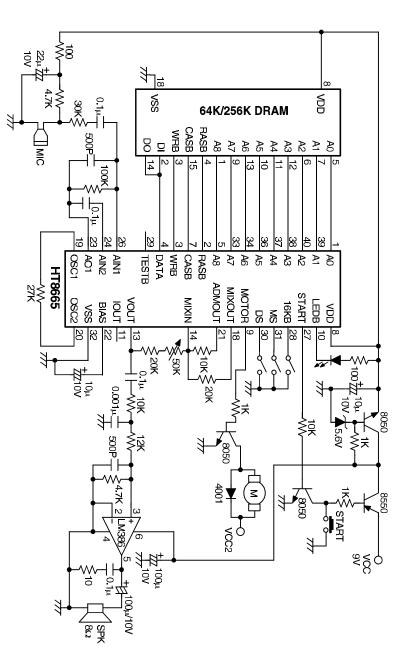

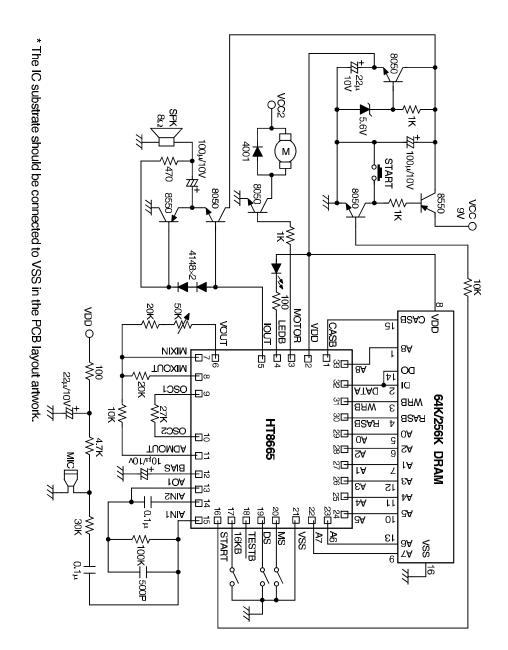

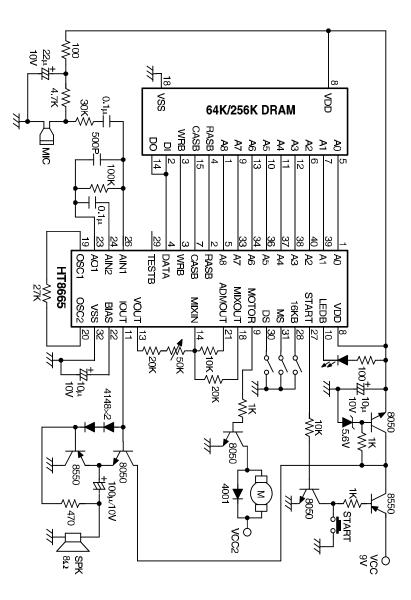

## **Application Circuits**

LM386 output

8

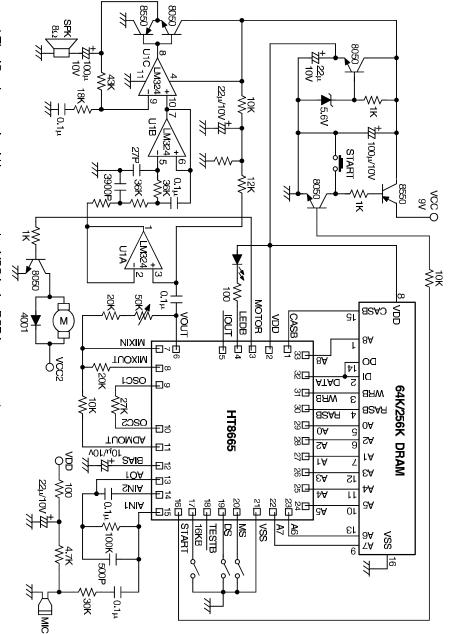

### Two transistor output

21st Dec '95

LM324 output

12

\* The IC substrate should be connected to VSS in the PCB layout artwork.