#### Product Preview

# Power Management and Interface IC for Smartcard Readers and Couplers

The MC33561 is an integrated circuit dedicated to the Smartcard interface applications. The device handles any type of smart or memory based card through a simple and flexible microcontroller interface. On top of that, thanks to the built—in chip select pin, several couplers can be connected in parallel. The MC33561 is particularly suited for low cost, low power applications, with high extended battery life coming from extremely low quiescent current.

#### **Features**

- 100% Compatible with ISO 7816–3 Standard

- Wide Battery Supply Voltage Range: 1.8 V < V<sub>bat</sub> < 6.6 V

- Programmable V<sub>CC</sub> Supply to Cope with either 3 V or 5 V Card Operation

- Very Low Quiescent Current in Standby Mode: 5 µA Max

- Built-in DC/DC Converter Generates the V<sub>CC</sub> Supply with Minimum External Components

- Full Control of the Power Up/Down Sequence Yields High Signal Integrity on both the Card I/O and the Signal Lines

- Programmable Card Clock Generator

- Built-in Chip Select Logic Allows Parallel Coupling Operation

- ESD Protection on Card Pins (4 kV, Human Body Model)

- Fault Monitoring Includes Vbatlow, Vcclow and Icclim

#### **ON Semiconductor**

Formerly a Division of Motorola

http://onsemi.com

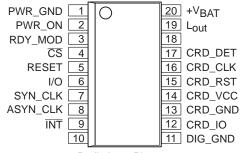

## CASE 948E PIN CONNECTIONS

#### Preliminary Pinout

ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

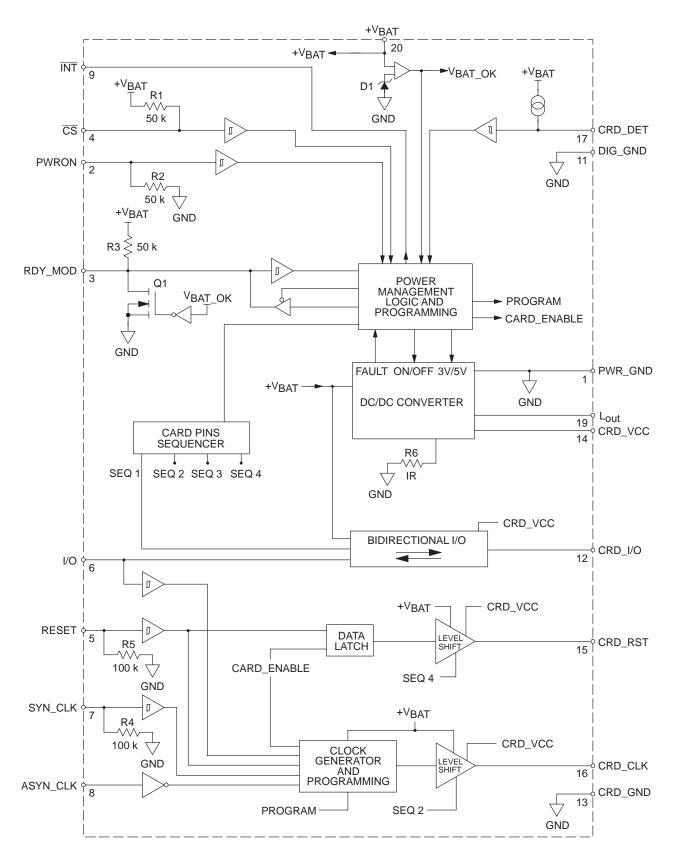

Figure 2. Detailed Block Diagram

#### **Table 1. Pin Functions and Description**

#### **CONTROLLER INTERFACE**

| Pin   | Symbol     | Туре                          | Name/Function                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------|------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2     | PWR_ON     | INPUT<br>Pull Down            | This pin valid the operation of the internal DC/DC converter.                                                                                                                                                                                                                                                                                                                                             |  |  |

| 3     | RDY_MOD    | I/O and Pull Up               | This bidirectional pin features tri–state output and schmitt trigger input. When RDY_MOD is forced to 0, the MC33xxx is set to programming mode by a nega transition on CS pin.                                                                                                                                                                                                                           |  |  |

| 4     | CS         | INPUT<br>Pull Up              | This pin provides the MC33561 chip select function. Pins x x x are disabled when CS = H. When RDY_MOD = L, the device jumps in the programming mode upon the falling edge of CS (See Figure YY).                                                                                                                                                                                                          |  |  |

| 5     | RESET      | INPUT<br>Pull Down            | The signal presents as this pin is translated to pin XX (card reset signal) when CS = L. The signal on this pin is latched when CS = H. This pin is also used in programming mode (See ZZZ).                                                                                                                                                                                                              |  |  |

| 6     | I/O        | Input/Output                  | This pin is connected to an external microcontroller interface. A bidirectional level translator adapts the serial I/O signal between the smartcard and the microcontroller. The level translator is enabled when CS = L. The signal present on this pin is latched when CS = H. This pin is also used in programming mode (See ZZZ).                                                                     |  |  |

| 7     | SYN_CLK    | CLOCK INPUT<br>Pull Down      | This pin, generally connected to the controller serial interface clock, is used to set up communications with synchronous cards. The signal is fed to the internal clock selector circuit and is translated to CRD_CLK upon appropriate programming of the MC33561. When the device operates in the programming mode, the signal present on this pin is latched when CS = H.                              |  |  |

| 8     | ASY_CLK_IN | CLOCK INPUT<br>High Impedance | This pin can be connected to either the microcontroller master clock, or to any clock signal, to drive the asynchronous cards. The signal is fed to internal clock selector circuit and translated to the CRD_CLK at either the same frequency, or divided by 2 or 4, depending upon the programming mode (See AAA).                                                                                      |  |  |

| 9     | INT        | OUTPUT<br>Pull Down           | This pin is activated LOW when a card has been inserted and detected by the interface. The signal is reset to a logic 1 on the rising edge of either CS or PWR_ON. The Collector open mode makes possible the wired AND/OR external logic. When two or more interfaces share the INT function with a single micro controller, the software must polls the MC33561 to identify the origin of the interupt. |  |  |

| ARD I | NTERFACE   |                               |                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 12    | CRD_IO     | I/O                           | This pin handles the connection to the serial I/O pin of the card connector. A bi–directional level translator adapts the serial I/O signal between the card and the micro controller.                                                                                                                                                                                                                    |  |  |

| 13    | CRD_GND    | GROUND                        | This pin is connected to the external card ground. It is the ground reference for all analog and digital signals.                                                                                                                                                                                                                                                                                         |  |  |

| 14    | CRD_VCC    | POWER                         | This pin provides the power to the external card. It is the logic level "1" for CRD_IO CRD_RST and CRD_CLK signals.                                                                                                                                                                                                                                                                                       |  |  |

| 15    | CRD_RST    | OUTPUT                        | This pin is connected to the RESET pin of the card connector. A level translator adapts the RESET signal from the micro controller to the external card.                                                                                                                                                                                                                                                  |  |  |

| 16    | CRD_CLK    | OUTPUT                        | This pin is connected to the CLK pin of the card connector. The CRD_CLK signal comes from the clock selector circuit output. The clock selection is programmed by using pins x x x with RDY_MOD forced to a logic zero.                                                                                                                                                                                   |  |  |

| 17    | CRD_DET    | INPUT                         | The signal coming from the external card connector is used to detect the presence of the card. A built in pull up resistor makes this pin active LOW.                                                                                                                                                                                                                                                     |  |  |

| Pin                                                                                                                                                  | Pin Symbol Type Name/Function |       |                                                                                                                                                                  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| POWER SUPPLY AND GROUND                                                                                                                              |                               |       |                                                                                                                                                                  |  |  |  |  |

| 1 PWR_GND POWER This pin is the current return from the external inductor L1. It is mandatory to carefully connect this pin to CRD_GND ground plane. |                               |       |                                                                                                                                                                  |  |  |  |  |

| 13                                                                                                                                                   | CRD_GND                       | POWER | This pin is the signal ground and must be connected to the ground pin of the card connector. This pin is the reference level for all analog and digital signals. |  |  |  |  |

| 14                                                                                                                                                   | CRD_VCC                       | POWER | This pin is connected to the Vcc pin of the card connector. This pin is the logic level reference for pins xx xx xx.                                             |  |  |  |  |

| 19                                                                                                                                                   | Ext_L                         | POWER | This pin is connected to the external inductor used for the DC/DC converter. Please refer to the DC/DC block description.                                        |  |  |  |  |

| 20                                                                                                                                                   | Vbat                          | POWER | This pin is connected to the supply voltage. The MC33561 operation is inhibited when Vbat is below the minimum value.                                            |  |  |  |  |

#### **Programming and Status Functions**

The MC33561 features a programming interface and a status interface. Table 2 illustrates the programming mode.

Table 2. Programming and Status Functions Pin Out Logic

|                     | Program CRD_VCC<br>to 3 V/5 V  | Select Vcc<br>ON/OFF | Select Clock<br>Input | Program ASY_CLKIN Divide Ration | Poll Card<br>Status | Poll CRD_VCC<br>Status |

|---------------------|--------------------------------|----------------------|-----------------------|---------------------------------|---------------------|------------------------|

| RDY_MOD<br>(In–out) | Force to 0                     | READ                 | Force to 0            | Force to 0                      | READ                | READ                   |

| CS (in)             | Rising edge                    | 0                    | Rising edge           | Rising edge                     | 0                   | 0                      |

| PWR_ON (in)         | 0/1                            | 0/1                  | Program<br>CRD_VCC    | Program<br>CRD_VCC              | 0 or Hi–Z           | 1                      |

| RESET (in)          | Program CLK input/divide ratio | Not used             | 0/1                   | 0/1                             | Not used            | Not used               |

| I/O (in)            | Program CLK input/divide ratio | Not used             | 0/1                   | 0/1                             | Not used            | Not used               |

#### **MAXIMUM RATINGS(1)**

| Symbol                                 | Rating                                                                              | Value                                                                                           | Unit       |

|----------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|

| V <sub>bat</sub>                       | Battery Supply Voltage                                                              | 7.0                                                                                             | V          |

| I <sub>bat</sub>                       | Battery Supply Current                                                              | ±200                                                                                            | mA         |

| Vcc                                    | Power Supply Voltage                                                                | 6.0                                                                                             | V          |

| Icc                                    | Power Supply Current                                                                | ± 150                                                                                           | mA         |

| Vin                                    | Digital Input Pins                                                                  | $-0.5 \text{ V} < \text{V}_{\text{in}} < \text{V}_{\text{bat}} + 0.5 \text{ V},$<br>but $< 7.0$ | V          |

| l <sub>in</sub>                        |                                                                                     | ±5.0                                                                                            | mA         |

| V <sub>out</sub>                       | Digital Output Pins                                                                 | $-0.5 \text{ V} < \text{V}_{\text{in}} < \text{V}_{\text{bat}} + 0.5 \text{ V},$<br>but $< 7.0$ | V          |

| l <sub>out</sub>                       |                                                                                     | ±10                                                                                             | mA         |

| V <sub>card</sub><br>I <sub>card</sub> | Card Interface Pins                                                                 | $-0.5 \text{ V} < \text{V}_{\text{card}} < \text{V}_{\text{CC}} + 0.5 \text{ V},$<br>$\pm 25$   | V<br>mA    |

| lΓ                                     | Inductor Driver Pin<br>Power Ground Pin (Pin 1)                                     | ±200<br>±100                                                                                    | mA<br>mA   |

| V <sub>ESD</sub>                       | ESD Capability <sup>(2)</sup> Standard Pins Card Interface Pins                     | 2<br>4                                                                                          | kV<br>kV   |

| P <sub>D</sub><br>R <sub>θ</sub> JA    | SO–16WB Package Power Dissipation @ Tamb = +85°C Thermal Resistance Junction to Air | 285<br>140                                                                                      | mW<br>°C/W |

| TA                                     | Operating Ambient Temperature Range                                                 | - 25 to +85                                                                                     | °C         |

| TJ                                     | Operating Junction Temperature Range                                                | - 40 to +125                                                                                    | °C         |

| T <sub>Jmax</sub>                      | Maximum Junction Temperature(3)                                                     | +150                                                                                            | °C         |

| T <sub>sg</sub>                        | Storage Temperature Range                                                           | -65 to +150                                                                                     | °C         |

<sup>(1)</sup> Maximum electrical ratings are defined as those values beyond which damage to the device may occur at  $T_A = +25$ °C.

<sup>(2)</sup> Human Body Model, R = 1500  $\Omega$ , C = 100 pF

<sup>(3)</sup> Absolute Maximum Rating beyond which damage to the device may occur.

**ELECTRICAL CHARACTERISTICS** The convention considers current flowing into the pin (sink current) as positive and current flowing out of the pin (source current) as negative. (Conditions:  $V_{BAT} = 4 \text{ V}$ ,  $V_{CC} = 5 \text{ V}$  nom,  $PWR\_ON = V_{BAT}$ ,  $-I_{CC} = 10 \text{ mA}$ ,  $-25^{\circ}C \leq T_{A} \leq 85^{\circ}C$ ,  $L_{1} = 47 \text{ }\mu\text{H}$ ,  $CRD\_VCC$  capacitor =  $10 \text{ }\mu\text{F}$ , unless otherwise noted.)

#### **BATTERY POWER SUPPLY SECTION**

| Symbol             | Characteristic                                                                           | Test Conditions                                                                                                    | Min        | Тур               | Max        | Unit |

|--------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------|-------------------|------------|------|

| V <sub>bat</sub>   | Supply Voltage Range                                                                     | Normal Operating Range<br>Extended Operating Range <sup>(4)</sup>                                                  | 2.2<br>1.8 | _                 | 6.0<br>6.6 | V    |

| l <sub>obat</sub>  | Standby Quiescent Current                                                                | PWR_ON = GND, CRDC_ON = GND<br>ASY_CLKIN = GND, V <sub>bat</sub> = 6 V,<br>all other logic inputs and outputs open | _          | _                 | 5.0        | μА   |

| I <sub>batop</sub> | DC Operating Current                                                                     | $-I_{CC} = 10 \text{ mA}, V_{CC} = 5 \text{ V}, V_{bat} = 6 \text{ V}$                                             | _          | _                 | 12.5       | μА   |

|                    | V <sub>bat</sub> Under Voltage Detection<br>Upper Voltage<br>Lower Voltage<br>Hysteresis |                                                                                                                    | _          | 1.6<br>1.4<br>0.2 | _          | V    |

<sup>(4)</sup> See Figures x and xx.

#### POWER SUPPLY SECTION @ $V_{CC} = 5 \text{ V Nominal}$

| Symbol                                      | Characteristic                                                                                             | Test Conditions                                                                                                                                                                                                           | Min          | Тур        | Max                   | Unit         |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-----------------------|--------------|

| V <sub>CC</sub>                             | Output Voltage                                                                                             | $2.2 \text{ V} < \text{V}_{\text{bat}} < 6 \text{ V}$ $1 \text{ mA} < -\text{I}_{\text{CC}} < 25 \text{ mA}$ $3.0 \text{ V} < \text{V}_{\text{bat}} < 6 \text{ V}$ $1 \text{ mA} < -\text{I}_{\text{CC}} < 60 \text{ mA}$ | 4.75<br>4.60 | 5.0<br>5.0 | 5.25<br>5.40          | V            |

| V <sub>th</sub><br>V <sub>tl</sub><br>Vhyss | Card V <sub>CC</sub> Under Voltage Detection<br>Upper Threshold<br>Lower Threshold<br>Switching Hysteresis | RDY_MOD Output<br>See Table 4                                                                                                                                                                                             | 4.2<br>120   | 4.5<br>180 | V <sub>cc</sub> -0.14 | V<br>V<br>mV |

| -I <sub>CC</sub> Lim                        | Peak Output Current                                                                                        | V <sub>CC</sub> = 4 V, Internally Limited<br>RDY_MOD = L                                                                                                                                                                  | 70           | _          | _                     | mA           |

| tdy                                         | Current Limit Time Out                                                                                     | $V_{CC} = 4 V$                                                                                                                                                                                                            | _            | 160        | _                     | ms           |

| ICCst                                       | Start-up Current                                                                                           | $V_{CC} = 2 V$<br>$0^{\circ}C < T_{A} < +85^{\circ}C$<br>$-40^{\circ}C < T_{A} < 0^{\circ}C$                                                                                                                              | 70<br>50     | _          | _<br>_                | mA           |

| V <sub>sat</sub>                            | Low Side Power Switch Saturation                                                                           | I <sub>L</sub> = 50 mA                                                                                                                                                                                                    | _            | 100        | 160                   | mV           |

| ٧F                                          | Rectifier Forward Voltage                                                                                  | I <sub>L</sub> = 50 mA                                                                                                                                                                                                    | _            | 400        | 520                   | mV           |

| F <sub>SW</sub>                             | DC/DC Switching Frequency                                                                                  | T <sub>A</sub> = +25°C                                                                                                                                                                                                    | _            | 120        |                       | kHz          |

| I <sub>SD</sub>                             | Shut Down Current<br>(Card Access Deactivated)                                                             | $PWR\_ON = GND$ $V_{CC} = 2 V$                                                                                                                                                                                            | 70           | _          | _                     | mA           |

#### POWER SUPPLY SECTION @ $V_{CC} = 3 \text{ V Nominal}$

| Symbol                                      | Characteristic                                                                                    | Test Conditions                                                                                                                      | Min          | Тур        | Max                   | Unit         |

|---------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-----------------------|--------------|

| V <sub>cc</sub>                             | Output Voltage                                                                                    | 2.2 V < V <sub>bat</sub> <6 V<br>1 mA < -I <sub>CC</sub> < 10 mA<br>2.5 V < V <sub>bat</sub> <6 V<br>1 mA < -I <sub>CC</sub> < 50 mA | 2.75<br>2.60 | 3.0        | 3.25<br>3.40          | V            |

| V <sub>th</sub><br>V <sub>tl</sub><br>Vhyss | Card V <sub>CC</sub> Under Voltage Detection Upper Threshold Lower Threshold Switching Hysteresis | RDY_MOD Output<br>See Table yyy                                                                                                      | 2.4<br>80    | 2.7<br>110 | V <sub>CC</sub> -0.10 | V<br>V<br>mV |

| I <sub>CCst</sub>                           | Start-up Current<br>Shut Down Current                                                             | $V_{CC} = 2 V$ $0^{\circ}C < T_{A} < +85^{\circ}C$ $-40^{\circ}C < T_{A} < 0^{\circ}C$                                               | 50<br>50     | _          |                       | mA           |

#### APPLICATION INTERFACE DC SECTION @ $V_{bat} = 5 \text{ V}$

| Symbol            | Characteristic                              | Test Conditions                                                                                       | Min                                                                  | Тур | Max                                                                     | Unit |

|-------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----|-------------------------------------------------------------------------|------|

| VIH               | Input High Threshold Voltage (Increasing)   | Pin                                                                                                   | 0.55*V <sub>bat</sub>                                                | _   | 0.55*V <sub>bat</sub>                                                   | V    |

| VIL               | Input Low Threshold Voltage<br>(Decreasing) | Pin<br>Pin<br>Pin                                                                                     | 0.3*V <sub>bat</sub><br>0.2*V <sub>bat</sub><br>0.3*V <sub>bat</sub> | _   | 0.45*V <sub>bat</sub><br>0.40*V <sub>bat</sub><br>0.50*V <sub>bat</sub> | V    |

| V <sub>hyst</sub> | Switching Hysteresis                        | Pin                                                                                                   | 0.06*V <sub>bat</sub>                                                | _   | 0.30*V <sub>bat</sub>                                                   | V    |

|                   | Threshold Voltage                           | Pin                                                                                                   | _                                                                    | _   | _                                                                       | V    |

| R <sub>down</sub> | Pull-down Resistance                        | $V_{in} = V_{bat} - 1 V$                                                                              | 50                                                                   | 100 | 200                                                                     | kΩ   |

| R <sub>up</sub>   | Pull-up Resistance                          | V <sub>in</sub> = 0.5 V                                                                               | 50                                                                   | 100 | 200                                                                     | kΩ   |

| VOH               | Output High Voltage                         | $I_{OH}$ = $-2.5 \mu A$ , @ CS = H<br>$I_{OH}$ = $-50 \mu A$<br>$I_{OH}$ = $-0.2 \mu A$ , Output Mode | V <sub>bat</sub> -1                                                  | _   | _                                                                       | V    |

| VOL               | Output Low Voltage                          | I <sub>OL</sub> = 1 mA<br>I <sub>OL</sub> = 0.2 mA                                                    | _                                                                    | _   | 0.4                                                                     | V    |

| I <sub>leak</sub> | Input Leakage Current                       | V <sub>in</sub> = 2.5 V, CS = H                                                                       | _                                                                    | _   | 2.0                                                                     | μΑ   |

#### CARD INTERFACE DC SECTION @ Vbat = 5 V

| Symbol           | Characteristic                                                   | Test Conditions                                        | Min                  | Тур | Max | Unit |

|------------------|------------------------------------------------------------------|--------------------------------------------------------|----------------------|-----|-----|------|

| VOH              | Output High Voltage                                              | $I_{OH} = -20 \mu\text{A}$<br>$I_{OL} = 0.2 \text{mA}$ | V <sub>CC</sub> -0.9 | _   | _   | V    |

| VOL              | Output Low Voltage                                               | I <sub>OL</sub> = 1 mA<br>I <sub>OL</sub> = 0.2 mA     | _                    | _   | 0.4 | V    |

|                  | I/O Pull–up Resistance,<br>Operating Mode, CS = L,<br>PWR_ON = H | V <sub>OL</sub> = 0.5 V                                | 18                   | _   | _   | kΩ   |

| V <sub>sec</sub> | Card Pins Security Voltage<br>(Card Access Deactivated)          | PWR_ON = GND, I <sub>in</sub> = 10 mA                  | _                    | _   | 2.0 | V    |

#### DIGITAL DYNAMIC SECTION @ V<sub>bat</sub> = 5 V, Normal Operating Mode(6)

| Symbol         | Characteristic                       | Test Conditions                           | Min | Тур | Max        | Unit |

|----------------|--------------------------------------|-------------------------------------------|-----|-----|------------|------|

| Fasyclk        | Input Clock Frequency                | Duty Cycle = 50%                          | _   | _   | 20         | MHz  |

| Fcrdclk        | Card Clock Frequency                 |                                           | _   | _   | 20         | MHz  |

| Rclk           | Card Clock Duty Cycle <sup>(7)</sup> | Fio = 16 MHz, 50% V <sub>CC</sub>         | 45  | _   | 55         | %    |

| Trclk<br>Tfclk | Card Clock Rise/Fall Time            | 10 −90% V <sub>CC</sub>                   | _   | _   | 10<br>10   | ns   |

| Fio            | I/O Data Transfer Frequency          | (8)                                       | _   | 1.0 | _          | MHz  |

| Trio<br>Tfio   | I/O Rise and Fall Time               | 10%–90% V <sub>CC</sub>                   | _   | _   | 150<br>150 | ns   |

|                | I/O Transfer Time                    | 50% V <sub>CC</sub> , L- <h, h-="">L</h,> | _   | _   | _          | _    |

| Tdseq          | Card Signal Sequence Interval        | V <sub>CC</sub> Power Up/Down             | _   | 0.2 | 1.0        | μs   |

| Tdres          | Internal Reset Delay                 | RES, V <sub>CC</sub> Power Up/Down        | _   | 20  | _          | μs   |

| Tdrdy          | Ready Delay Time                     |                                           | _   | _   | 2.0        | μs   |

| Twon           | PWR_ON Low Pulse Width               | CS = L                                    | 2.0 | _   | _          | μs   |

<sup>(6)</sup> Pin Load = 30 pF

(7) Since the clock buffer is optimized for low current consumption, clock signal duty cycle is guaranteed for divide by 2 and divide by 4 ratio.

#### DIGITAL DYNAMIC SECTION @ Vbat = 5 V, Programming Mode(6)

| Symbol | Characteristic                                     | Test Conditions | Min | Тур | Max | Unit |

|--------|----------------------------------------------------|-----------------|-----|-----|-----|------|

| Tsmod  | Data Set-up Time<br>RDY_MOD, PWR_ON,<br>RESET, I/O |                 | 1.0 |     | _   | μs   |

| Thmod  | Data Hold Time<br>RDY_MOD, PWR_ON,<br>RESET, I/O   |                 | 1.0 | _   |     | μs   |

| Twcs   | CS Low Pulse Width                                 |                 | 2.0 |     |     | μs   |

#### **DETAILED OPERATING DESCRIPTION**

#### **Card Vcc and Card Clock Programming**

The CRD\_VCC and ASY\_CLK programming options allows matching the system frequency with the card clock frequency, and to select 3 V or 5 V CRD\_VCC supply. The table 3 given hereafter highlight the PWR\_ON, RESET and I/O values for the possible options. The default power reset condition is state 4: synchronous clock and CRD\_VCC = 5 V. All states are latched for each output variable in programming mode at the positive going slope of CS.

**Table 3. Card Vcc and Card Clock Truth Table**

| STATE # | PWR_ON | RESET | I/O | CRD_VCC | CRD_CLK     |

|---------|--------|-------|-----|---------|-------------|

| 0       | L      | L     | L   | 3 V     | SYN_CLK     |

| 1       | L      | L     | Н   | 3 V     | ASY_CLKIN/4 |

| 2       | L      | Н     | Н   | 3 V     | ASY_CLKIN/2 |

| 3       | L      | Н     | L   | 3 V     | ASY_CLKIN   |

| 4       | Н      | L     | L   | 5 V     | SYN_CLK     |

| 5       | Н      | L     | Н   | 5 V     | ASY_CLKIN/4 |

| 6       | Н      | Н     | Н   | 5 V     | ASY_CLKIN/2 |

| 7       | Н      | Н     | L   | 5 V     | ASY_CLKIN   |

NOTE: Card clock integrity is guaranteed no spikes whatever be the frequency switching. At power ON, state 4 is the default state machine.

#### DC/DC Converter and Card Detector Status

The MC33561 status can be polled when CS = L. Please consult Table 3 for a description of input and output signals. The status message is described in Table 4.

Table 4.

| PWR_ON (Input) | RDY_MOD (Output) | Message                    |

|----------------|------------------|----------------------------|

| LOW            | LOW              | No Card                    |

| LOW            | HIGH             | Card Present               |

| HIGH           | LOW              | DC/DC Converter Overloaded |

| HIGH           | HIGH             | DC/DC Converter OK         |

#### **APPLICATIONS INFORMATION**

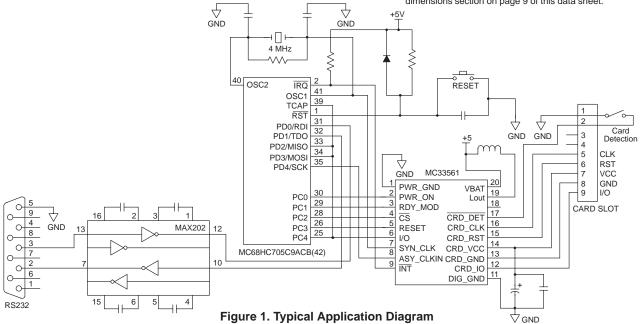

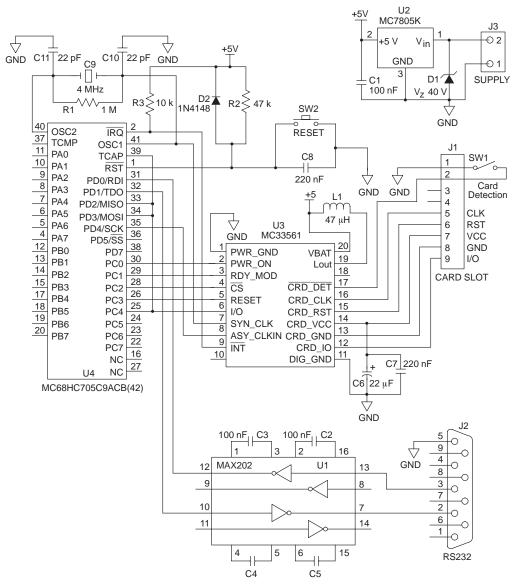

Figure 3. Typical Application Schematic Diagram

#### **ORDERING INFORMATION**

| Device       | Package  | Shipping                 |

|--------------|----------|--------------------------|

| MC33561DTB   | TSSOP-20 | 75 Units / Rail          |

| MC33561DTBR2 | TSSOP-20 | 2500 Units / Tape & Reel |

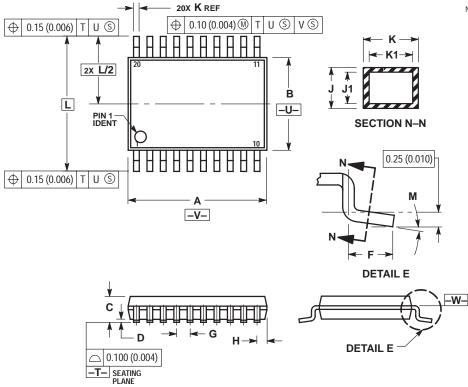

#### **PACKAGE DIMENSIONS**

#### TSSOP-20 **DTB SUFFIX**

CASE 948E-02 **ISSUE A**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

- Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION. SHALL NOT EXCEED 0.25 (0.010) PER SIDE PER SIDE.

- PER SIDE.

DIMENSION K DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN

EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

TERMINAL NUMBERS ARE SHOWN FOR

- REFERENCE ONLY.

7. DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE W–.

|     | MILLIN   | IETERS | INCHES    |       |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 6.40     | 6.60   | 0.252     | 0.260 |

| В   | 4.30     | 4.50   | 0.169     | 0.177 |

| С   |          | 1.20   |           | 0.047 |

| D   | 0.05     | 0.15   | 0.002     | 0.006 |

| F   | 0.50     | 0.75   | 0.020     | 0.030 |

| G   | 0.65 BSC |        | 0.026 BSC |       |

| Н   | 0.27     | 0.37   | 0.011     | 0.015 |

| J   | 0.09     | 0.20   | 0.004     | 0.008 |

| J1  | 0.09     | 0.16   | 0.004     | 0.006 |

| K   | 0.19     | 0.30   | 0.007     | 0.012 |

| K1  | 0.19     | 0.25   | 0.007     | 0.010 |

| L   | 6.40 BSC |        | 0.252 BSC |       |

| M   | 0°       | 8°     | 0°        | 8°    |

### **Notes**

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### **USA/EUROPE Literature Fulfillment:**

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line\*: 303-675-2167

800-344-3810 Toll Free USA/Canada \*To receive a Fax of our publications

N. America Technical Support: 800-282-9855 Toll Free USA/Canada

ASIA/PACIFIC: LDC for ON Semiconductor - Asia Support

Phone: 303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time)

Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4-32-1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan 141-8549

Phone: 81-3-5487-8345 Email: r14153@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.