## INTEGRATED CIRCUITS

## DATA SHEET

# **SAA7708H**Car Radio Digital Signal Processor

Preliminary specification File under Integrated Circuits, RACE/docu/7708N1A\_Datasht.frm 1998 May 19

## **SAA7708H**

#### CONTENTS

| 1                | GENERAL DESCRIPTION                                                  |

|------------------|----------------------------------------------------------------------|

| 2                | HARDWARE FEATURES                                                    |

| 3                | SOFTWARE FEATURES                                                    |

| 1                | APPLICATIONS                                                         |

|                  |                                                                      |

| 5                | QUICK REFERENCE DATA                                                 |

| 5                | ORDERING INFORMATION                                                 |

| 7                | APPLICATION BLOCK DIAGRAM                                            |

| 3                | BLOCK DIAGRAM                                                        |

| 9                | PINNING                                                              |

| 9.1              | Pinning diagram                                                      |

| 10               | FUNCTIONAL DESCRIPTION                                               |

| 10.1             | Signal path for Level information                                    |

| 10.1.1           | The VREFAD pin                                                       |

| 10.2             | Signal path of the third order switched capacitor AD's               |

| 10.2.1           | The FM MPX signal path                                               |

| 10.2.2           | Input sensitivity for FM and RDS                                     |

| 10.2.3           | The signal flow of the AM, CD analog and TAPE                        |

| 10.2.4           | Analog source switching                                              |

| 10.2.5           | The realisation of common mode inputs                                |

| 10.2.6           | Phone input with volume control                                      |

| 10.3             | Input selection switches                                             |

| 10.4             | Supply of the analog inputs                                          |

| 10.5             | The DCS clock block                                                  |

| 10.6             | Synchronization with the DSP core                                    |

| 10.7             | IAC                                                                  |

| 10.7.1           | General description                                                  |

| 10.7.2           | Parameter setting for the MPX input ignition detector                |

| 10.7.3           | AGC set point (1 bit)                                                |

| 10.7.4           | Threshold sensitivity offset (3 bits)                                |

| 10.7.5           | Deviation feed forward factor (3 bits)                               |

| 10.7.6           | Suppresion stretch time (3 bits)                                     |

| 10.7.7           | MPX delay                                                            |

| 10.7.8<br>10.7.9 | Level IAC threshold (4 bits) Level IAC feed forward setting (2 bits) |

| 10.7.9           | Level IAC suppression stretch time (2 bits)                          |

| 10.7.10          | Dynamic IAC threshold levels                                         |

| 10.7.11          | IAC testing                                                          |

| 10.7.12          | Analog outputs                                                       |

| 10.8.1           | D/A converters                                                       |

| 10.8.2           | Upsample filter                                                      |

| 10.8.3           | Volume control                                                       |

| 10.8.4           | Function of the POM pin                                              |

| 10.8.5           | The Fader                                                            |

| 10.8.6           | Power off plop suppression                                           |

| 10.8.7           | The Internal VREFDA pin                                              |

| 10.8.8           | Supply of the analog outputs                                         |

| 10.9             | Clock circuit and oscillator                                         |

## **SAA7708H**

| 10.9.1    | Supply of the X-tal oscillator                                   |

|-----------|------------------------------------------------------------------|

| 10.10     | The phase lock loop circuit to generate the DSP and other clocks |

| 10.11     | The DSP core                                                     |

| 10.12     | DSP core status register and the external control pins           |

| 10.13     | I <sup>2</sup> C control (SCL and SDA pin)                       |

| 10.14     | I <sup>2</sup> S and SPDIF inputs                                |

| 10.14.1   | General description I2S inputs                                   |

| 10.14.2   | The timing diagram of the communication is shown in Fig. 11.     |

| 10.14.3   | Digital data stream formats                                      |

| 10.14.4   | General description SPDIF INPUTS                                 |

| 10.14.4.1 | SPDIF format                                                     |

| 10.14.4.2 | SPDIF channel modulation                                         |

| 10.14.4.3 | Timing Characteristicse logic.                                   |

| 10.15     | RDS decoder (RDS_CLOCK / RDS_DATA pins)                          |

| 10.15.1   | Clock and data recovery                                          |

| 10.15.2   | Timing of Clock and Data signals                                 |

| 10.15.3   | Buffering of RDS data                                            |

| 10.15.4   | Buffer interface                                                 |

| 10.16     | DSP Reset                                                        |

| 10.17     | Power supply connection and EMC                                  |

| 11        | ELECTRICAL CHARACTERISTICS                                       |

| 12        | THERMAL RESISTANCE                                               |

| 13        | DC CHARACTERISTICS                                               |

| 14        | ANALOG INPUTS                                                    |

| 15        | ANALOG OUTPUTS                                                   |

| 16        | OSCILLATOR                                                       |

| 17        | RDS TIMING                                                       |

| 18        | SUPPLY CURRENTS                                                  |

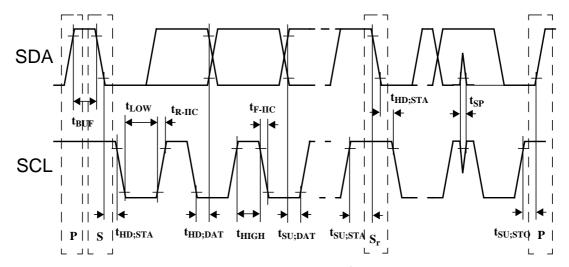

| 19        | I2C BUS CONTROL AND COMMANDS                                     |

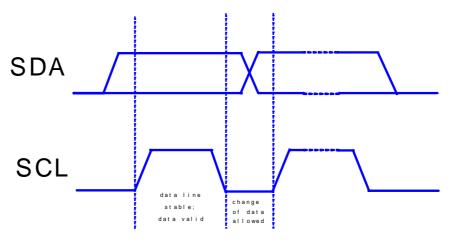

| 19.1      | Characteristics of the I2C Bus                                   |

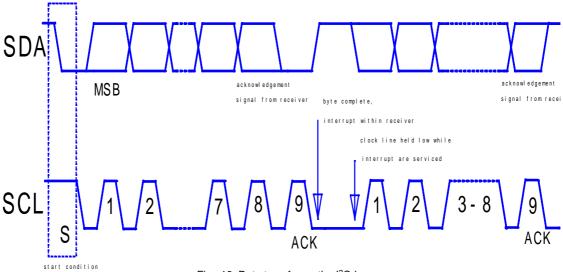

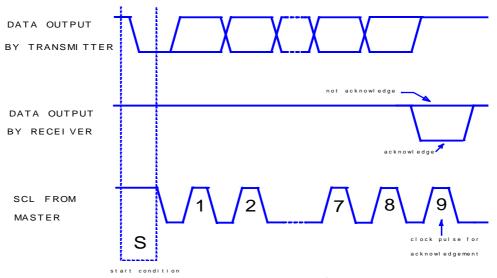

| 19.2      | Bit transfer                                                     |

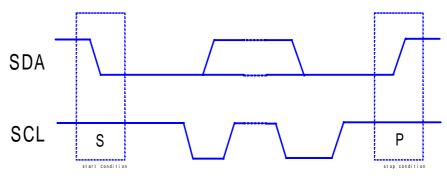

| 19.3      | Start and stop conditions                                        |

| 19.4      | Data transfer                                                    |

| 19.5      | Acknowledge                                                      |

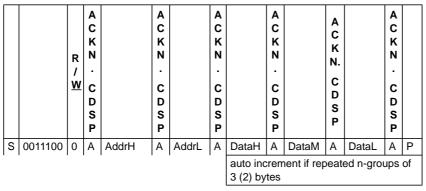

| 20        | I2C BUS FORMAT                                                   |

| 20.1      | Addressing                                                       |

| 20.2      | Slave address (A0 pin)                                           |

| 20.3      | CDSP write cycles                                                |

| 20.4      | CDSP READ cycles                                                 |

| 20.5      | I2C memory map specification                                     |

| 20.6      | I2C Memory map definition                                        |

| 20.7      | Table definitions                                                |

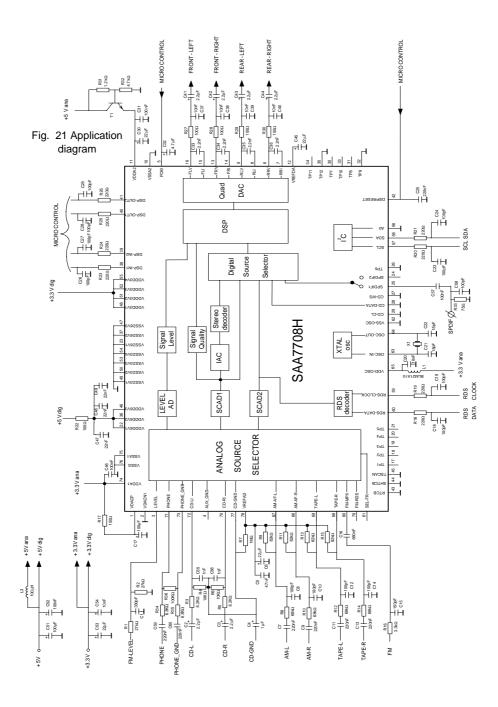

| 21        | APPLICATION DIAGRAM                                              |

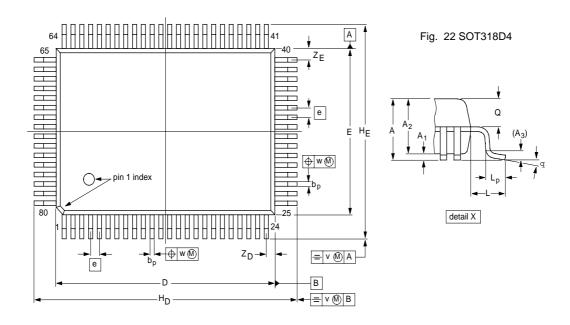

| 22        | MECHANICAL OUTLINE DRAWING OF PACKAGE                            |

**SAA7708H**

#### 1 GENERAL DESCRIPTION

The CDSP-chip performs all the signal functions in front of the power amplifiers and behind the AM and FM\_MPX demodulation of a car radio or the tape input. These functions are: interference absorption, stereo decoding, RDS decoding, FM and AM weak signal processing (soft-mute, sliding stereo, etc.), Dolby-B tape noise reduction and the audio controls (volume, balance, fader and tone). Some functions have been implemented in hardware (stereo decoder, RDS decoding and IAC for FM\_MPX) and are not freely programmable. A digital audio signals from external sources with the Philips I<sup>2</sup>S and the LSB 16, 18 and 20 bit justified format or SPDIF format are accepted. There are four independent analog output channels..

The DSP contains a basic program which enables a set with AM/FM reception, sophisticated FM weak signal functions, MSS, Dolby-B tape noise reduction system, CD play with compressor function and separate bass and treble tone control and fader/balance control.

#### 2 HARDWARE FEATURES

- Two 3rd order SCAD (switch cap analog to digital converters)

- · D/A converters with four fold over sampling and noise shaping

- Digital stereo decoder for the FM\_MPX signal

- · Improved, digital IAC for FM

- RDS processing with optional 16 bit buffer via a separate channel.

- Phone input with common mode rejection. Can be mixed with DAC output of front channels or processed via an AD

- Auxiliary high CMRR analog CD input (CD-walkman, speech, economic CD-changer etc.)

- One separate full I2S and LSB justified format and two muxable SPDIF high performance input interfaces

- · Audio output short circuit protected

- I2C bus controlled

- AM input or AM\_Right and AM\_Left input

- · Phase Lock Loop to generate the high frequency DSP clock from common fundamental oscillator crystal

- · Combined AM/FM level input

- Two analog single ended tape inputs

- -40 to +85 °C operating temperature range

#### 3 SOFTWARE FEATURES

- Improved FM weak signal processing

- Integrated 19 kHz MPX filter and de-emphasis

- Electronic adjustments: FM/AM level, FM channel separation, Dolby level

- Baseband Audio processing (treble/bass/balance/fader/volume)

- · Dynamic loudness or bass boost

- · Audio level meter

- Music Search detection for Tape (MSS)

- · Dolby-B tape noise reduction

- · CD dynamics compressor

- CD De-emphasis processing

- Improved AM processing with IAC

- Soft Audio Mute

**SAA7708H**

- Extended Bleep functions

- Pause detection for RDS updates

- Signal level, noise and multipath detection for AM/FM signal quality information

#### 4 APPLICATIONS

• Car radio systems

## **SAA7708H**

## 5 QUICK REFERENCE DATA

| SYMBOL          | PARAMETER CONDITIONS                                             |                                                                                | MIN | TYP         | MAX          | UNIT    |  |

|-----------------|------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|-------------|--------------|---------|--|

| V <sub>d3</sub> | Operating supply voltage 3.3 Volt analog and digital             | with respect to Vss all parts                                                  | 3   | 3.3         | 3.6          | V       |  |

| V <sub>d5</sub> | Operating supply voltage 5<br>Volt periphery                     | with respect to Vss all parts                                                  | 4.5 | 5           | 5.5          | V       |  |

| IP <sub>3</sub> | DC supply current of the 3.3 digital core part                   | high activity of the DSP at 31 MHz DSP frequency                               | -   | 57.4        | 78           | mA      |  |

| IP <sub>5</sub> | DC supply current of the 5V digital periphery part               | Without external load to ground                                                | -   | 5           | 7            | mA      |  |

| IP <sub>A</sub> | DC supply current of the analog part                             | At zero input and output signal                                                | -   | 16.5        | 22.6         | mA      |  |

| Ptot            | Total power dissipation                                          | high activity of the DSP at 31 MHz DSP frequency                               | -   | 0.273       | 0.423        | W       |  |

| ADSNR           | Level AD converter SNR<br>RMS (unweighted)                       | BW=0-29 kHz Max. input                                                         | 48  | 54          | -            | dB      |  |

| ADICL           | Input voltage range level AD for full scale                      |                                                                                | 0   | -           | VDDA1        | V       |  |

| AITHDM          | THD FM_MPX input                                                 | 1 kHz 1.1 Vrms, BW= 19 kHz, I <sup>2</sup> C default setting                   | -   | -70<br>0.03 | -65<br>0.056 | dB<br>% |  |

| AISNRM          | SNR FM_MPX input mono                                            | 1 kHz, BW=19 kHz, 0 dB ref. = 1.1 Vrms, I <sup>2</sup> C default setting       | 80  | 83          | -            | dB      |  |

| AISNRSS         | SNR FM_MPX input stereo                                          | 1 kHz, BW=40 kHz, 0 dB<br>ref. = 1.1 Vrms, I <sup>2</sup> C default<br>setting | 74  | 77          | -            | dB      |  |

| AITHDC          | THD CD Inputs, not multiplex mode                                | 1 kHz, 0.55Vrms, BW=20<br>kHz                                                  | -   | -80<br>0.01 | -76<br>0.016 | dB<br>% |  |

| AISNRC          | SNR CD Input, not multiplex mode                                 | 1 kHz, BW=20 kHz, 0 dB<br>ref.= 0.55 Vrms                                      | 81  | 84          | -            | dB      |  |

| AITHDA          | THD AM mono input, not multiplex                                 | 1 kHz, 0.55 Vrms, BW=5 kHz                                                     | -   | -80<br>0.01 | -76<br>0.016 | dB<br>% |  |

| AISNRA          | SNR AM mono input, not multiplex                                 | 1 kHz, BW=5 kHz, 0dB ref.<br>= 0.55 Vrms                                       | 83  | 88          | -            | dB      |  |

| AITHDT          | THD Tape input, multiplex mode                                   | 1 kHz, BW = 20 kHz, 0.55<br>Vrms                                               |     | -80<br>0.01 | -76<br>0.016 | dB<br>% |  |

| AISNRT          | SNR Tape input, multiplex mode                                   | 1 kHz, BW= 20 kHz, 0 dB<br>ref. = 0.55 Vrms                                    | 70  | 77          | -            | dB      |  |

| AILVL           | conversion input level                                           | THD < 1%                                                                       | 0.6 | 0.66        | -            | Vrms    |  |

| THD&N/S         | DAC total harmonic<br>distortion + noise vs<br>Output Signal DAC | Rload AC> 5 k $\Omega$ , f=1 kHz                                               | -   | -75         | -65          | dBA     |  |

| DRAN            | DAC Dynamic Range                                                | f = 1 kHz, -60 dB                                                              | 92  | 102         | -            | dBA     |  |

Philips Semiconductors Preliminary specification

## Car Radio Digital Signal Processor

## **SAA7708H**

| SYMBOL  | PARAMETER                | CONDITIONS                    | MIN  | TYP     | MAX | UNIT |

|---------|--------------------------|-------------------------------|------|---------|-----|------|

| DSIL    | DAC Digital Silence      | f=20 Hz-17 kHz A-<br>weighted | -102 | -108    | -   | dBA  |

| XTFREQ  | X-tal frequency          |                               |      | 11.2896 |     | MHz  |

| DSPFREQ | Clock Frequency DSP core |                               |      | 31.0464 | -   | MHz  |

## 6 ORDERING INFORMATION

| EXTENDED TYPE | PACKAGE |              |          |           |  |

|---------------|---------|--------------|----------|-----------|--|

| NUMBER        | PINS    | PIN POSITION | MATERIAL | CODE      |  |

| SAA7708H      | 80      | QFP          | plastic  | SOT318D4C |  |

**SAA7708H**

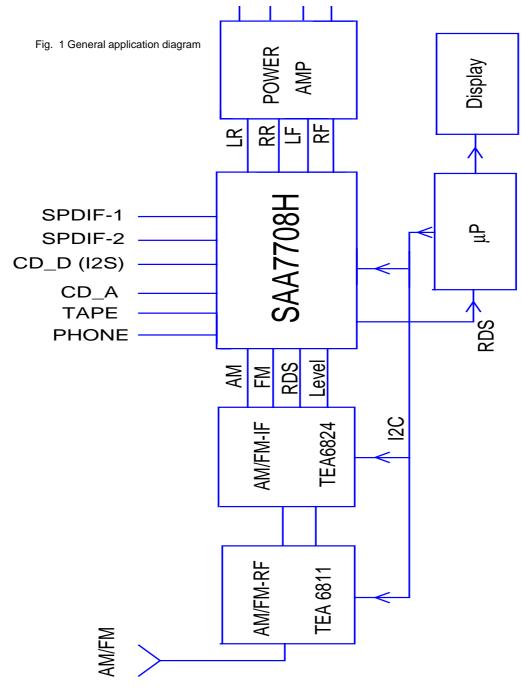

#### 7 APPLICATION BLOCK DIAGRAM

## **SAA7708H**

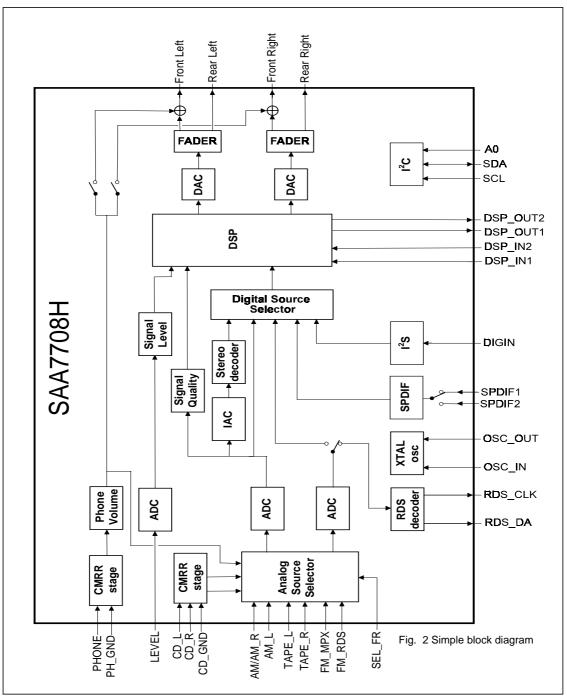

#### 8 BLOCK DIAGRAM

9

**SAA7708H**

#### 9 PINNING

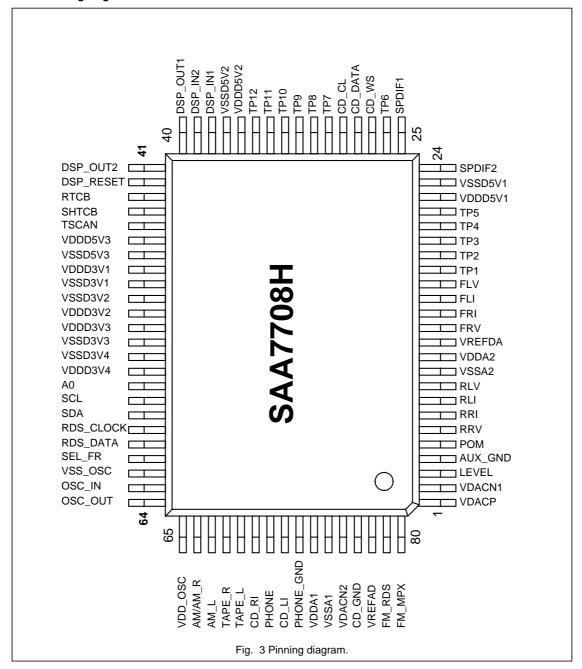

#### 9.1 Pinning diagram

**SAA7708H**

Pinning Table

Pin list SAA7708

| SYMBOL  | PIN | DESCRIPTION                                                                                                                                                                 | PIN      |

|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|         |     |                                                                                                                                                                             | TYPE     |

| VDACP   | 1   | Positive reference voltage SCAD1, SCAD2 and Level AD                                                                                                                        | AP2D     |

| VDACN1  | 2   | Ground reference voltage 1 SCAD1, SCAD2 and Level AD                                                                                                                        | AP2D     |

| LEVEL   | 3   | FM/AM-level input pin. Via this pin the level of the FM signal or level of the AM signal is fed to the CDSP. The level information is used in the DSP for signal correction | AP2D     |

| AUX_GND | 4   | By I2C switchable common mode reference pin to enable an arbitrary high common mode analog input.                                                                           | AP2D     |

| POM     | 5   | Power on Mute of the FADER DAC. Timing is determined by an external capacitor.                                                                                              | APR2D    |

| RRV     | 6   | Rear Right audio voltage output of the FADER DAC                                                                                                                            | AP2D     |

| RRI     | 7   | Rear Right audio current output of the FADER DAC                                                                                                                            | APR2D    |

| RLI     | 8   | Rear Left audio current output of the FADER DAC                                                                                                                             | APR2D    |

| RLV     | 9   | Rear Left audio voltage output of the FADER DAC                                                                                                                             | AP2D     |

| VSSA2   | 10  | Ground supply analog part of the FADER DAC and SPDIF bitslicer                                                                                                              | APVSS    |

| VDDA2   | 11  | 3V positive supply analog part of the FADER DAC and SPDIF bitslicer                                                                                                         | APVDD    |

| VREFDA  | 12  | Voltage reference of the analog part of the FADER DAC                                                                                                                       | AP2D     |

| FRV     | 13  | Front Right audio voltage output of the FADER DAC                                                                                                                           | AP2D     |

| FRI     | 14  | Front Right audio current output of the FADER DAC                                                                                                                           | APR2D    |

| FLI     | 15  | Front Left audio current output of the FADER DAC                                                                                                                            | APR2D    |

| FLV     | 16  | Front Left audio voltage output of the FADER DAC                                                                                                                            | AP2D     |

| TP1     | 17  | Test pin, may not be connected in the application                                                                                                                           | BT4CR    |

| TP2     | 18  | Test pin, may not be connected in the application                                                                                                                           | BT4CR    |

| TP3     | 19  | Test pin, may not be connected in the application                                                                                                                           | BT4CR    |

| TP4     | 20  | Test pin, may not be connected in the application                                                                                                                           | BT4CR    |

| TP5     | 21  | Test pin, may not be connected in the application                                                                                                                           | BD4CR    |

| VDDD5V1 | 22  | 5V positive supply 1 peripheral cells only                                                                                                                                  | VDDE5    |

| VSSD5V1 | 23  | Ground supply 1 of 5 volt peripheral cells only                                                                                                                             | VSSE5    |

| SPDIF2  | 24  | Analog bitslicer input2 for SPDIF, can be selected i.s.o. SPDIF1 via I2C bit                                                                                                | APR2D    |

| SPDIF1  | 25  | Analog bitslicer input1 for SPDIF, can be selected i.s.o. SPDIF2 via I2C bit                                                                                                | APR2D    |

| TP6     | 26  | Test pin, may not be connected in the application                                                                                                                           | SCHMITCD |

| CD_WS   | 27  | I <sup>2</sup> S or LSB justified format Word select input from a digital audio source                                                                                      | SCHMITCD |

| CD_DATA | 28  | I <sup>2</sup> S or LSB justified format Left-Right Data input from a digital audio source                                                                                  | SCHMITCD |

| CD_CL   | 29  | I <sup>2</sup> S Clock or LSB justified format input from a digital audio source                                                                                            | SCHMITCD |

| TP7     | 30  | Test pin, may not be connected in the application                                                                                                                           | BD4CRD   |

| TP8     | 31  | Test pin, may not be connected in the application                                                                                                                           | SCHMITCD |

| TP9     | 32  | Test pin, may not be connected in the application                                                                                                                           | SCHMITCD |

## **SAA7708H**

| SYMBOL    | PIN | DESCRIPTION                                                                                                                                                                                                                                                                                        | PIN      |

|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|           |     |                                                                                                                                                                                                                                                                                                    | TYPE     |

| TP10      | 33  | Test pin, may not be connected in the application                                                                                                                                                                                                                                                  | BD4CRD   |

| ΓP11      | 34  | Test pin, may not be connected in the application                                                                                                                                                                                                                                                  | BD4CRD   |

| ΓP12      | 35  | Test pin, may not be connected in the application                                                                                                                                                                                                                                                  | SCHMITCD |

| /DDD5V2   | 36  | 5V positive supply 2 peripheral cells only                                                                                                                                                                                                                                                         | VDDE     |

| /SSD5V2   | 37  | Ground supply 2 of 5 volt peripheral cells only                                                                                                                                                                                                                                                    | VSSE     |

| OSP-IN1   | 38  | Digital input 1 of the DSP-core (F0 of the status register). Level must always be defined externally in the application.                                                                                                                                                                           | SCHMITC  |

| DSP-IN2   | 39  | Digital input 2 of the DSP-core (F1 of the status register). Level must always be defined externally in the application.                                                                                                                                                                           | SCHMITC  |

| OSP-OUT1  | 40  | Digital output 1 of the DSP-core (F2 of the status register)                                                                                                                                                                                                                                       | B4CR     |

| OSP-OUT2  | 41  | Digital output 2 of the DSP-core (F3 of the status register)                                                                                                                                                                                                                                       | B4CR     |

| OSP-RESET | 42  | Reset of the DSP core (active low)                                                                                                                                                                                                                                                                 | IBUFU    |

| RTCB      | 43  | Asynchronous Reset Test Control Block active low, connect to ground                                                                                                                                                                                                                                | SCHMITCD |

| SHTCB     | 44  | Shift Clock Test Control Block, connect to ground                                                                                                                                                                                                                                                  | SCHMITCD |

| rscan .   | 45  | Scan control active high, connect to ground                                                                                                                                                                                                                                                        | SCHMITCD |

| /DDD5V3   | 46  | 5V positive supply 3 peripheral cells only                                                                                                                                                                                                                                                         | VDDE5    |

| /SSD5V3   | 47  | Ground supply 3 of 5 volt peripheral cells only                                                                                                                                                                                                                                                    | VSSE5    |

| /DDD3V1   | 48  | 3V positive supply 1 core only                                                                                                                                                                                                                                                                     | VDDI3    |

| /SSD3V1   | 49  | Ground supply 1 of 3 volt core only                                                                                                                                                                                                                                                                | VSSI3    |

| /SSD3V2   | 50  | Ground supply 2 of 3 volt core only                                                                                                                                                                                                                                                                | VSSI     |

| /DDD3V2   | 51  | 3V positive supply 2 core only                                                                                                                                                                                                                                                                     | VDDI3    |

| /DDD3V3   | 52  | 3V positive supply 3 core only                                                                                                                                                                                                                                                                     | VDDI3    |

| /SSD3V3   | 53  | Ground supply 3 of 3 volt core only                                                                                                                                                                                                                                                                | VSSI3    |

| /SSD3V4   | 54  | Ground supply 4 of 3 volt core only                                                                                                                                                                                                                                                                | VSSI3    |

| /DDD3V4   | 55  | 3V positive supply 4 core only                                                                                                                                                                                                                                                                     | VDDI3    |

| 40        | 56  | Slave sub-address I <sup>2</sup> C selection / Serial data input test control block                                                                                                                                                                                                                | SCHMITCD |

| SCL       | 57  | Serial clock input I <sup>2</sup> C bus                                                                                                                                                                                                                                                            | SCHMITC  |

| SDA       | 58  | Serial data input / output I <sup>2</sup> C bus                                                                                                                                                                                                                                                    | BD4SCI4  |

| RDS_CLOCK | 59  | Radio Data System bit clock output / RDS external clock input                                                                                                                                                                                                                                      | BD4CR    |

| RDS_DATA  | 60  | Radio Data System data output                                                                                                                                                                                                                                                                      | B4CR     |

| SEL_FR    | 61  | AD input selection switch to enable high ohmic FM_MPX input at fast tuner search on FM_RDS input. At switch to '1' the input of the FM_RDS is put through to the MPX input of the dowsample filters and FM_MPX inputs gets high ohmic. Level must always be defined externally in the application. | SCHMITC  |

| VSS_OSC   | 62  | Ground supply crystal oscillator circuit                                                                                                                                                                                                                                                           | APVSS    |

| OSC_IN    | 63  | Crystal oscillator input: crystal oscillator sense for gain control or forced input in slave mode                                                                                                                                                                                                  | APR2D    |

| OSC_OUT   | 64  | Crystal oscillator output: Drive output to 11.2896 MHz crystal                                                                                                                                                                                                                                     | AP2D     |

| VDD_OSC   | 65  | 3V positive supply crystal oscillator circuit                                                                                                                                                                                                                                                      | APVDD    |

## SAA7708H

| SYMBOL    | PIN | DESCRIPTION                                                             | PIN   |

|-----------|-----|-------------------------------------------------------------------------|-------|

|           |     |                                                                         | TYPE  |

| AM/AM_R   | 66  | Analog input pin for AM audio frequency Right Channel or AM mono input! | AP2D  |

| AM_L      | 67  | Analog input pin for AM audio frequency Left Channel                    | AP2D  |

| TAPE_R    | 68  | Input of the analog TAPE Right signal                                   | AP2D  |

| TAPE_L    | 69  | Input of the analog TAPE Left signal                                    | AP2D  |

| CD_RI     | 70  | Input of the analog CD Right signal                                     | AP2D  |

| PHONE     | 71  | Input of common mode phone signal                                       | AP2D  |

| CD_LI     | 72  | Input of the analog CD Left signal                                      | AP2D  |

| PHONE_GND | 73  | The common mode reference pin of the phone signal                       | AP2D  |

| VDDA1     | 74  | Positive supply analog SCAD1, SCAD2 and Level AD.                       | APVDD |

| VSSA1     | 75  | Ground supply analog SCAD1, SCAD2 and Level AD.                         | APVSS |

| VDACN2    | 76  | Ground reference voltage 2 SCAD1, SCAD2 and Level AD                    | AP2D  |

| CD_GND    | 77  | The common mode reference pin of the CD_AD LEFT and CD_AD RIGHT block   | AP2D  |

| VREFAD    | 78  | Common mode reference voltage SCAD1, SCAD2 and Level AD                 | AP2D  |

| FM_RDS    | 79  | Analog input pin for FM RDS signal                                      | AP2D  |

| FM_MPX    | 80  | Analog input pin for FM-Multiplex signal                                | AP2D  |

Table 1 Brief explanation of used pin types

| PIN TYPE | EXPLANATION                                                                      |

|----------|----------------------------------------------------------------------------------|

| AP2D     | Analog IO (Input/Output)                                                         |

| APR2D    | Analog IO with series resistor and clamp device                                  |

| APVDD    | Analog SUPPLY                                                                    |

| APVSS    | Analog GROUND                                                                    |

| VDDE5    | 5 Volt Peripheral only supply ring                                               |

| VSSE5    | 5 Volt Peripheral only gound connection, no connection to substrate              |

| VDDI3    | 3.3 Volt SUPPLY to digital core and internal IO pads                             |

| VSSI3    | 3.3 Volt GROUND to digital core and internal IO pads, no substrate connection    |

| VSSI     | 3.3 Volt GROUND to digital core and internal IO pads with substrate connection   |

| SCHMITC  | CMOS Schmitt trigger input                                                       |

| SCHMITCD | CMOS, Schmitt trigger input with active pull-down to VSSE5                       |

| IBUFD    | CMOS, active pull-down to VSSE5                                                  |

| IBUFU    | CMOS, active pull-up to VDDE5                                                    |

| BD4CR    | Bidirectional CMOS IO buffer, 4 mA, slew rate control                            |

| BD4CRD   | Bidirectional CMOS IO buffer, 4 mA, slew rate control, active pull down to VSSE5 |

| BT4CR    | 4mA CMOS tristate ouput buffer, slew rate control                                |

| B4CR     | 4mA CMOS ouput buffer, slew rate control                                         |

| BD4SCI4  | CMOS IO pad with open drain output                                               |

**SAA7708H**

#### 10 FUNCTIONAL DESCRIPTION

#### 10.1 Signal path for Level information

For FM weak signal processing, for AM and FM purposes (absolute level and multipath) a FM/AM Level input is implemented (pin LEVEL). In the case of radio reception the clocking of the filters and the AD is based on a 38 kHz Fs frequency. A DC input signal is converted by a bitstream first order Sigma-Delta AD converter followed by a decimation filter.

The input signal has to be obtained from a radio part. The tuner must deliver the level information of either AM or FM to the LEVEL pin.

#### 10.1.1 THE VREFAD PIN

Via this pin the Midref voltage of the AD's is filtered. This Midref voltage is used as reference of the LEVEL AD and half supply reference of the two third order switch capacitor ADs. External capacitors (connected to VSSA1) prevents crosstalk between the AD's. This pin must also used in the application as reference for the inputs AM/AM\_R, AM\_L, , TAPE\_L and TAPE\_R (see Fig. 21).

#### 10.2 Signal path of the third order switched capacitor AD's.

#### 10.2.1 THE FM MPX SIGNAL PATH

The CDSP has in total three analog audio source channels. One of the analog inputs is the FM\_MPX signal. Selection of this signal is achieved according Table 3. The multiplex FM signal is converted to the digital domain in SCAD1, a bitstream third order switched capacitor AD converter. A decimation filter reduces the output of the AD to a lower sample rate. From this filter the following signals are derived and are processed in the DSP.

The outputs from this signal path to the DSP which are all running on a sample frequency of 38 kHz are:

- Pilot presence indication: Pilot-I. This one bit signal is low for a pilot frequency deviation < 3 kHz and high for a pilot frequency deviation > 3 kHz AND the FM MPX stereodecoder is locked on a pilot tone.

- 'Left' and 'Right' FM reception stereo signal: This is the 18 bit output of the stereo decoder after the matrix decoding in ISN I<sup>2</sup>S format. This signal is fed via a muxer to a general I<sup>2</sup>S interface block that communicates with the DSP.

- A noise level information. This signal is derived from the first MPX decimation fiter via a wide band noise filter.

Detection is done with an envelope detector. This noise level is filtered in the DSP core and is used to optimize the FM weak signal processing.

Normally the FM\_MPX input and the FM\_RDS input have the same source. If the FM input contains a stereo radio channel, the pilot information is used to lock the clocking of the decimation filters of FM MPX and RDS path and also the stereo decoder.

#### 10.2.2 INPUT SENSITIVITY FOR FM AND RDS

The FM and RDS input sensitivity is designed for tuner front ends which deliver an output voltage of 200 mVrms at a modulation depth of 22.5 kHz of a 1 kHz tone. In this case the I<sup>2</sup>C bit pcs\_ad\_sel must be 'o' and the SEL\_FR switch is also low. The MPX part of the FM\_MPX signal will be processed via SCAD1, the RDS part is processed via SCAD2...

Another input sensitivity can be obtained by putting the pcs\_ad\_sel bit high. Biasing of this input must now take place exterenally via high-ohmic resistors connected to the VREFAD pin. In this case the input sensitivity has increased from 200 mVrms to 65 mVrms at modulation depth of 22.5 kHz. Reduction of the input sensitivity can be obtained by an external resistor tap consisting of an in the signal path placed series resistor and a resistor to VREFAD.

#### 10.2.3 THE SIGNAL FLOW OF THE AM, CD ANALOG AND TAPE

The signal AM mono via the AM/AM\_R input can be selected by the correct values of the I<sup>2</sup>C bits. There is also an option available to connect a left and right signal to the chip. This can be for instance the AM-Right and AM-Left signal. The AM, TAPE and CD inputs are buffered by an opamp to ensure a high ohmic input that makes external signal reduction

**SAA7708H**

possible via an external resistor divider. For correct biasing of the first input buffer it is obligatory to connect the resistor between the tap and the virtual ground of the VREFAD pin (see Fig. 28). The way to make a high common mode input is described in chapter 10.2.5.

**SAA7708H**

#### 10.2.4 ANALOG SOURCE SWITCHING

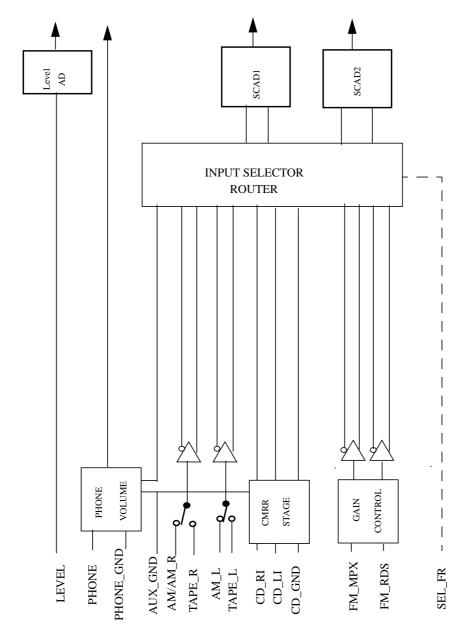

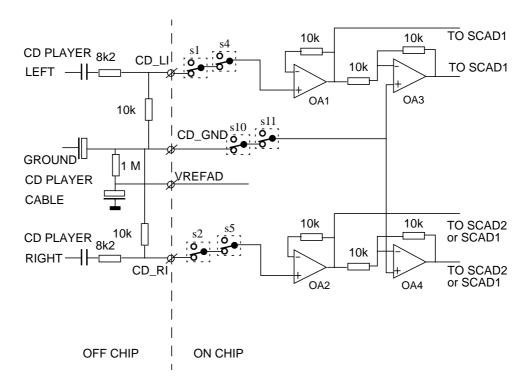

Fig. 4 Analog input switching circuit

## **SAA7708H**

#### 10.2.5 THE REALISATION OF COMMON MODE INPUTS

A high Common Mode Rejection Ratio can be created by the use of the either the AUX\_GND or the CD\_GND pin. One of these pins can be connected via the switches s10 and s11 (see Fig. 5) to the plus input of the second opamp in the signal path of TAPE, CD or AM. The signal of which a high common mode rejection ratio is required has one signal (or two signals) and a common signal as input. The common signal is connected to either the AUX\_GND or CD\_GND input and for the specific mode selected with the switches 10 and 11. This means that on both signal lines going to the SCAD will contain the common mode signal. The AD's itself will suppress this common mode signal very effectively and this is the way good common mode signal suppression is achieved. The switches needed are drawn in the appropriate position. The inputs CD\_LI and CD\_RI get in this example a diminished input signal by the external resistor tap of 8k2 and 10k. The 10k resistors provides together with the 1 M resistor from CD\_GND to VREFAD also the biasing of the opamps OA1 and OA2. If no external resistor tap is needed still resistors will be needed between the signal inputs and the CD\_GND pin. The CD\_GND pin is in this configuration connected to the plus input of the opamps OA3 and OA4. Biasing of the opamps OA3 and OA4 is again provided by the 1 M resistor to VREFAD. In this construction the common mode signals on CD\_LI / CD\_RI and the CD\_GND pin will be unchanged in amplitude being present at the AD input and the common mode rejection behaviour of these AD will provide a good common mode rejection ratio. The other common mode input AUX\_GND can in the same way be used.

Fig. 5 Example of the use of common mode analog input

**SAA7708H**

#### 10.2.6 PHONE INPUT WITH VOLUME CONTROL

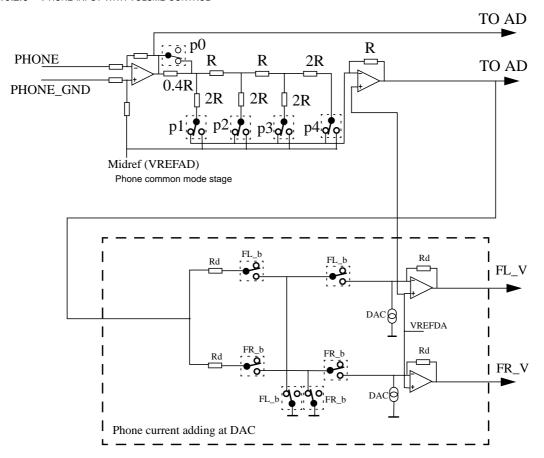

Fig. 6 Volume control setting of PHONE input

A common mode input with volume control for mixing to the Front Left or Front Right or both DAC outputs is provided. The inputs consist of a PHONE input for the signal and a PHONE\_GND to be connected to the ground shield of the PHONE cable. By means of two opamps the signal is then converted to a signal with better common mode rejection ratio. Via the switches s6\_7 and the multiplex switch in front of the SCAD1 this signal can be processed via the AD signal path. In that case the resistor volume control must be put in an all '00000' position of the I2C bits p4-p0 meaning 0 dB pass through mode (see Fig. 6). Although in this way signal improvement with the DSP can be done, mixing with other analog sources is not possible. Another signal path is the R 2R volume setting block to the DAC current input. The signal from the phone opamp is converted via a R-2R ladder network to a voltage. This voltage can be controlled with the I2C bits p4,p3,p2,p1,p0 according Table 2. This voltage can be connected to two resistors in the DAC block via the I2C controlled switches FL\_b and FR\_b. The two resistors convert the voltage to a current an this current is added to the already present current of the Front Left DA and/or the Front Right DA. This is the way the phone signal is mixed with the DAC signal in the analog domain.

**SAA7708H**

Table 2 Volume settings of the PHONE input (\$0FFE)

| VOL_PHONE BITS<br>P4,P3,P2,P1,P0 | FL AND FR OUTPUT (DB) |

|----------------------------------|-----------------------|

| 00000                            | 0                     |

| 00001                            | -3                    |

| 00010                            | -6                    |

| 00011                            | -9                    |

| 00110                            | -12                   |

| 01110                            | -15                   |

| 01111                            | -18                   |

| 01111                            | -21                   |

| 1111*                            | MUTE                  |

#### 10.3 Input selection switches

In Fig. 4 a block diagram of the input is shown. The input selection is controlled by bits in the input selector control register and the input pin SEL\_FR. The relation between these bits and the switches is indicated in table 3. This table is not 100% elaborated but gives an idea of the switching possibilities.

**Table 3** Analog input selection via I<sup>2</sup>Cbits (\$0FFD) signal destination

| MODE                        | pcs_ad<br>_sel | en_38<br>_clk | sw_<br>ad1 | rds_cd<br>_sel | s1_2 | s4_5 | s6_7 | s8_9 | wide_<br>narrow |

|-----------------------------|----------------|---------------|------------|----------------|------|------|------|------|-----------------|

| FM_MPX +<br>RDS mode        | 0              | 0             | 0          | 0              | d    | d    | d    | 0    | 0               |

| 200 mV                      |                |               |            |                |      |      |      |      |                 |

| FM_MPX +<br>RDS mode        | 1              | 0             | 0          | 0              | d    | d    | d    | 0    | 0               |

| AM mono +<br>RDS            | 0 or 1         | 0             | 0          | 0              | 0    | 1    | d    | 1    | 0               |

| AM stereo +<br>RDS          | 0 or 1         | 1             | d          | 0              | 0    | 1    | 0    | 1    | 0               |

| TAPE<br>STEREO +<br>RDS     | 0 or 1         | 1             | d          | 0              | 1    | 0    | 0    | 1    | 0               |

| CD-ANALOG<br>+ RDS          | 0 or 1         | 1             | d          | 0              | 0    | 0    | 0    | 1    | 0               |

| CD ANALOG                   | d              | 0             | 1          | 1              | 0    | 0    | 0    | d    | 1               |

| PHONE via<br>SCAD1 +<br>RDS | 0 or 1         | 0             | 1          | 0              | d    | d    | 1    | d    | 0               |

<sup>•</sup> In all the positions above one supposes that the SEL\_FR pin is low.

The switches s10 and s11 must be switched according the position needed for the correct common mode rejection ratio of the chosen input e.g. s10=0 and s11=1 in case of CD analog input.

**SAA7708H**

#### 10.4 Supply of the analog inputs

The analog input circuit has separate power supply connections to allow maximum filtering. These pins are the VSSA1 for the analog ground and the VDDA1 for the analog power supply.

#### 10.5 The DCS clock block

For the digital stereo decoder a clock signal is needed which is the 512 multiple of the pilot tone frequency of the FM MPX signal. This is done by the DCS clock block, which generates this 512 \* 19 kHz = 9.728 MHz clock, the DCS clock, by locking to the pilot frequency. This block is also able to generate other frequencies and controlling is done via a number of I<sup>2</sup>C bits of the registers in Table 21 and Table 22. Default I<sup>2</sup>C settings of the DCS and the PLL guarantee correct functioning of the DCS block.

#### 10.6 Synchronization with the DSP core

The system can run in case of I<sup>2</sup>S input on different audio sample frequencies of Fs=32kHz, 38 kHz, 44.1 kHz or 48 kHz. After each processing period of one input sample with this signal, the Input flag (I-flag) of the status register of the DSP core is set on the falling edge of the I2S WS to I=1 during 4 clock cycles. This flag can be tested with a conditional branch instruction in the DSP. This synchronisation starts really in parallel with the input signal due to the short period that the I flag is set. It is obvious that the higher the Fs the lower the number of cycles available in the DSP program..

#### 10.7 IAC

#### 10.7.1 GENERAL DESCRIPTION

The Interference Absorption Circuit (IAC) detects and suppresses ignition interference. This hardware IAC is a modified, digitized and extended version of the analog circuit which is in use for many years already.

The IAC consists of an MPX mute function switched by mute pulses from ignition interference pulse detectors. All IAC functions must be switched off if there is no FM MPX signal processing.

The input signal of a first IAC detection circuit is the output signal of ADF1. This interference detector analyses the high frequency contents of the MPX signal. The discrimination between interference pulses and other signals is performed by a special Philips patented fuzzy logic like algorithm and is based on probability calculations. This detector performs optimally in higher antenna voltage circumstances. On detection of ignition interference, this logic will send appropriate pulses to the MPX mute switch.

The input signal of a second IAC detection circuit is the LEVEL signal (the output of the Level AD). This detector performs optimally in lower antenna voltage circumstances. It is therefore complementary to the first detector.

The characteristics of both IAC detectors can be adapted to the properties of different FM front ends by means of the predefined coefficients in the IAC control registers. The values can be changed via the I<sup>2</sup>C bus. Both IAC detectors can be switched on or off independently of each other. Both IAC detectors can mute the MPX signal independently of each other.

A third IAC function is the Dynamic IAC circuit. This block is intended to switch off the IAC completely the moment the MPX signal has a too high frequency deviation which in case of narrow IF filters can result in AM modulation. This AM modulation could be interpreted by the IAC circuitry as interference caused by the car's engine.

AM IAC is also implemented. In this case only the AM mono signal is monitored by the on the DSP processor running program. Input from the LEVEL pin is not used.

#### 10.7.2 PARAMETER SETTING FOR THE MPX INPUT IGNITION DETECTOR

There are in total 5 different coefficients. The settings of these coefficients are described below. On RESET, the nominal setting for a good performing MPX IAC detector is selected.

**SAA7708H**

#### 10.7.3 AGC SET POINT (1 BIT)

In case the sensitivity and feed forward factor are out of range in a certain application, the set point of the AGC can be shifted. The set point controls the sensitivity of the other IAC control parameters. See bit 11 of \$0FFB (Table 25).

#### 10.7.4 THRESHOLD SENSITIVITY OFFSET (3 BITS)

With this parameter the threshold sensitivity of the comparator in the interfering pulse detectors can be set. It also influences the amount of unwanted triggering. Settings are according Table 31.

#### 10.7.5 DEVIATION FEED FORWARD FACTOR (3 BITS)

This parameter determines the reduction of the sensitivity of the detector by the absolute value of the MPX signal. This mechanism prevents the detector from unwanted triggering at noise with modulation peaks. In Table 32 the possible values are given.

#### 10.7.6 SUPPRESION STRETCH TIME (3 BITS)

This parameter sets the duration of the pulse suppression after the detector has stopped sending a trigger pulse. It can be switched off by applying the value 0. The duration can be selected in steps of one period of the 304 kHz (3.3  $\mu$ s) sample frequency. In Table 33 the possible values are given.

#### 10.7.7 MPX DELAY

With this parameter the delay time between 2 and 5 samples of the 304 kHz sample frequency can be selected. The needed value depends on the used front end of the car radio. Settings are according Table 34.

#### 10.7.8 LEVEL IAC THRESHOLD (4 BITS)

With this parameter the sensitivity of the comparator in the ignition interference pulse detector can be set. It also influences the amount of unwanted triggering. The possible values are given in Table 26. The prefix value '0000' switches the Level IAC function off.

#### 10.7.9 Level IAC feed forward setting (2 bits)

This parameter allows to adjust for delay differences in the signal paths from the FM antenna to the MPX mute, namely, via the FM level ADC and level IAC detection and via the FM demodulator and MPX conversion and filtering. These differences depend on the front end used in the car radio. With a simultaneous appearance of a peak disturbance at the LEVEL input and the MPX ADC input of the chip, a zero delay setting will make for the level IAC mute pulse to coincide with the passage of the disturbance in the MPX mute circuit. The setting for the Level IAC Feed Forward allows to advance the mute pulse by 1 sample period or to delay it by 1 or 2 sample periods of the 304 kHz clock, with respect to the default. The appropriate I<sup>2</sup>C bits for each setting are given in Table 27.

#### 10.7.10 LEVEL IAC SUPPRESSION STRETCH TIME (2 BITS)

This parameter sets the time the mute pulse is stretched when the LEVEL input has stopped exceeding the threshold. The duration can be selected in steps of one period of the 304 kHz (3.3  $\mu$ s) sample frequency. In Table 28 the possible values are given

#### 10.7.11 DYNAMIC IAC THRESHOLD LEVELS

If enabled by the lev\_en\_dyn\_iac I<sup>2</sup>C bit (bit 15, register \$0FFC) this block will disable temporarily all IAC action if the MPX mono signal exceeds a threshold deviation (threshold 1) for a given time with a given excess amount (threshold 2). This MPX mono signal is separated from the MPX signal with a low-pass filter with the - 3 dB corner point at 15 kHz. The possible values of the this threshold can be found in Table 29.

**SAA7708H**

#### 10.7.12 IAC TESTING

The internal IAC trigger signal is visible on DSP-OUT2 pin if the IAC\_trigger bit of the IAC control register is set. In this mode the effect of the parameter settings on the IAC performance can be verified.

#### 10.8 Analog outputs

#### 10.8.1 D/A CONVERTERS

Each of the two low noise high dynamic range D/A convertors consists of a 15 bit signed magnitude DAC with current output. This DAC current is split in two parts by means of a fader. Each part of the current is fed to an operational amplifier, which converts the current into an output voltage. The fader makes it possible to make 4 outputs with only two DACS.

#### 10.8.2 UPSAMPLE FILTER

To reduce spectral components above the audio band, a fixed 4 times oversampling and interpolating 18 bits digital IIR filter is used. It is realised as a bit serial design and consists of two consecutive filters. The data path in these filters is 22 bits to prevent overflow and to maintain a theoretical SNR above 105 dB.

The word clock for the upsample filter (4\*asf) is derived from the audio source timing. If the internal audio source is selected, the sample frequency can be either 44.1 kHz or 38 kHz. In case of external digital sources (CD1, SPDIF), a sample frequency from 32 kHz to 48 kHz is possible.

#### 10.8.3 VOLUME CONTROL

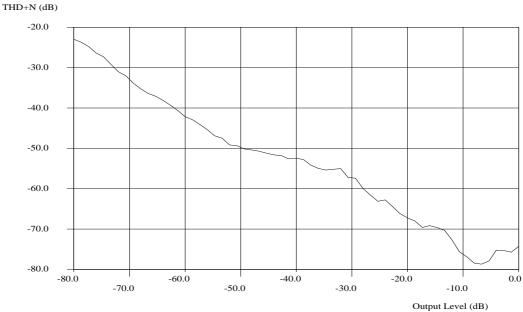

Fig. 7 Typical THD+N curve versus output level

The total volume control has a dynamic range of more than 100 dB. With the signed magnitude noise shaped 15 bit DAC and the internal 18 bits registers of the DSP core a useful digital volume control range of 100 dB is possible by calculating

**SAA7708H**

the corresponding coefficients. The step size is freely programmable and an additional analog volume control is not needed in this design. The SNR of the audio output at full scale is determined by the total 15 bits of the converter. The noise at low outputs is fully determined by the noise performance of the DAC. Since it is a signed magnitude type, the noise at digital silence is also low. As disadvantage the total THD is slightly higher than conventional D/A converters. The typical Signal to Noise and THD versus output level are shown in Fig. 7.

#### 10.8.4 FUNCTION OF THE POM PIN

With the POM pin it is possible to switch off the reference current source of the D/A converter. The capacitor on the POM pin determines the time after which this current has a soft switch-on. So at power-on the current audio signal outputs are always muted. The loading of the external capacitor is done in two stages via two different current sources. The loading starts at a current level that is 9 times lower than the current loading after the POM pin voltage has past the 1 V level. This results in an almost dB linear behaviour. However the DAC has an a-symmetrical supply and the DC output voltage will be half the supply voltage under functional conditions. During startup the output voltage is not defined as long as the supply voltage is lower than the threshold voltages of the transistors and a small jump in DC is possible at startup. In this DC voltage jump audio components can be present.

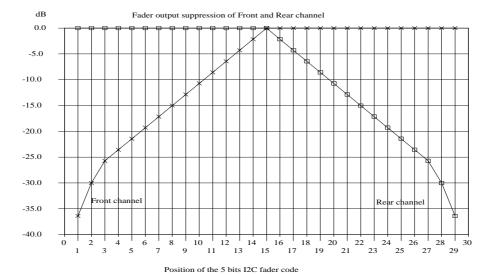

#### 10.8.5 THE FADER

The fader is a 5 bit I2C (bits 11-15 of \$0FFC) controlled volume regulator between the front and the rear outputs. Of the 32 positions of the 5 bit I2C code position 15 is the default position in which front and rear output have the same volume (Fig. 8). Increasing the 5 bits I2C code will keep the front channels at the same volume but will decrease the volume of the rear channels. Decreasing the 5 bits code starting at position 15 will keep the rear channels at the same volume but will decrease the volume of the front channels. Starting at the default position the first 12 steps decrease the volume linearly to -26 dB, step 13 and 14 decrease until -37 dB. The positions 0 and 30 of the fader represent mute for the front-and rear channel respectively. Position 31 is not used.

Fig. 8 DAC fader control range

**SAA7708H**

#### 10.8.6 POWER OFF PLOP SUPPRESSION

To reduce the chance of plops in a power amplifier, the supply voltage of the analog part of the D/A converter can be fed from the 5V via a transistor. An capacitor is connected to the 3.3 V to provide still power to the analog part the moment the digital is switching off fast. In this case the output voltage will decrease gradually allowing the power amplifier some extra time to switch off without audible plops.

#### 10.8.7 THE INTERNAL VREFDA PIN

With two internal resistors half the supply voltage VDDA2 is obtained and coupled to an internal buffer. This reference voltage is used as DC voltage for the output operational amplifiers and as reference for the DAC. In order to obtain the lowest noise and to have the best ripple rejection, a filter capacitor has to be added between this pin and ground.

#### 10.8.8 SUPPLY OF THE ANALOG OUTPUTS

All the analog circuitry of the DACs and the OPAMPS are fed by 2 supply pins, VDDA2 and VSSA2. The VDDA2 must have sufficient decoupling to prevent THD degradation and to ensure a good Power Supply Rejection Ratio. The digital part of the DAC is fully supplied from the chip core supply.

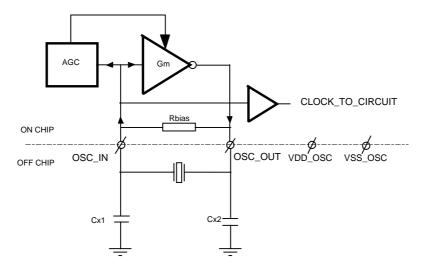

#### 10.9 Clock circuit and oscillator

The chip has an on board crystal clock oscillator. The block schematic of this Pierce oscillator is shown in Fig. 9. The active element needed to compensate for the loss resistance of the crystal is the block Gm. This block is placed between the external pins OSC\_IN and OSC\_OUT. The gain of the oscillator is internally controlled by the AGC block. A sine-wave with peak to peak voltage close to the oscillator power supply voltage is generated. The AGC block prevents clipping of the sine-wave and therefore the higher harmonics are as low as possible. At the same time the voltage of the sine wave is as high as possible which reduces the jitter going from sine wave to clock signal.

Fig. 9 Block diagram oscillator circuit

**SAA7708H**

#### 10.9.1 SUPPLY OF THE X-TAL OSCILLATOR

The power supply connections of the oscillator are separate from the other supply lines. This to minimize the feedback from the ground bounce of the chip to the oscillator circuit. The VSS\_OSC pin is used as ground supply and the VDD\_OSC as positive supply.

#### 10.10 The phase lock loop circuit to generate the DSP and other clocks

There are several reasons why two PLL circuits to generate the DSP clock and other clocks are used:

- PLL1 is used to deliver the clock to the DSP core. The deviding factor of this PLL can be changed with I2C bits PLL\_DIV(3,2,1,0) but should only be used in the default position to ensure maximum functionality.

- Crystals for the crystal oscillator in the range of twice the required DSP clock frequency, so approximately 45 MHz, are always third overtone crystals and must also be fabricated on customer demand. This makes these crystals expensive. The PLL2 enables the use of a crystal running in the fundamental mode and also a general available crystal can be chosen. For this circuit a 256 X 44.1 kHz = 11.2896 MHz crystal is chosen. The clock of this PLL2 is used via a sample rate converter for the AD decimation paths and stereo decoding, the SPDIF logic, the uProcessor interface and the Fader DAC upsample filters.

With the I<sup>2</sup>C bit dsp\_turbo (bit 11 of \$0FFD) the output frequency can be doubled for test purposes by switching this bit to 1, in functional mode only the default '0' position is allowed.

#### 10.11 The DSP core

For this chip a type of DSP core (the actual programmable embedded calculating machine) is used that is adapted to the required calculation power needed and as such is optimized on area. This DSP core is also known under the name EPICS6, of which EPICS is the generic name of this type of DSP and 6 is the version number. This DSP is mainly a calculator designed for real time processing of the digitized (at 38 or 44.1 kHz sample frequency) audio data stream. A DSP is especially suited to calculate the sum of products of the digital datawords representing the audio data.

#### 10.12 DSP core status register and the external control pins

In the DSP core there is a 9 bit long status register. These 9 flags contain information which is used by the conditional branch logic of the DSP core. For direct use with the external world 4 flags are defined, F0, F1, F2 and F3. For external control two input pins, DSP\_IN1 and DSP\_IN2, have been implemented. These pins control the status of the flags F0 and F1. The two status flags F3 and F4 are controlled by the DSP core and can be read via the output pins DSP\_OUT1 and DSP\_OUT2. The functions of each pin depends on the DSP program. Another important flag is the I-flag. This flag is an input flag and is set the moment new I<sup>2</sup>S data or another type of digital audio data is available to the DSP core.

#### 10.13 I<sup>2</sup>C control (SCL and SDA pin)

General description of the I<sup>2</sup>C format in a booklet can be obtained at Philips Semiconductors, International Marketing and Sales

For the external control of the CDSP chip a fast I<sup>2</sup>C bus is implemented. This is a 400 kHz bus which is downward compatible with the standard 100 kHz bus. There are three different types of control instructions:

- Instructions to control the DSP program, programming the coefficient RAM and reading the values of parameters.

(level, multipath etc.)

- Instructions controlling the DATA I<sup>2</sup>S flow, like source selection, IAC control and clock speed

The detailed description of the  $I^2C$  bus and the description of the different bits in the memory map is given in paragraph:  $I^2C$  Bus control and commands.

**SAA7708H**

#### 10.14 I2S and SPDIF inputs

#### 10.14.1 GENERAL DESCRIPTION I2S INPUTS

For communication with external digital sources a I<sup>2</sup>S digital interface bus can be used. It is a serial 3-line bus, having one line for data, one line for clock and one line for the word select. For external digital sources the SAA7708 acts as a slave, so the external source is master and supplies the clock.

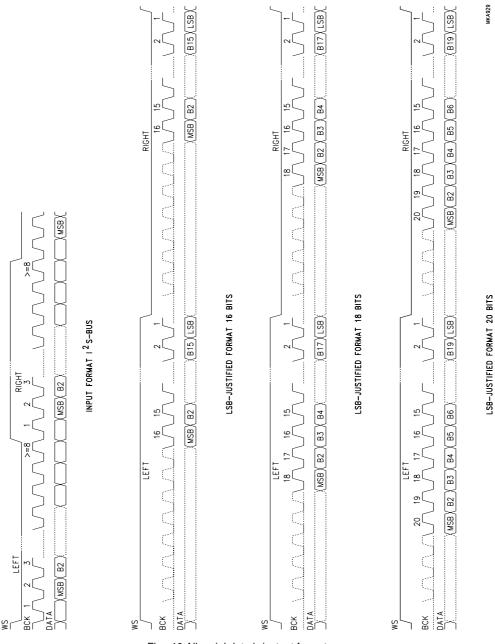

The digital audio input is capable of handling multiple input formats. For brevity the serial digital audio in- and outputs are called I2S. However this does not mean that the format is always the Philips I2S standard.

The I<sup>2</sup>S input is capable of handling Philips I<sup>2</sup>S, and LSB justified formats of 16, 18 and 20 bits word sizes, fs can vary from 32 kHz until 48 kHz.

See the I<sup>2</sup>C Memory Map for the bits that must be programmed, for selection of the desired I<sup>2</sup>S format.

See Fig. 10 for the general waveform formats of the four possible formats.

The number of bitclock (BCK) pulses may vary in the application. When the applied wordlength is smaller than 18 bits (internal resolution), the LSB bits will get internally a zero value.

When the applied wordlength exceeds 18 bits, the LSB's are skipped.

The input circuitry is limited in handling the number of BCK pulses per WS period. The maximum allowed number of bitclocks per WS period is 512.

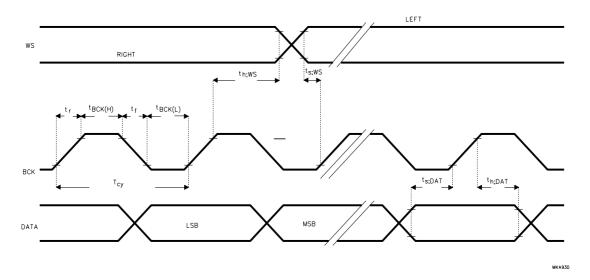

10.14.2 THE TIMING DIAGRAM OF THE COMMUNICATION IS SHOWN IN FIG. 11.

The DSP program is synchronised with the external source via the word select signal. On every negative edge of the IIS\_WS the I flag of the status register is set.

## SAA7708H

10.14.3 DIGITAL DATA STREAM FORMATS

Fig. 10 All serial data in/output formats

Philips Semiconductors

Fig. 11 Input timing digital audio data inputs

Table 4 Timing digital audio inputs/out (see Fig. 11)

| SYMBOL              | PARAMETER             | CONDITIONS             | MIN.                 | TYP. | MAX.                 | UNIT | NO   |

|---------------------|-----------------------|------------------------|----------------------|------|----------------------|------|------|

| t <sub>r</sub>      | rise time             | t <sub>cy</sub> =50 nS | -                    | -    | 0.15*t <sub>cy</sub> | ns   | 9.01 |

| t <sub>f</sub>      | fall time             | t <sub>cy</sub> =50 nS | -                    | -    | 0.15*t <sub>cy</sub> | ns   | 9.02 |

| t <sub>cy</sub>     | bitclock cycle time   |                        | 50                   | -    | -                    | ns   | 9.03 |

| t <sub>BCK(H)</sub> | bitclock time<br>HIGH | t <sub>cy</sub> =50 nS | 0.35*t <sub>cy</sub> | -    | -                    | ns   | 9.04 |

| t <sub>BCK(L)</sub> | bitclock time<br>LOW  | t <sub>cy</sub> =50 nS | 0.35*t <sub>cy</sub> | -    | -                    | ns   | 9.05 |

| t <sub>s;DAT</sub>  | data setup time       | t <sub>cy</sub> =50 nS | 0.2*t <sub>cy</sub>  | -    | -                    | ns   | 9.06 |

| t <sub>h;DAT</sub>  | data hold time        | t <sub>cy</sub> =50 nS | 0.2*t <sub>cy</sub>  |      |                      | ns   | 9.07 |

| t <sub>s;WS</sub>   | wordselect setup time | t <sub>cy</sub> =50 nS | 0.2*t <sub>cy</sub>  | -    | -                    | ns   | 9.1  |

| t <sub>h;WS</sub>   | wordselect hold time  | t <sub>cy</sub> =50 nS | 0.2*t <sub>cy</sub>  | -    | -                    | ns   | 9.11 |

**SAA7708H**

#### 10.14.4 GENERAL DESCRIPTION SPDIF INPUTS

For communication with external digital sources also a SPDIF input can be used. The two SPDIF input pins can be connected via an analog multiplexer to the SPDIF receiver. It is a receiver without an analogue PLL that samples the incoming SPDIF with a high frequency. In this way the data is recovered synchronously on the applied system clock. Also a 64\*Fs clock is regenerated out of the SPDIF datastream.

From the SPDIF signal a three wire (I2S like) serial bus is made, consisting of a Wordselect, Data and Bitclock line. The FS frequency depends solely on the SPDIF signal input accuracy.

This design does NOT handle the userdata-, channelstatus- and validitybits of the SPDIF stream, but only the audio is given at its outputs. The bits in the audio space are always decoded regardless of any statusbits e.g. 'copy protected', 'professional mode' or 'data mode'.

#### 10.14.4.1 SPDIF format

The SPDIF format used here carries the 2 channel PCM audio over a two wire pair.

The SPDIF format can be partitioned into two main layers, being the abstract model of frames and blocks, and the channel modulation. Currently there are three samples frequencies specified:

Table 5 Sample Frequencies

| SAMPLE FREQ [KHZ] | DATA-RATE [MBIT/S] | CHANNEL-RATE [MBIT/S] |

|-------------------|--------------------|-----------------------|

| 44.1              | 2.8224             | 5.6448                |

| 48.0              | 3.072              | 6.144                 |

| 32.0              | 2.048              | 4.096                 |

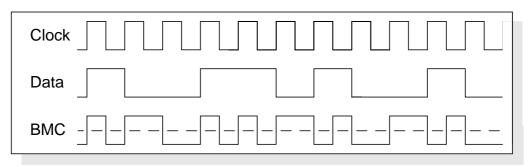

#### 10.14.4.2 SPDIF channel modulation

The digital signal is coded using "biphase-mark-code" (BMC), which is a kind of phase-modulation. In this scheme, a logic one in the data corresponds to two zero-crossings in the coded signal, and a logic zero to one zero-crossing

Fig. 12 BiPhase Mark Coding

The SPDIF interface of the SAA7708 is capable of decoding all standardized sampling frequencies with Level3 timing being the whole range of 28 kHz to 54 kHz sampling frequency. However the highest frequency posible is in fact due to the limited cycle budget of the DSP only 44.1 kHz.

**SAA7708H**

#### 10.14.4.3 Timing Characteristicse logic.

The SPDIF specification IEC 958, supports three levels of clock accuracy, being high-accuracy, normal accuracy and variable or pitch shifter clock mode.

- Level 1, high accuracy, tolerance of transmitting sampling frequency shall be within +50x10-6

- Level 2, normal accuracy, all receivers should receive a signal of +1000x10-6 of nominal sampling frequency

- Level 3, variable pitch shifted clock mode, adeviation of 12.5% of the nominal sampling frequency is possible

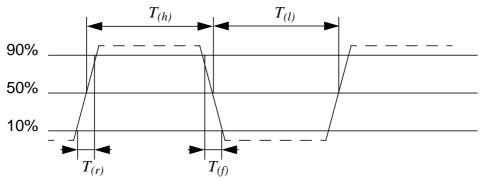

Rise and fall times are defined as:

Rise time =  $100 \times R(r) / (T(I)+T(h))\%$

Fall time =  $100 \times R(f) / (T(I)+T(h))\%$

Rise and fall times should be in the range:

0%-20%when the data bit is a "1"

0%-10%when the data bits are two succeeding

Fig. 13 Rise and fall times

Duty cycle shall be calculated using the equation:

Duty cycle =  $100 \times T(h) / (T(l)+T(h))\%$

Duty cycle shall be in the range:

40%-60% when the data bit is a logical "1"

45%-55% when the data bits are two succeeding "0"'s

#### 10.15 RDS decoder (RDS\_CLOCK / RDS\_DATA pins)

The RDS decoder recovers the additional inaudible RDS information which is transmitted by FM radio broadcasting. The (buffered) data is provided as output for further processing by a suitable decoder. The operational functions of the decoder are in accordance with the EBU specification EN 50067.

The RDS decoder has three different functions:

**SAA7708H**

- · Clock and data recovery from the MPX signal

- · Buffering of 16 bits if selected

- · Interfacing with the micro controller

#### 10.15.1 CLOCK AND DATA RECOVERY

The RDS-chain has a separate input FM\_RDS. This enables RDS updates during tape play.

The RDS chain contains a third order sigma-delta AD convertor, followed by two decimation filters. The first filter passes the multiplex band including the signals around 57 kHz and reduces the sigma- delta noise. The second filter reduces the RDS bandwidth around 57 kHz.

The quadrature mixer converts the RDS band to the frequency spectrum around 0 Hz and contains the appropriate Q/I signal filters. The final decoder recovers the clock and data signals. These signals are output on the RDS-Clock and Data pins.

#### 10.15.2 TIMING OF CLOCK AND DATA SIGNALS

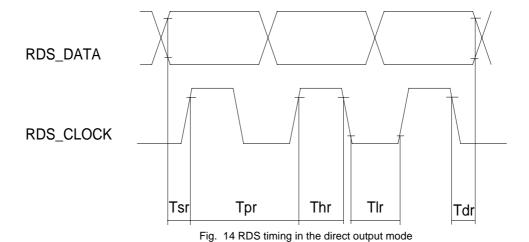

The timing of the Clock and Data output is derived from the incoming data signal. Under stable conditions the data will remain valid for  $400 \, \mu s$  after the clock transition. The timing of the data change is  $100 \, \mu s$  before a positive clock change. This timing is suited for positive as well as negative triggered interrupts on a microprocessor. The RDS timing is shown in Fig. 14.

During poor reception it is possible that faults in phase occur, then the duty cycle of the clock and data signals will vary from minimum 0.5 times to a maximum of 1.5 times the standard clock periods. Normally, faults in phase do not occur on a cyclic basis.

#### 10.15.3 BUFFERING OF RDS DATA

The repetition of the RDS data is around the 1187 Hz. This results in an interrupt on the microprocessor for every 842 uS. In a second mode, the RDS interface has a double 16 bit buffer.

**SAA7708H**

#### 10.15.4 BUFFER INTERFACE

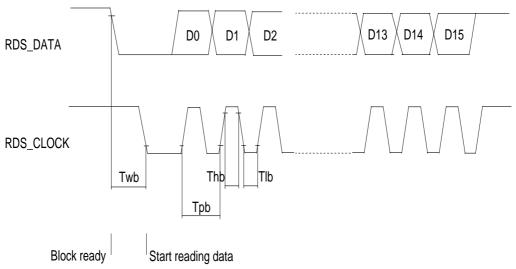

The RDS interface buffers 16 data bits. Every time 16 bits are received, the data line in pulled down and the buffer is overwritten. The control microprocessor has to monitor the data line in at most every 13.5 msec. This mode is selected by setting the rds\_clkin I<sup>2</sup>C bit of the IIC\_RDS\_ConTrol register (\$0FF3) (see Table 29) to "1". In Fig. 15 the interface signals from the RDS decoder and the microcomputer in buffer mode are shown. When the buffer is filled with 16 bit the data line is pulled down. The data line will remain low until reading of the buffer is started by pulling down the clock line. The first bit is clocked out. After 16 clock pulses the reading of the buffer is ready and the data line is set high until the buffer is filled again. The microprocessor stops communication by pulling the line high. The data is written out just after the clock high-low transition. The data is valid when the clock is high.

When a new 16 bit buffer is filled before the other buffer is read, that buffer will be overwritten and the old data is lost.

Fig. 15 Interface signals RDS decoder and microcomputer

#### 10.16 DSP Reset