©1995 National Semiconductor Corporation TL/H/7146

RRD-B30M115/Printed in U. S. A.

| f Military/Aerospace specified devi<br>olease contact the National Sem<br>Office/Distributors for availability an                                                                                                                        | Package Dissipation (Note 1)<br>Storage Temperature<br>Operating Temperature |                        | 1.39W<br>−65°C to +150°C<br>0°C to +70°C |                         |                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------|------------------------------------------|-------------------------|---------------------|

| Supply Voltage<br>LM391N-100                                                                                                                                                                                                             | Lead Temp. (Solo                                                             | dering, 10 sec.)       |                                          | 260°C                   |                     |

| LM391N-100         ± 50V or + 100V           Input Voltage         Supply Voltage less 5V                                                                                                                                                |                                                                              | Thermal Resistar       | nce                                      |                         |                     |

| Shutdown Current (Pin 14)                                                                                                                                                                                                                | 1 mA                                                                         | $	heta_{JC}$           |                                          |                         | 20°C/W<br>63°C/W    |

| Electrical Characteristic                                                                                                                                                                                                                | <b>S</b> $T_A = 25^{\circ}C$ (The follow                                     | wing are for $V^+ = 9$ | 0% V $^+$ <sub>MAX</sub> and V           | ′− = 90% V <sup>−</sup> | - <sub>MAX</sub> .) |

| Parameter                                                                                                                                                                                                                                | Conditions                                                                   | Min                    | Тур                                      | Мах                     | Units               |

| Quiescent Current<br>LM391N-100                                                                                                                                                                                                          | Current in Pin 15<br>$V_{IN} = 0$                                            |                        | 5                                        | 6                       | mA                  |

| Output Swing                                                                                                                                                                                                                             | Positive<br>Negative                                                         | $V^+ - 7 V^- + 7$      | $V^{+} - 5 V^{-} + 5$                    |                         | V<br>V              |

| Drive Current                                                                                                                                                                                                                            | Source (Pin 8)<br>Sink (Pin 5)                                               | 5<br>5                 |                                          |                         | mA<br>mA            |

| Noise (20 Hz–20 kHz)                                                                                                                                                                                                                     | Input Referred                                                               |                        | 3                                        |                         | μV                  |

| Supply Rejection                                                                                                                                                                                                                         | Input Referred                                                               | 70                     | 90                                       |                         | dB                  |

| Total Harmonic Distortion                                                                                                                                                                                                                | f = 1  kHz<br>f = 20  kHz                                                    |                        | 0.01<br>0.10                             | 0.25                    | %<br>%              |

| Intermodulation Distortion                                                                                                                                                                                                               | 60 Hz, 7 kHz, 4:1                                                            |                        | 0.01                                     |                         | %                   |

| Open Loop Gain                                                                                                                                                                                                                           | f = 1 kHz                                                                    | 1000                   | 5500                                     |                         | V/V                 |

| Input Bias Current                                                                                                                                                                                                                       |                                                                              |                        | 0.1                                      | 1.0                     | μΑ                  |

| Input Offset Voltage                                                                                                                                                                                                                     |                                                                              |                        | 5                                        | 20                      | mV                  |

| Positive Current Limit V <sub>BE</sub>                                                                                                                                                                                                   | Pin 10–9                                                                     |                        | 650                                      |                         | mV                  |

| Negative Current Limit V <sub>BE</sub>                                                                                                                                                                                                   | Pin 9–13                                                                     |                        | 650                                      |                         | mV                  |

| Positive Current Limit Bias Current                                                                                                                                                                                                      | Pin 10                                                                       |                        | 10                                       | 100                     | μΑ                  |

| Negative Current Limit Bias Current                                                                                                                                                                                                      | Pin 13                                                                       |                        | 10                                       | 100                     | μΑ                  |

| Minimum pin 14 current required for<br>Maximum pin 14 current for amplifier<br>The typical shutdown switch point cu<br>lote 1: For operation in ambient temperatures abo<br>f 90°C/W junction to ambient.<br><b>Typical Applications</b> | not shut down is 0.05 m<br>rrent is 0.2 mA.                                  | Α.                     |                                          | erature and a the       | mal resistanc       |

| , ) From , i FF nom on o                                                                                                                                                                                                                 | v* <b>o</b>                                                                  | Reb                    |                                          |                         |                     |

| <b></b>                                                                                                                                                                                                                                  |                                                                              |                        |                                          |                         |                     |

|                                                                                                                                                                                                                                          |                                                                              |                        |                                          | ]                       |                     |

| Component                        | Typical Value | Comments                                                                                                                                                                                                                                   |

|----------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>IN</sub>                  | 1 μF          | Input coupling capacitor sets a low frequency pole with R <sub>IN</sub> .                                                                                                                                                                  |

|                                  |               | $f_{L} = \frac{1}{2\pi R_{IN}C_{IN}}$                                                                                                                                                                                                      |

| R <sub>IN</sub>                  | 100k          | Sets input impedance and DC bias to input.                                                                                                                                                                                                 |

| R <sub>f2</sub>                  | 100k          | Feedback resistor; for minimum offset voltage at the output this should be equal to $R_{IN}$ .                                                                                                                                             |

| R <sub>f1</sub>                  | 5.1k          | Feedback resistor that works with $R_{f_2}$ to set the voltage gain. $A_V = 1 + \frac{R_{f_2}}{R_{f_1}}$                                                                                                                                   |

| Cf                               | 10 µF         | Feedback capacitor. This reduces the gain to unity at DC for minimum offset voltage at the output. Also sets a low frequency pole with $R_{f_1}$ .<br>$f_L = \frac{1}{2\pi R_{f_1}C_f}$                                                    |

| C <sub>C</sub>                   | 5 pF          | $            Compensation capacitor. Sets gain bandwidth product and a high frequency pole. \\             GBW = \frac{1}{2\pi 5000C_C}, \ f_h = \frac{GBW}{A_V} \\             Max \ f_h \ for \ stable \ design \ \approx \ 500 \ kHz. $ |

| R <sub>A</sub>                   | 3.9k          | AB bias resistor.                                                                                                                                                                                                                          |

| R <sub>B</sub>                   | 10k           | AB bias potentiometer. Adjust to set bias current in the output stage.                                                                                                                                                                     |

| C <sub>AB</sub>                  | 0.1 μF        | Bypass capacitor for bias. This improves high frequency distortion and transient response.                                                                                                                                                 |

| C <sub>R</sub>                   | 5 pF          | Ripple capacitor. This improves negative supply rejection at midband and high frequencies. $C_{\rm R},$ if used, must equal $C_{\rm C}.$                                                                                                   |

| R <sub>eb</sub>                  | 100Ω          | Bleed resistor. This removes stored charge in output transistors.                                                                                                                                                                          |

| R <sub>O</sub>                   | 2.7Ω          | Output compensation resistor. This resistor and $C_O$ compensate the output stage. This valu will vary slightly for different output devices.                                                                                              |

| CO                               | 0.1 μF        | Output compensation capacitor. This works with ${\sf R}_O$ to form a zero that cancels ${\sf f}_\beta$ of the output power transistors.                                                                                                    |

| R <sub>E</sub>                   | 0.3Ω          | Emitter degeneration resistor. This resistor gives thermal stability to the output stage<br>quiescent current. IRC PW5 type.                                                                                                               |

| R <sub>TH</sub>                  | 39k           | Shutdown resistor. Sets the amount of current pulled out of pin 14 during shutdown.                                                                                                                                                        |

| C <sub>2</sub> , C′ <sub>2</sub> | 1000 pF       | Compensation capacitors for protection circuitry.                                                                                                                                                                                          |

| XL                               | 10Ω∥5 μH      | Used to isolate capacitive loads, usually 20 turns of wire wrapped around a 10 $\Omega$ , 2W resisted                                                                                                                                      |

# **Application Hints**

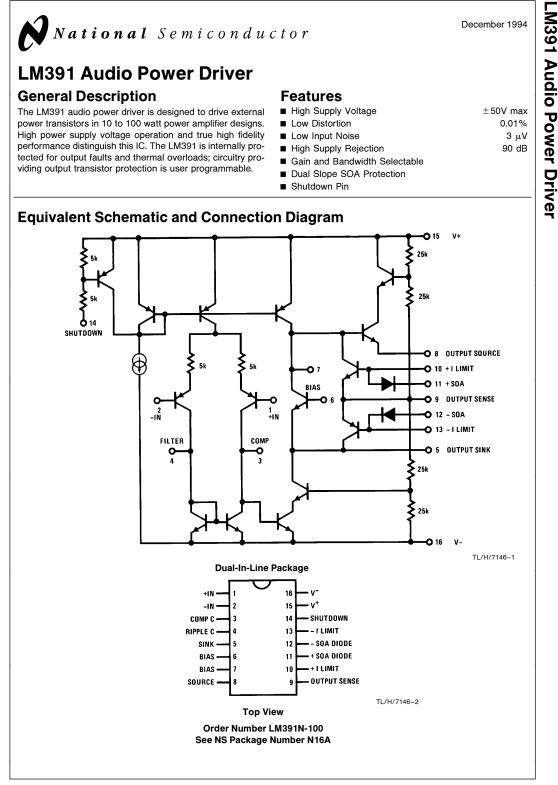

GENERALIZED AUDIO POWER AMP DESIGN

Givens: Power Output

- Load Impedance

- Input Sensitivity

- Input Impedance

- Bandwidth

The power output and load impedance determine the power supply requirements. Output signal swing and current are found from:

$$V_{\text{Opeak}} = \sqrt{2 R_{\text{L}} P_{\text{O}}} \tag{1}$$

$$I_{\text{Opeak}} = \sqrt{\frac{2 P_{\text{O}}}{R_{\text{L}}}}$$

(2)

Add 5 volts to the peak output swing (V<sub>OP</sub>) for transistor voltage to get the supplies, i.e.,  $\pm$  (V<sub>OP</sub> + 5V) at a current of I<sub>peak</sub>. The regulation of the supply determines the unloaded voltage, usually about 15% higher. Supply voltage will also rise 10% during high line conditions.

max supplies  $\approx \pm (V_{Opeak} + 5) (1 + regulation) (1.1)$  (3) The input sensitivity and output power specs determine the required gain.

$$A_{V} \ge \frac{\sqrt{P_{O} R_{L}}}{V_{IN}} = \frac{V_{ORMS}}{V_{INRMS}}$$

(4)

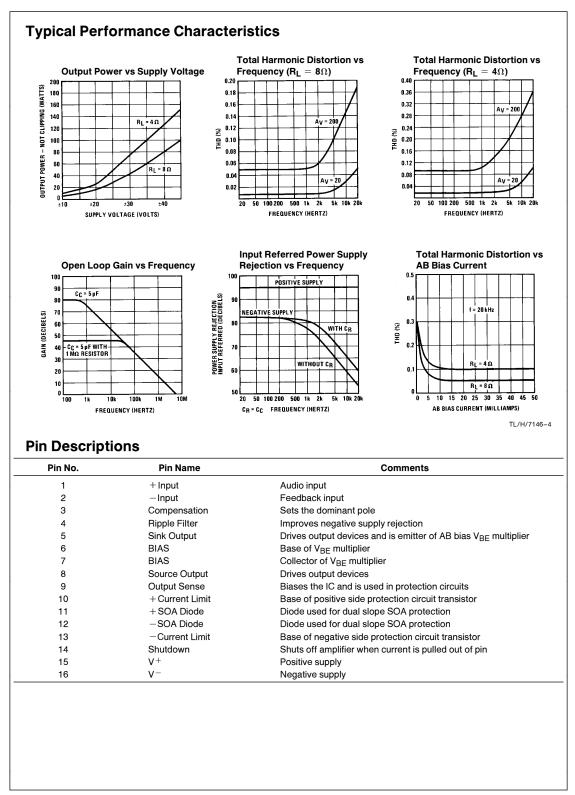

Normally the gain is set between 20 and 200; for a 25 watt, 8 ohm amplifier this results in a sensitivity of 710 mV and 71 mV, respectively. The higher the gain, the higher the THD, as can be seen from the characteristics curves. Higher gain also results in more hum and noise at the output.

The desired input impedance is set by  ${\sf R}_{IN}.$  Very high values can cause board layout problems and DC offsets at the output. The bandwidth requirements determine the size of C<sub>f</sub> and C<sub>C</sub> as indicated in the external component listing.

The output transistors and drivers must have a breakdown voltage greater than the voltage determined by equation (3). The current gain of the drive and output device must be high enough to supply  $I_{Opeak}$  with 5 mA of drive from the LM391. The power transistors must be able to dissipate approximately 40% of the maximum output power; the drivers must dissipate this amount divided by the current gain of the outputs. See the output transistor selection guide, Table A.

To prevent thermal runaway of the AB bias current the following equation must be valid:

$$\theta_{JA} \leq \frac{\mathsf{R}_{\mathsf{E}} \left(\beta_{\mathsf{MIN}} + 1\right)}{\mathsf{V}_{\mathsf{CEQMAX}} \left(\mathsf{K}\right)}$$

(5)

where:

where:

$\theta_{JA}$  is the thermal resistance of the driver transistor, junction to ambient, in °C/W.

$\mathsf{R}_\mathsf{E}$  is the emitter degeneration resistance in ohms.

$\beta_{\min}$  is that of the output transistor.

$V_{\mbox{CEQMAX}}$  is the highest possible value of one supply from equation (3).

K is the temperature coefficient of the driver base-emitter voltage, typically 2 mV/°C.

Often the value of  $R_E$  is to be determined and equation (5) is rearranged to be:

$$R_{E} \ge \frac{\theta_{JA} \left( V_{CEQMAX} \right) K}{\beta_{MIN} + 1}$$

(6)

The maximum average power dissipation in each output transistor is:

$$\overline{P_{DMAX}} = 0.4 P_{OMAX} \tag{7}$$

The power dissipation in the driver transistor is:

$$\overline{P_{\text{DRIVER(MAX)}}} = \frac{\overline{P_{\text{DMAX}}}}{\beta_{\text{MIN}}}$$

(8)

Heat sink requirements are found using the following formulas:

$$\theta_{JA} \le \frac{T_{JMAX} - T_{AMAX}}{P_D}$$

(9)

$$\theta_{SA} \le \theta_{JA} - \theta_{JC} - \theta_{CS}$$

(10)

$heta_{\mathsf{SA}} \leq heta_{\mathsf{JA}} - heta_{\mathsf{JC}} - heta_{\mathsf{CS}}$

$T_{\mbox{jMAX}}$  is the maximum transistor junction temperature.

$T_{\mbox{\scriptsize AMAX}}$  is the maximum ambient temperature.

$\theta_{\rm JA}$  is thermal resistance junction to ambient.

$\theta_{SA}$  is thermal resistance sink to ambient.

$\theta_{\rm JC}$  is thermal resistance junction to case.

$\theta_{CS}$  is thermal resistance case to sink, typically 1°C/W for most mountings.

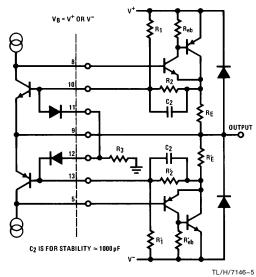

# Application Hints (Continued) PROTECTION CIRCUITRY

The protection circuits of the LM391 are very flexible and should be tailored to the output transistor's safe operating area. The protection V-I characteristics, circuitry, and resistor formulas are described below. The diodes from the output to each supply prevent the output voltage from exceeding the supplies and harming the output transistors. The output will do this if the protection circuitry is activated while driving an inductive load.

### TURN-ON DELAY

It is often desirable to delay the turn-ON of the power amplifier. This is easily implemented by putting a resistor in series with a capacitor from pin 14 to ground. The value of the

### **Protection Circuitry with External Components**

resistor is set to limit the current to less than 1 mA (the absolute maximum). This resistor with the capacitor gives a time constant of RC. The turn-ON delay is approximately 2 time constants.

Example:

Amplifier with maximum supply of 30V, like the 20W,  $8\Omega$  example in the data sheet, requiring a delay of 1 second. Time delay = 2 RC

$$R = \frac{Max V^+}{1 mA}$$

So:

R = 30k. Solving for C gives 16.7  $\mu F.$  Use C = 20  $\mu F$  with a 30V rating.

### Protection Characteristics

## Protection Circuit Resistor Formulas ( $V_B = V^+$ )

| Type of Protection                            | R <sub>E</sub> , R'          | R <sub>1</sub> , R′ <sub>1</sub>                | R <sub>2</sub> , R' <sub>2</sub> | R <sub>3</sub> , R′ <sub>3</sub>                          |

|-----------------------------------------------|------------------------------|-------------------------------------------------|----------------------------------|-----------------------------------------------------------|

| Current Limit                                 | $R_{E} = \frac{\phi}{I_{L}}$ | Not Required                                    | Short                            | Not Required                                              |

| Single Slope SOA<br>Protection                | $R_{E} = \frac{\phi}{I_{L}}$ | $R_1 = R_2\left(\frac{V_M - \phi}{\phi}\right)$ | 1 kΩ                             | Not Required                                              |

| Dual Slope SOA<br>Protection<br>$(V_B = V^+)$ | $R_{E} = \frac{\phi}{I_{L}}$ | $R_1 = R_2\left(\frac{V_M - \phi}{\phi}\right)$ | 1 kΩ                             | $R_3 = R_2 \left[ \frac{V^+}{I_L R_E - \phi} - 1 \right]$ |

Note:  $\phi$  is the current limit V<sub>BE</sub> voltage, 650 mV. Assumptions: V<sup>+</sup> >>  $\phi$ , V<sub>M</sub> >>  $\phi$ . V<sup>+</sup> is the load supply voltage. V<sub>M</sub> is the maximum rated V<sub>CE</sub> of the output transistors.

# Application Hints (Continued)

# TRANSIENT INTERMODULATION DISTORTION

There has been a lot of interest in recent years about transient intermodulation distortion. Matti Otala of University of Oulu, Oulu, Finland has published several papers on the subject. The results of these investigations show that the open loop pole of the power amplifier should be above 20 kHz.

To do this with the LM391 is easy. Put a 1 M $\Omega$  resistor from pin 3 to the output and the open loop gain is reduced to about 46 dB. Now the open loop pole is at 30 kHz. The current in this resistor causes an offset in the input stage that can be cancelled with a resistor from pin 4 to ground. The resistor from pin 4 to ground should be 910 k $\Omega$  rather than 1 M $\Omega$  to insure that the shutdown circuitry will operate correctly. The slight difference in resistors results in about 15 mV of offset. The 40W, 8 $\Omega$  amplifier schematic shows the hookup of these two resistors.

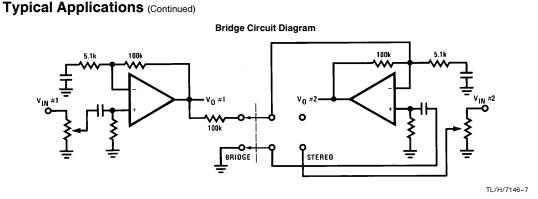

### **BRIDGE AMPLIFIER**

A switch can be added to convert a stereo amplifer to a single bridge amplifer. The diagram below shows where the switch and one resistor are added. When operating in the bridge mode the output load is connected between the two outputs, the input is V<sub>IN</sub> #1, and V<sub>IN</sub> #2 is disconnected.

# **OSCILLATIONS & GROUNDING**

Most power amplifiers work the first time they are turned on. They also tend to oscillate and have excess THD. Most oscillation problems are due to inadequate supply bypassing and/or ground loops. A 10  $\mu$ F, 50V electrolytic on each power supply will stop supply-related oscillations. However, if the signal ground is used for these bypass caps the THD is usually excessive. The signal ground must return to the power supply alone, as must the output load ground. All other grounds—bypass, output R-C, protection, etc., can tie together and then return to supply. This ground is called high frequency ground. On the 40W amplifier schematic all the grounds are labeled.

Capacitive loads can cause instabilities, so they are isolated from the amplifier with an inductor and resistor in the output lead.

### **AB BIAS CURRENT**

To reduce distortion in the output stage, all the transistors are biased ON slightly. This results in class AB operation and reduces the crossover (notch) distortion of the class B stage to a low level, (see performance curve, THD vs AB bias). The potentiometer, R<sub>B</sub>, from pins 6–7 is adjusted to give about 25 mA of current in the output stage. This current is usually monitored at the supply or by measuring the voltage across R<sub>E</sub>.

# **Output Transistors Selection Guide**

| Power<br>Output F | Driver Tr | ransistor | Output Transistor |        |

|-------------------|-----------|-----------|-------------------|--------|

|                   | PNP       | NPN       | PNP               | NPN    |

| 20W @ 8Ω          | MJE711    | MJE721    | TIP42A            | TIP41A |

| 30W @ 4Ω          | MJE171    | MJE181    | 2N6490            | 2N6487 |

|                   | D43C8     | D42C8     |                   |        |

| 40W @ 8Ω          | MJE712    | MJE722    | 2N5882            | 2N5880 |

| 60W @ 4Ω          | MJE172    | MJE182    |                   |        |

|                   | D43C11    | D42C11    |                   |        |

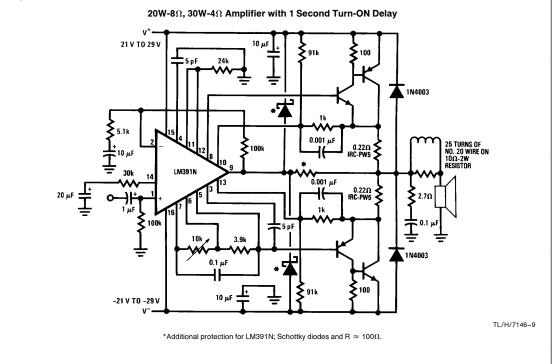

### Application Hints (Continued) A 20W, 80: 30W, 40, AMPLIFIER

| A 20W, | 812; | 30 99, | 452 | AWF | LIFIER |  |

|--------|------|--------|-----|-----|--------|--|

| ~      |      |        |     |     |        |  |

Givens:

| Power Outp        | ut                 | 20W into $8\Omega$         |

|-------------------|--------------------|----------------------------|

|                   |                    | 30W into $4\Omega$         |

| Input Sensitivity |                    | 1V Max                     |

| Input Imped       | ance               | 100k                       |

| Bandwidth         |                    | 20 Hz–20 kHz $\pm$ 0.25 dB |

| Equations (1)     | and (2) give:      |                            |

| 20W/8Ω            | $V_{OP} = 17.9V$   | $I_{OP} = 2.24A$           |

| $30W/4\Omega$     | $V_{OP} = 15.5V$   | $I_{OP} = 3.87A$           |

| Therefore the     | supply required is | :                          |

|                   |                    |                            |

$\pm\,23V$  @ 2.24A, reducing to . . .

$\pm\,21V$  @ 3.87A

With 15% regulation and high line we get  $\pm 29V$  from equation (3).

Sensitivity and equation (4) set minimum gain:

$$A_V \ge \frac{\sqrt{20 \times 8}}{1} = 12.65$$

We will use a gain of 20 with resulting sensitivity of 632 mV. Letting  $R_{\rm IN}$  equal 100k gives the required input impedance. For low DC offsets at the output we let  $R_{\rm f_2}$  = 100k. Solving for  $R_{\rm f_1}$  gives:

$$\begin{aligned} R_{f_2} &= 100k\\ R_{f_1} &= \frac{100k}{20-1} = 5.26k; \text{use } 5.1k \end{aligned}$$

The bandwidth requirement must be stated as a pole, i.e., the 3 dB frequency. Five times away from a pole gives 0.17 dB down, which is better than the required 0.25 dB. Therefore:

$$f_L = \frac{20}{5} = 4 \text{ Hz}$$

$$f_h = 20k \times 5 = 100 \text{ kHz}$$

Solving for C<sub>f</sub>:

$$C_{f} \ge \frac{1}{2\pi R_{f_{1}}f_{L}} = 7.8 \ \mu F; use 10 \ \mu F$$

The recommended value for C\_C is 5 pF for gains of 20 or larger. This gives a gain-bandwidth product of 6.4 MHz and a resulting bandwidth of 320 kHz, better than required.

The breakdown voltage requirement is set by the maximum supply; we need a minimum of 58V and will use 60V. We must now select a 60V power transistor with reasonable beta at  $|_{Opeak}$ , 3.87A. The TIP42, TIP41 complementary pair are 60V, 60W transistors with a minimum beta of 30 at 4A. The driver transistor must supply the base drive given 5 mA drive from the LM391. The MJE711, MJE721 complementary driver transistors are 60V devices with a minimum beta of 40 at 200 mA. The driver transistors to insure that the R-C on the output will prevent instability.

To find the heat sink required for each output transistor we use equations (7), (9), and (10):

$$\overline{P_D} = 0.4 (30) = 12W$$

(7)

$$\theta_{JA} \le \frac{150^{\circ}C - 55^{\circ}C}{12} = 7.9^{\circ}C/W \text{ for } T_{AMAX} = 55^{\circ}C$$

(9)

$$\theta_{SA} \le 7.9 - 2.1 - 1.0 = 4.8^{\circ}C/W$$

(10)

If both transistors are mounted on one heat sink the thermal resistance should be halved to 2.4  $^\circ C/W.$

The maximum average power dissipation in each driver is found using equation (8):

$$\overline{P}_{DRIVER(MAX)} = \frac{12}{30} = 400 \text{ mW}$$

Using equation (9):

$$\theta_{\rm JA} \le \frac{155 - 55}{0.4} = 237^{\circ} {\rm C/W}$$

# Application Hints (Continued)

Since the free air thermal resistance of the MJE711, MJE721 is 100°C/W, no heat sink is required. Using this information and equation (6) we can find the minimum value of R<sub>E</sub> required to prevent thermal runaway.

$$\mathsf{R}_{\mathsf{E}} \geq \frac{100~(30)~(0.002)}{30~+~1} = ~0.19 \Omega \tag{6}$$

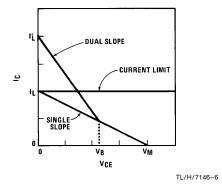

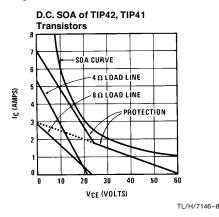

We must now use the SOA data on the TIP42, TIP41 transistors to set up the protection circuit. Below is the SOA curve with the  $4\Omega$  and  $8\Omega$  load lines. Also shown are the desired protection lines. Note the value of V<sub>B</sub> is equal to the supply voltage, so we use the formulas in the table.

The data points from the curve are:

$V_M = 60V, \; V_B = 23V, \; I_L = 3A, \; I_L^{'} = 7A$  Using the dual slope protection formulas:

$$R_{E} = \frac{0.65}{3} = 0.22\Omega$$

$$R_{2} = 1k$$

$$R_{1} = 1k \left(\frac{60 - 0.65}{0.65}\right) \approx 91k$$

$$R_{3} = 1k \left(\frac{23}{7(0.22) - 0.65} - 1\right) \approx 24k$$

Note that an R<sub>E</sub> of 0.22 $\Omega$  satisfies equation (6). The final schematic of this amplifier is below. If the output is shorted the current will be 1.8A and V<sub>CE</sub> is 23V. Since the input is AC, the average power is:

short

$$\overline{P_D} = \frac{1}{2}(1.8)$$

(23)  $\approx 21W$

This power is greater than was used in the heat sink calculations, so the transistors will overheat for long-duration shorts unless a larger heat sink is used.

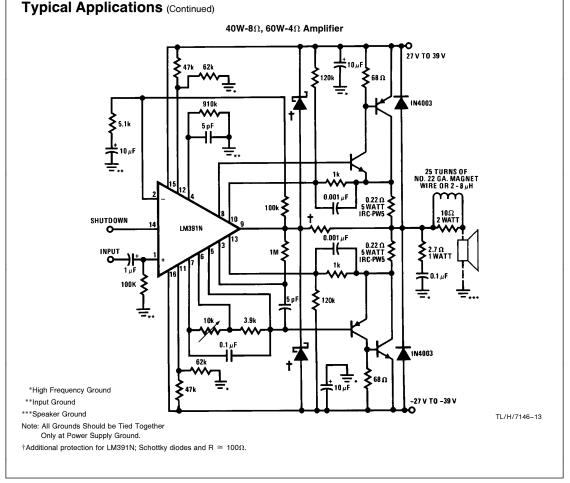

## Application Hints (Continued) Δ 40W/8Ω. 60W/4Ω AMPLIFIER

| A 40W/012,         | 00 44 / 432 | FIEF |

|--------------------|-------------|------|

| Given <sup>.</sup> |             |      |

| Given.                                                                   |                            |  |  |  |

|--------------------------------------------------------------------------|----------------------------|--|--|--|

| Power Output                                                             | 40W/8Ω                     |  |  |  |

|                                                                          | 60W/4Ω                     |  |  |  |

| Input Sensitivity                                                        | 1V Max                     |  |  |  |

| Input Impedance                                                          | 100k                       |  |  |  |

| Bandwidth                                                                | 20 Hz–20 kHz $\pm$ 0.25 dB |  |  |  |

| Equations (1) and (2) give:                                              |                            |  |  |  |

| $40W/8\Omega$ V <sub>OPeak</sub> = 25.3V                                 | I <sub>OPeak</sub> = 3.16A |  |  |  |

| $60W/4\Omega$ V <sub>OPeak</sub> = 21.9V                                 | $I_{OPeak} = 5.48A$        |  |  |  |

| Therefore the supply required is:                                        |                            |  |  |  |

| $\pm30.3V$ @ 3.16A, reducing to                                          |                            |  |  |  |

| ±26.9V @ 5.48A                                                           |                            |  |  |  |

| With 15% regulation and high line we get $\pm$ 38.3V using equation (3). |                            |  |  |  |

| The minimum gain from equation (4) is:                                   |                            |  |  |  |

| $A_{12} > 12$                                                            | 8                          |  |  |  |

$A_V \ge 18$

We select a gain of 20; resulting sensitivity is 900 mV. The input impedance and bandwidth are the same as the 20 watt amplifier so the components are the same.

$$R_{f_1} = 5.1k$$

$R_{IN} = 100k$   $C_C = 5 pF$

$R_{f_2} = 100k$   $C_f = 10 \mu F$

The maximum supplies dictate using 80V devices. The 2N5882, 2N5880 pair are 80V, 160W transistors with a minimum beta of 40 at 2A and 20 at 6A. This corresponds to a minimum beta of 22.5 at 5.5A (I<sub>Opeak</sub>). The MJE712, MJE722 driver pair are 80V transistors with a minimum beta of 50 at 250 mA. This output combination guarantees IOpeak with 5 mA from the LM391.

Output transistor heat sink requirements are found using equations (7), (9), and (10):

$$\overline{P_D} = 0.4 (60) = 24W$$

(7)

$$\theta_{\text{JA}} \le \frac{200 - 55}{24} = 6.0^{\circ}\text{C/W} \text{ for } \text{T}_{\text{AMAX}} = 55^{\circ}\text{C}$$

(9)

$\theta_{\text{SA}} \le 6.0 - 1.1 - 1.0 = 3.9^{\circ}\text{C/W}$  (10)

$\theta_{SA} \le 6.0 - 1.1 - 1.0 = 3.9^{\circ}C/W$

For both output transistors on one heat sink the thermal resistance should be 1.9°C/W.

Now using equation (8) we find the power dissipation in the driver:

$$\overline{P_{\text{DRIVER}}} = \frac{24}{20} = 1.2W$$

(8)

$$\theta_{\rm JA} \le \frac{150 - 55}{1.2} = 79^{\circ} {\rm C/W}$$

(9)

Since a heat sink is required on the driver, we should investigate the output stage thermal stability at the same time to optimize the design. If we find a value of  $\mathsf{R}_\mathsf{E}$  that is good for the protection circuitry, we can then use equation (5) to find the heat sink required for the drivers.

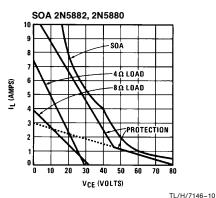

The SOA characteristics of the 2N5882, 2N5880 transistors are shown in the following curve along with a desired protection line.

The desired data points are:

$V_{M}=80V \quad V_{B}=47V \quad I_{L}=3A \quad I_{L}^{'}=11A$

Since the break voltage is not equal to the supply, we will use two resistors to replace  $\mathsf{R}_3$  and move  $\mathsf{V}_B.$

> Circuit Used TL/H/7146-11 Thevenin Equivalent Where: R<sub>TH</sub> = R<sub>3</sub><sup>A</sup> || R<sub>3</sub><sup>B</sup> Vτι  $\frac{R_3^A}{R_3^A + R_3^E}$ RTH  $V_{TH} = V^{-1}$ TL/H/7146-12

# Application Hints (Continued)

The formulas for R<sub>E</sub>, R<sub>1</sub>, and R<sub>2</sub> do not change:

$$R_{\sf E} = \frac{0.65}{3{\sf A}} = 0.22\Omega$$

80 - 0.65

$$R_2 = 1k$$

$R_1 = 1k \frac{60 - 0.03}{0.65} = 120k$

The formula for  $\mathsf{R}_3$  now gives  $\mathsf{R}_{TH}$  when the  $\mathsf{V}^+$  in the formula becomes  $\mathsf{V}_B.$

$$R_{TH} = R_2 \left[ \frac{V_B}{I_L R_E - \phi} - 1 \right]$$

$$= 1k \left[ \frac{47}{11 (0.22) - 0.65} - 1 \right] = 25.55k$$

$V_{TH}$  is the additional voltage added to the supply voltage to get  $V_{B}.$

$V_{TH}=-(V_B-V^+)=-(47-30)=-17V$ Now we must find  $R_3^A$  and  $R_3^B$  using the Thevenin formulas. Putting  $V_{TH},\,V^-,\,$  and  $R_{TH}$  into the appropriate formulas reduces to:

$$R_3^B = 0.76 R_3^A$$

and  $25.55k = R_3^A || R_3^B$

The easiest way to solve these equations is to iterate with standard values. If we guess  $\mathsf{R}_3^{\mathsf{A}}=62\mathsf{k},$  then  $\mathsf{R}_3^{\mathsf{B}}=47.12\mathsf{k};$  use 47k. The Thevenin impedance comes out 26.7k, which is close enough to 25.55k.

Now we will use equation (5) to determine the heat sinking requirements of the drivers to insure thermal stability:

$$\theta_{\rm JA} \le \frac{0.22 (20 + 1)}{40 (0.002)} \approx 57^{\circ} {\rm C/W}$$

(5)

This value is lower than we got with equation (9), so we will use it in equation (10):

$$\theta_{SA} \le 57 - 6 - 1 = 50^{\circ}C/W$$

(10)

This is the required heat sink for each driver. For low TIM we add the 1 M $\Omega$  resistor from pin 3 to the output and a 910k resistor from pin 4 to ground. The complete schematic is shown below.

If the output is shorted, the transistor voltage is about 28V and the current is 5A. Therefore the average power is:

short

$$\overline{PD} = \frac{1}{2}(28) 5 = 70W$$

This is much larger than the power used to calculate the heat sinks and the output transistors will overheat if the output is shorted too long.

# LM391 Audio Power Driver

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications