**OKI** Semiconductor

# MSM6660-01,02,03

# 1/2, 1/3 DUTY LCD DRIVER WITH 3-DOT COMMON DRIVER AND 62-DOT SEGMENT DRIVER

# **GENERAL DESCRIPTION**

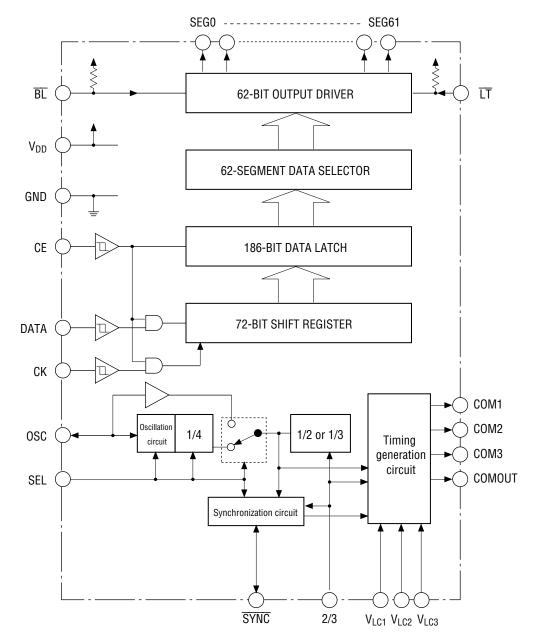

The MSM6660 is a dynamic display LCD driver, equipped with a function that can switch between 1/2 and 1/3 duty. The MSM6660 can directly drive LCDs with up to 124 or 186 segments, depending on whether 1/2 or 1/3 duty is selected.

The MSM6660's on-board display synchronization circuit allows display in a multi-chip configuration.

# FEATURES

- Power supply voltage : 4 to 6 V (for both logic and LCD driver)

- Operating temperature : -40°C to +85°C

- Applicable LCD duty : 1/2 (1/2 bias), 1/3 (1/3 bias)

- Common output : 2 (1/2 duty), 3 (1/3 duty)

- Segment output : 62

- Serial transfer clock rate : 2 MHz Maximum

- On-board display synchronization circuit which enables display in a multi-chip configuration.

- CE, DATA, and CK are provided for microcomputer interface.

- Handling of display data segments in three blocks enables efficient data transfer.

- Equipped with display-blanking input and display segment test input functions.

- A built-in voltage dividing resistor for bias voltage generation.

- 01: No internal resistance

- 02: 1 k $\Omega$  internal resistance

- 03: 30 k $\Omega$  internal resistance

- A built-in RC oscillation circuit which uses an external RC.

- Package options:

| 80-pin plastic QFP (QFP80-P-1420-0.80-K) | (Product name: MSM6660-01GS-K)     |

|------------------------------------------|------------------------------------|

|                                          | (Product name: MSM6660-02GS-K)     |

|                                          | (Product name: MSM6660-03GS-K)     |

| 80-pin plastic QFP (QFP80-P-1420-0.80-Bl | K) (Product name: MSM6660-01GS-BK) |

|                                          | (Product name: MSM6660-02GS-BK)    |

|                                          | (Product name: MSM6660-03GS-BK)    |

|                                          |                                    |

# **BLOCK DIAGRAM**

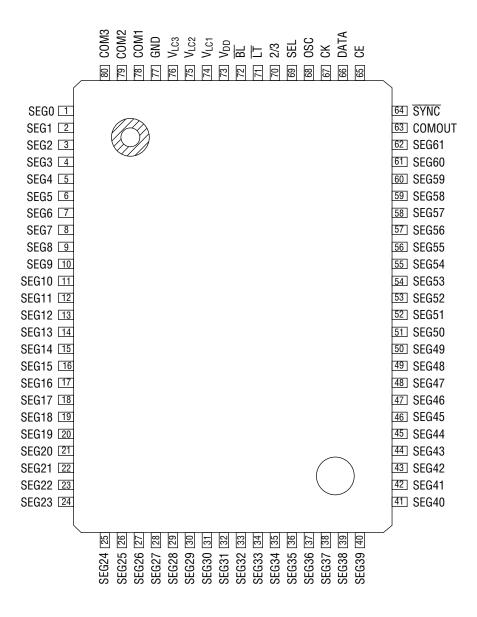

# **PIN CONFIGURATION (TOP VIEW)**

80-Pin Plastic QFP

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition | Rating                       | Unit |

|---------------------|------------------|-----------|------------------------------|------|

| Supply Voltage      | V <sub>DD</sub>  | Ta=25°C   | -0.3 to +7                   | V    |

| Input Voltage       | V <sub>IN</sub>  | Ta=25°C   | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Power Dissipation   | PD               | Ta=85°C   | 300                          | mW   |

| Storage Temperature | T <sub>STG</sub> |           | –55 to +150                  | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol          | Condition | Range                             | Unit |

|-----------------------|-----------------|-----------|-----------------------------------|------|

| Supply Voltage        | V <sub>DD</sub> |           | 4 to 6                            | V    |

| "H" Input Voltage     | V <sub>IH</sub> |           | $V_{DD}\!\times\!0.7$ to $V_{DD}$ | V    |

| "L" Input Voltage     | V <sub>IL</sub> | —         | 0 to $V_{DD} \times 0.3$          | V    |

| Shift Frequency       | fcк             |           | 0.1 to 2                          | MHz  |

| Operating Temperature | T <sub>op</sub> |           | -40 to +85                        | C°   |

### **Oscillation Circuit**

| Parameter               | Symbol           | Condition | Min.   | Тур. | Max.  | Unit |

|-------------------------|------------------|-----------|--------|------|-------|------|

| Oscillation Resistance  | R <sub>0</sub>   | —         | 20     | 100  | 120   | kΩ   |

| Oscillation Capacitance | Co               | —         | 0.0047 | 0.01 | 0.047 | μF   |

| Oscillation Frequency   | f <sub>OSC</sub> | —         | _      | 1.4  | —     | kHz  |

| COMOUT Frequency        | f <sub>COM</sub> | —         |        | 350  | _     | Hz   |

#### ELECTRICAL CHARACTERISTICS DC Characteristics

|                     | 5                 |                                                   |        | (V <sub>DD</sub>    | = 5V±20% | , Ta = -40 to       | ) +85°C) |

|---------------------|-------------------|---------------------------------------------------|--------|---------------------|----------|---------------------|----------|

| Parameter           | Symbol            | Condition                                         |        | Min.                | Тур.     | Max.                | Unit     |

| "H" Input Voltage1  | V <sub>IH1</sub>  |                                                   | *1     | $V_{DD} \times 0.7$ |          | —                   | V        |

| "L" Input Voltage1  | V <sub>IL1</sub>  |                                                   | *1     | _                   | _        | $V_{DD} \times 0.3$ | V        |

| "H" Input Voltage2  | V <sub>IH2</sub>  |                                                   | *12    | $V_{DD} 	imes 0.85$ |          | —                   | V        |

| "L" Input Voltage2  | V <sub>IL2</sub>  |                                                   | *12    | _                   | _        | 0.4                 | V        |

| Hysteresis Width    | V <sub>HS</sub>   |                                                   | *2     | _                   | 0.8      | _                   | V        |

| "H" Input Current   | IIH               | $V_{IH} = V_{DD}$                                 | *3     | -1                  |          | 1                   | μΑ       |

| "L" Input Current 1 | I <sub>IL1</sub>  | $V_{IL} = GND$                                    | *4     | -1                  | _        | 1                   | μΑ       |

| "L" Input Current 2 | I <sub>IL2</sub>  | $V_{DD} = 5V, V_{IL} = GND$                       | *5     | -15                 | -50      | -100                | μΑ       |

| Leakage Current     | Iz                | V <sub>I</sub> = V <sub>DD</sub> or GND           | *6     | -1                  | _        | 1                   | μΑ       |

| "H" Output Voltage  | V <sub>OH</sub>   | $V_{DD} = 4V, I_{OH} = -0.4mA$                    | *7     | 3.5                 |          | _                   | V        |

| "L" Output Voltage  | V <sub>OL</sub>   | V <sub>DD</sub> = 4V, I <sub>OH</sub> = 0.4mA     | *7     | _                   | _        | 0.4                 | V        |

|                     | R <sub>ONDP</sub> | V <sub>DD</sub> = 5V, I <sub>0</sub> = -0.5mA     | *8,*11 | _                   |          | 1                   | kΩ       |

| Segment Output      | R <sub>0NV1</sub> | V <sub>LC1</sub> = 3.33V, I <sub>0</sub> = ±0.5mA | *8,*11 | _                   | —        | 3                   | kΩ       |

| ON Resistance       | R <sub>0NV2</sub> | V <sub>LC2</sub> = 1.67V, I <sub>0</sub> = ±0.5mA | *8,*11 | —                   | —        | 3                   | kΩ       |

|                     | R <sub>ONV3</sub> | V <sub>LC3</sub> = 0.0V, I <sub>0</sub> = 0.5mA   | *8,*11 | —                   | —        | 3                   | kΩ       |

|                     | R <sub>ONDP</sub> | V <sub>DD</sub> = 5V, I <sub>0</sub> = -0.5mA     | *9,*11 | _                   |          | 1                   | kΩ       |

| Common Output       | R <sub>0NV1</sub> | V <sub>LC1</sub> = 3.33V, I <sub>0</sub> = ±0.5m  | *9,*11 | _                   | —        | 3                   | kΩ       |

| ON Resistance       | R <sub>ONV2</sub> | V <sub>LC2</sub> = 1.67V, I <sub>0</sub> = ±0.5mA | *9,*11 | —                   |          | 3                   | kΩ       |

|                     | R <sub>ONV3</sub> | V <sub>LC3</sub> = 0.0V, I <sub>0</sub> = 0.5mA   | *9,*11 | —                   |          | 3                   | kΩ       |

| Supply Current      | I <sub>DD</sub>   | f <sub>OSC</sub> = 1.4kHz, no load, CK=E          | )C *10 | —                   | 0.3      | 1.0                 | mA       |

\*1 Applicable to all input pins except OSC pin on the master side.

\*2 Applicable to CE, CK, and DATA input.

\*3 Applicable to CE, CK, DATA, SEL, 2/3,  $\overline{BL}$ , and  $\overline{LT}$ .

\*4 Applicable to CE, CK, DATA, SEL, and 2/3.

- \*5 Applicable to  $\overline{BL}$  and  $\overline{LT}$  input.

- \*6 Applicable to  $\overline{\text{SYNC}}$ .

- \*7 Applicable to SYNC and COMOUT.

- \*8 Applicable to SEG0 SEG61.

- \*9 Applicable to COM1 COM3.

\*10 If a voltage-dividing resistor for bias voltage generation is included (- 02 and - 03), the value does not include the current that flows through the resistor.

- \*11 If a voltage-dividing resistor for bias voltage generation is included (-02 and -03), the output ON resistance value depends on the built-in dividing resistor.

- \*12 Applicable to the OSC pin on the master side.

| Voltage-dividing resistor for bias voltage generation | <b>Voltage</b> | dividing | resistor | for bia | s voltage | generation |

|-------------------------------------------------------|----------------|----------|----------|---------|-----------|------------|

|-------------------------------------------------------|----------------|----------|----------|---------|-----------|------------|

| Code Name | Symbol           | Condition         | Min. | Тур. | Max. | Unit |

|-----------|------------------|-------------------|------|------|------|------|

| -02       | R <sub>LCD</sub> | Ta = -40 to +85°C | 0.6  | 1    | 1.4  | kΩ   |

| -03       | R <sub>LCD</sub> | Ta = -40 to +85°C | 10   | 30   | 100  | kΩ   |

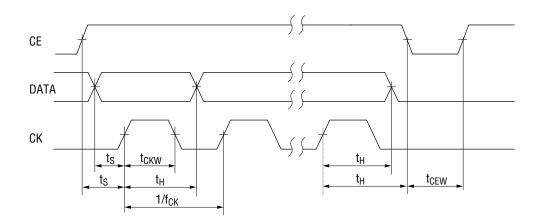

#### **AC Characteristics**

$(V_{DD} = 5V \pm 20\%, Ta = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter               | Symbol           | Condition                   | Min. | Тур. | Max. | Unit |

|-------------------------|------------------|-----------------------------|------|------|------|------|

| Maximum Clock Frequency | f <sub>CK</sub>  | —                           | 2    |      | —    | MHz  |

| Clock Pulse Width       | t <sub>CKW</sub> | _                           | 200  |      | —    | ns   |

| Data Set-up Time        | ts               | —                           | 200  | —    |      | ns   |

| Data Hold Time          | t <sub>H</sub>   | _                           | 200  | _    | —    | ns   |

| CE Pulse Width          | t <sub>CEW</sub> | —                           | 200  |      |      | ns   |

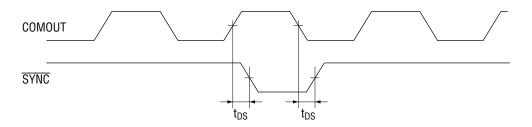

| COMOUT-SYNC Delay Time  | t <sub>DS</sub>  | C <sub>L</sub> =50pF        | —    |      | 40   | ns   |

| Oscillation Frequency   | fosc             | OSC Pin Operating Frequency |      | 1.4  | 50   | kHz  |

#### FUNCTIONAL DESCRIPTION Pin Functional Description

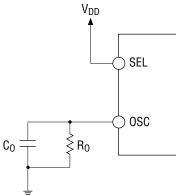

#### • OSC (pin 68)

When the master mode is selected, connect an external resistor and capacitor for the RC oscillation circuit to this pin. When the slave mode is selected, this pin becomes the input pin for an external clock signal.

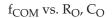

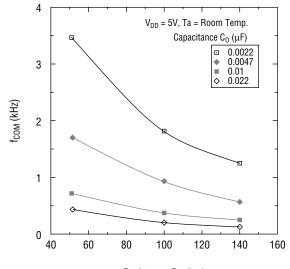

The relationship of oscillation frequency to external  $C_O$  and  $R_O$ , when the master mode is selected, is shown below.

$$f_{OSC} = \frac{1}{0.69 \times R_O \times C_O}$$

(Ta = 25 °C)

Example: When  $C_O = 0.01 \mu$ F and  $R_O = 100 k\Omega$  the oscillation frequency,  $f_{OSC}$ , is approximately 1.4 kHz.

#### • CE (pin 65)

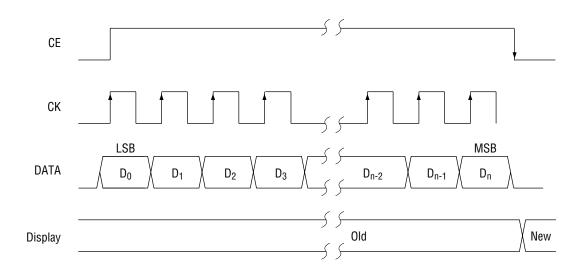

This is a chip select input pin. Input data is valid only when this pin is set to "H". Data that is input into the 72-stage shift register synchronously with the rising edge of CK will be latched with the falling edge of this pin, and the display will be updated. A Schmitt trigger is built into the input area.

#### • DATA (pin 66)

This is a data input pin. Data input is valid only when the CE pin is set to "H". The 72-stage shift register contents are latched with the falling edge of this pin, and the display will be updated. A Schmitt trigger is built into the input area.

#### • CK (pin 67)

This is a serial data shift lock input pin. Data is input synchronously with the rising edge of the shift clock. A Schmitt trigger is built into the input area. Data can be latched even if the shift clock is stopped, since a static shift register is used.

# • SEL (pin 69)

This is an input pin used to switch between the master and the slave modes when a multi-chip configuration is used. Set this pin to "H" to select the master mode, and to "L" to select the slave mode.

# • SYNC (pin 64)

When the master mode is selected, this pin becomes an output pin for synchronous signals. When the slave mode is selected, this pin becomes an input pin for synchronous signals.

### • 2/3 (pin 70)

This pin is used to switch between 1/2 and 1/3 duty. Set this pin to "H" to select 1/2 duty, and to "L" to select 1/3 duty.

#### • COMOUT (pin 63)

This is an output pin for clock synchronization. A frequency equal to  $f_{\rm OSC}/4$  is output from this pin.

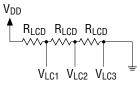

# • V<sub>LC1</sub> (pin 74), V<sub>LC2</sub> (pin 75) and V<sub>LC3</sub> (pin 76)

When the code is -01, these pins are used as input pins for LCD bias voltage. The  $V_{LC3}$  pin should be connected with GND. The settings for these pins should be as follows:

$V_{DD} \ge V_{LC1} \ge V_{LC2} \ge V_{LC3} = GND$

When the code is -02 or -03,  $V_{LC1}$  and  $V_{LC2}$  pins should be left open, and  $V_{LC3}$  pin connected with GND since a voltage-dividing resistor for bias voltage generation has been built in. (However, when the code setting is -02 or -03, and if 1/2 duty is selected,  $V_{LC1}$  and  $V_{LC2}$  should be externally shorted.)

#### • COM1-COM3 (pins 78 to 80)

These are common signal output pins for driving the LCD. In the 1/2 duty mode, leave the COM3 pin open.

#### • SEG0-SEG61 (pins 1 to 62)

These are segment signal output pins for driving the LCD. 1/2 or 1/3 duty can be selected using the 2/3 pin, and 1/2 or 1/3 bias can be selected using pins V<sub>LC1</sub> through V<sub>LC3</sub>.

# • LT (pin 71)

This is an input pin for controlling the display on the LCD. If this pin is set to "L", all segments will be turned on. A pull-up resistor is included.

# • BL (pin 72)

This is an input pin for controlling the display on the LCD. If this pin is set to "L", all segments will be turned off. A pull-up resistor is included.

#### Data Input

Display data should be input according to the timing diagram below.

\* Display Data

| Duty Mode | 2/3 Pin | Data Length           | COM Data                                                                  |  |  |  |

|-----------|---------|-----------------------|---------------------------------------------------------------------------|--|--|--|

| 1/2 Duty  | н       | 48-Bit (D0 - D47) × 3 | COM1: D0, D2D0+2n<br>COM2: D1, D3D1+2n<br>n = 0 - 61                      |  |  |  |

| 1/3 Duty  | L       | 72-Bit (D0 - D71) × 3 | COM1: D0, D3D0+3n<br>COM2: D1, D4D1+3n<br>COM2: D2, D5D2+3n<br>n = 0 - 61 |  |  |  |

\* Address Data

The most significant 3 bits (the last 3 bits) contain the address data.

Address data: "100" — SEG0 - SEG20 "010" — SEG21 - SEG41

"001" - SEG21 - SEG41"001" - SEG42 - SEG61

Since the last 3 bits correspond to each group of segments, if the address is "110", SEG0 - SEG20 and SEG21 - SEG41 are all updated at a time in accordance with the data.

| D0                       | D1        | D2        | D3        | D4        | D5        | ( (      | D39        | D40        | D41        | D42- | D44  | D45      | D46      | D47      |

|--------------------------|-----------|-----------|-----------|-----------|-----------|----------|------------|------------|------------|------|------|----------|----------|----------|

| S0                       | S0        | S1        | S1        | S2        | S2        | > >      | S19        | S20        | S20        |      | >    | 4        | 0        | 0        |

| C1                       | C2        | C1        | C2        | C1        | C2        |          | C2         | C1         | C2         |      |      | 1        | 0        | U        |

| D42 - D44 are Dummy Data |           |           |           |           |           |          |            |            |            |      |      |          |          |          |

|                          |           |           |           |           |           |          |            |            |            |      |      |          |          |          |

| D0                       | D1        | D2        | D3        | D4        | D5        | ( (      | D39        | D40        | D41        | D42- | D44  | D45      | D46      | D47      |

| D0<br>S21                | D1<br>S21 | D2<br>S22 | D3<br>S22 | D4<br>S23 | D5<br>S23 | <u> </u> | D39<br>S40 | D40<br>S41 | D41<br>S41 | D42- | _D44 |          | D46      |          |

| -                        |           |           | -         |           |           |          |            | -          |            | D42- | _D44 | D45<br>0 | D46<br>1 | D47<br>0 |

1) Data format when 1/2 duty (124 segments) is selected.

| D0        | D1        | D2        | D3        | D4                | D37       | D38       | D39       | D40-            | <sub>&lt;</sub> D44 | D45 | D46 | D47 |

|-----------|-----------|-----------|-----------|-------------------|-----------|-----------|-----------|-----------------|---------------------|-----|-----|-----|

| S42<br>C1 | S42<br>C2 | S43<br>C1 | S43<br>C2 |                   | S60<br>C2 | S61<br>C1 | S61<br>C2 |                 | >                   | 0   | 0   | 1   |

|           |           | ļ         | ļ         | $\longrightarrow$ |           |           |           | $ \rightarrow $ | <u> </u>            |     |     |     |

D40 - D44 are Dummy Data

2) Data format when 1/3 duty (186 segments) is selected.

| D0 D1 D2 D | 3 D4 D5        | D60             | D61 D62          | D63- <sub>&lt; &lt;</sub> D68 | D69 | D70 | D71 |

|------------|----------------|-----------------|------------------|-------------------------------|-----|-----|-----|

|            | S1 S1<br>C2 C3 | >>> S20<br>< C1 | S20 S20<br>C2 C3 |                               | 1   | 0   | 0   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | D0 | D1 | D2 | D3 | D4 | D5 | ( (           | D60       | D61 | D62 | D63- | <sub>&lt;</sub> D68 | D69 | D70 | D71 |

|---------------------------------------------------------|----|----|----|----|----|----|---------------|-----------|-----|-----|------|---------------------|-----|-----|-----|

|                                                         |    |    |    |    |    |    | $\rightarrow$ | S41<br>C1 |     | -   |      | $\sim$              | 0   | 1   | 0   |

D63 - D68 are Dummy Data

| D0 D1 D2        | D3 D4     | $\langle \langle \rangle$ | D57       | D58       | D59       | D60- | D68 | D69 | D70 | D71 |

|-----------------|-----------|---------------------------|-----------|-----------|-----------|------|-----|-----|-----|-----|

| S42S42S42C1C2C3 | S43<br>C1 | > ><br>< <                | S61<br>C1 | S61<br>C2 | S61<br>C3 |      | >   | 0   | 0   | 1   |

D60 - D68 are Dummy Data

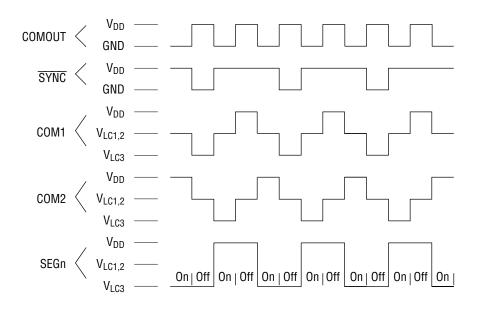

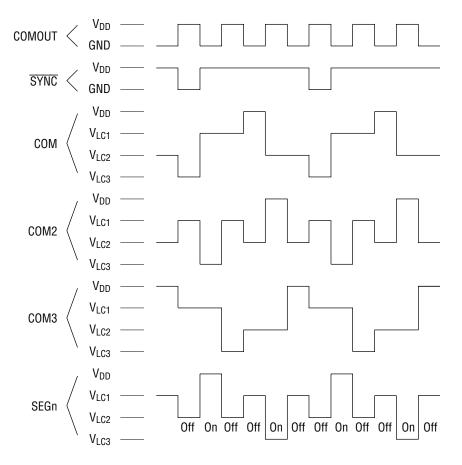

#### LCD Display Timing

1) 1/2 duty mode (2/3 = "H")

Note: When 1/2 duty is selected and 1/2 bias is used, perform the following: - When the code is -01, short  $V_{LC1}$  and  $V_{LC2}$ , and supply the bias voltage. - When the code is -02 or -03, externally short  $V_{LC1}$  and  $V_{LC2}$ .

### 2) 1/3 duty mode (2/3 = "L")

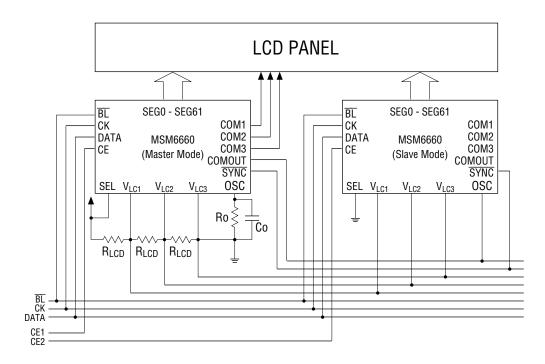

#### Pin Functions in a Multi-chip Configuration

When MSM6660 ICs are used in a multi-chip configuration, one of them is used in the master mode to generate the common frequency and the synchronization signal. These signals are then received by the slave mode ICs to enable synchronous operation.

| Symbol | Pin | Master Mode LSI                            | Slave Mode LSI              |

|--------|-----|--------------------------------------------|-----------------------------|

| COMOUT | 63  | Connect to Slave IC OSC                    | Open (Unused)               |

| SYNC   | 64  | Connect to Slave IC SYNC                   | Connect to Master IC SYNC   |

| OSC    | 68  | Connect an external resistor and capacitor | Connect to Master IC COMOUT |

| SEL    | 69  | "H" (V <sub>DD</sub> ) level               | "L" (GND) level             |

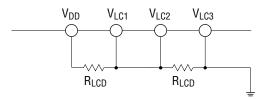

#### LCD Bias Voltage Application Method

1) For 1/2 bias (when 1/2 duty is selected)

- Note: The above case is for code -01. When the code is -02 or -03, an external voltage-dividing resistor is not needed, because it is already built into the type signified by these settings. However, pins  $V_{LC1}$  and  $V_{LC2}$  must be shorted externally.

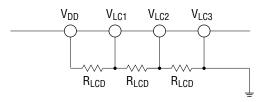

- 2) For 1/3 bias (when 1/3 duty is selected)

Note: The above case is for the code -01. When the code is -02 or -03, an external voltagedividing resistor is not needed, because it is already built into the type signified by these settings. Leave  $V_{LC1}$  through  $V_{LC3}$  open.

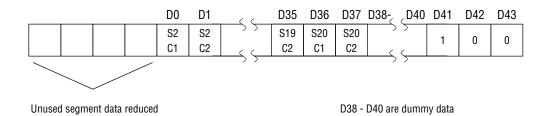

#### Method of Reducing the Transfer Time When Unused Segments Exist

When unused segments exist, it is not required to transfer the data of unused segments. This allows the data transfer time to be reduced. However, the last 3 bits are address data.

When SEG0 and 1 are not used, the data can be reduced from the original 48 bits to 44 bits.

# **APPLICATION CIRCUIT**

#### For 1/3 duty, 1/3 bias (when the code setting is -01)

# **REFERENCE DATA**

f<sub>OSC</sub> vs. V<sub>DD</sub>

Resistance  $\mathsf{R}_0 \; (\mathsf{k}\Omega)$

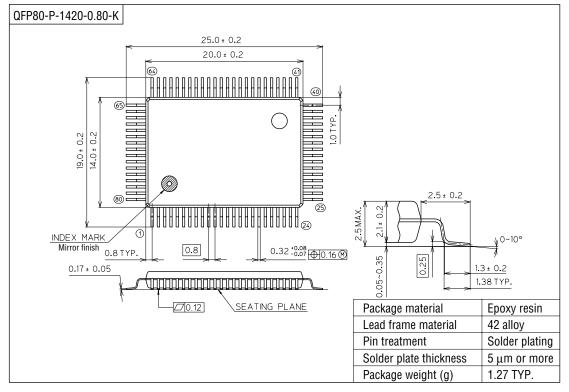

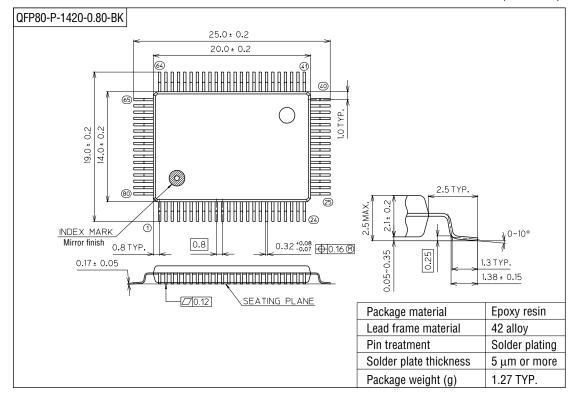

# PACKAGE DIMENSIONS

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).