# <del>LC66556B,</del> 66558B

# Four-Bit Single-Chip Microcontrollers with 6 k and 8 k Bytes of On-Chip ROM

### **Overview**

The LC66556B and LC66558B are four-bit single-chip CMOS microcontrollers that integrate on a single chip all the functions required in a microcontroller, including ROM, RAM, I/O ports, two serial interfaces, comparator inputs, three-value inputs, timers and interrupts. These products are provided in a 64-pin package.

These products differ from the earlier LC66558A Series in the power supply voltage range and certain other electrical characteristics.

### **Features and Functions**

- On-chip ROM and RAM with 6 k (or 8 k) byte and 512 × 4-bit capacities

- The same instruction set (with 127 instructions) as the LC66000 Series (except that the SB instruction is not supported)

- I/O ports: 54 pins

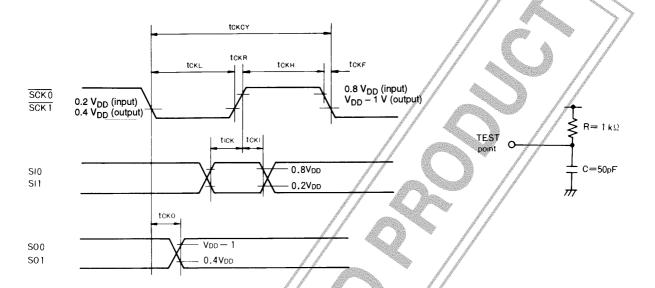

- 8-bit serial interface: two circuits (16-bit cascade connection supported)

- Instruction cycle: 0.92 to 10 μs (at 3 to 5.5 V)

- Powerful timers and prescalers

12-bit timer: time-limit timer, event counter, pulse width measurement, square wave output

8-bit timer: time-limit timer, event counter, PWM output, square wave output

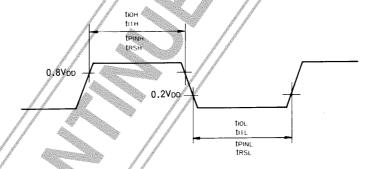

- Powerful 11-factor 8-vector interrupt system External interrupts: 6 factors/3 vectors

Internal interrupts: 5 factors/5 vectors

12-bit prescaler; time base functions

- Plexible I/O functions

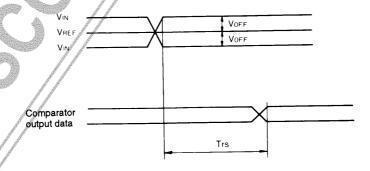

Comparator inputs, three-value inputs, 20 mA drive outputs, 15 V breakdown voltage pins, pull-up/opendrain option switching possible

- Runaway detection function (watchdog timer) option

- 8-bit I/O function

- Power saving functions: halt and hold modes Package; DIP64S, QFP64E

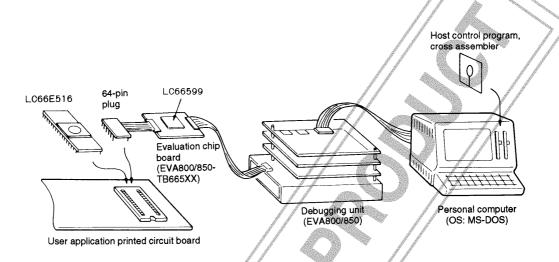

- Evaluation LSI: LC66599 (evaluation chip) + EVA850/800-TB665XX LC66E516 (On-chip EPROM microcontrollers) LC66P516 (On-chip OTPROM microcontrollers)

### **Series Structure**

| Type No.                | Pin count | ROM capacity       | RAM capacity | acity Package      |                   | Features                                             |

|-------------------------|-----------|--------------------|--------------|--------------------|-------------------|------------------------------------------------------|

| LC66304A/306A/308A      | 42        | 4 k/6 k/8 kB       | 512 W        | DIP42S             | QFP48E            |                                                      |

| LC66404A/406A/408A      | 42        | 4 k/6 k/8 kB       | 512 W        | DIP42S             | QFP48E            | Normal versions<br>4.0 to 6.0 V/0.92 µs              |

| LC66506B/508B/512B/516B | 64        | 6 k/8 k/12 k/16 kB | 512 W        | DIP64S             | QFP64A            | 1.0 to 0.0 t/0.02 pc                                 |

| LC66354A/356A/358A      | 42        | 4 k/6 k/8 kB       | 512 W        | DIP42S             | QFP48E            |                                                      |

| LC66354S/356S/358S*     | 42        | 4 k/6 k/8 kB       | 512 W        |                    | QFP44M            | Low-voltage versions<br>2.2 to 5.5 V/3.92 µs         |

| LC66556A/558A/562A/566A | 64        | 6 k/8 k/12 k/16 kB | 512 W        | DIP64S             | QFP64E            | 2.2 to 0.0 v/0.02 po                                 |

| LC66354B/356B/358B      | 42        | 4 k/6 k/8 kB       | 512 W        | DIP42S             | QFP48E            |                                                      |

| LC66556B/558B 64        |           | 6 k/8 k            | 512 W        | DIP64S             | QFP64E            | Low-voltage high-speed versions 3.0 to 5.5 V/0.92 µs |

| LC66562B/566B           | 64        | 12 k/16 kB         | 512 W        | DIP64S             | QFP64E            | 0.0 to 0.0 1/0.02 pc                                 |

| LC66E308                | 42        | EPROM 8 kB         | 512 W        | DIC42S<br>(window) | QFC48<br>(window) |                                                      |

| LC66P308                | 42        | OTPROM 8 kB        | 512 W        | DIC42S             | QFP48E            |                                                      |

| LC66E408                | 42        | EPROM 8 kB         | 512 W        | DIC42S<br>(window) | QFC48<br>(window) | Evaluation (window) versions & OTP versions          |

| LC66P408                | 42        | OTPROM 8 kB        | 512 W        | DIC42S             | QFP48E            | 4.5 to 5.5 V/0.92 μs                                 |

| LC66E516                | 64        | EPROM 16 kB        | 512 W        | DIC64S<br>(window) | QFC64<br>(window) |                                                      |

| LC66P516                | 64        | OTPROM 16 kB       | 512 W        | DIC64S             | QFP64E            |                                                      |

Note: \*: Under development

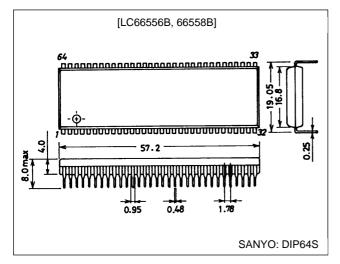

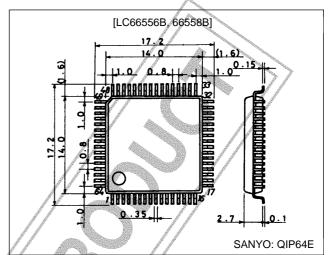

### **Package Dimensions**

unit: mm

### 3071-DIP64S

unit: mm 3159-QFP64E

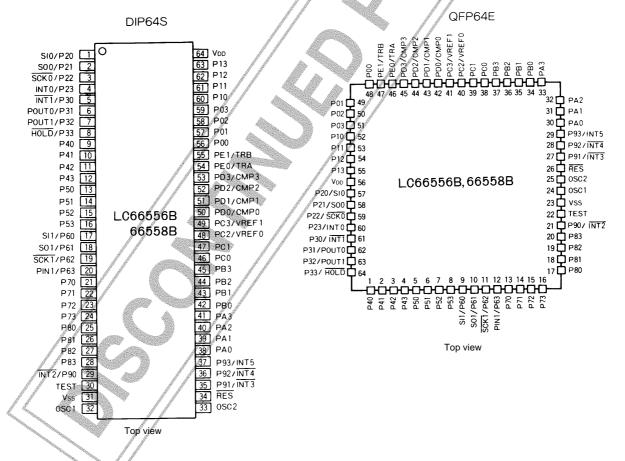

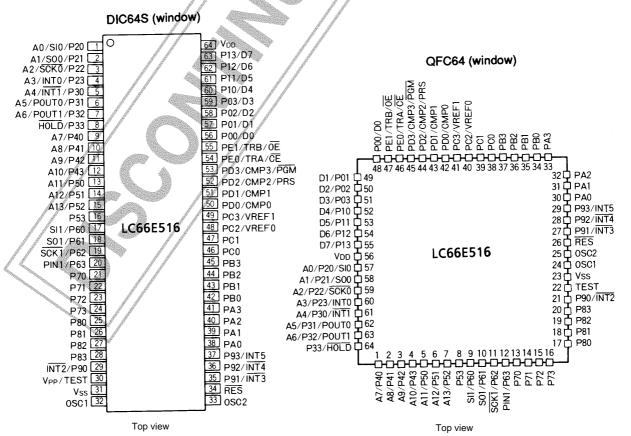

### **Pin Assignments**

We recommend using reflow soldering as the QFP solder mounting technique.

Consult your Sanyo representative concerning temperature and other conditions if techniques in which the whole package is to be immersed in a solder dip bath, i.e. solder dip techniques, are to be used.

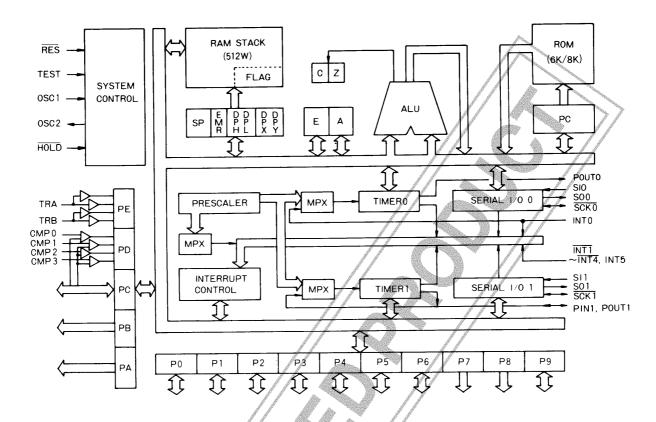

### **System Block Diagram**

### Differences between the LC66556B/LC66558B and the LC66508B Series

| Item                                                                                       | LC66508B series<br>(Including the EVA850/800-TB665XX tool)                                   | LC66556B, 66558B                                    |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------|

| System differences  • Hardware wait time (number of cycles) when hold mode is cleared      | 65536 cycles<br>At 4 MHz (Tcyc = 1 μs); about 64 ms                                          | 16384 cycles<br>At 4 MHz (Tcyc = 1 μs): about 16 ms |

| Value of timer 0 at reset<br>(including the value after hold mode is cleared)              | The value FF0 is loaded.                                                                     | The value FFC is loaded.                            |

| Differences in the major characteristics  • Operating power supply voltage/operating speed | LC66512B, 516B<br>4.0 to 6.0 V/0.92 to 10 μs<br>LC66E516, P516<br>4.5 to 5.5 V/0.92 to 10 μs | 3.0 to 5.5V/0.92 to 10 μs                           |

- 1. An RC oscillator cannot be used with the LC66556B and LC66558B

- In addition, certain other output current and comparator input voltage specifications differ.

For details, see the individual catalogs for the LC66508B, LC66E516 and LC66P516.

Keep these differences in mind when using the LC66E516 and LC66P516 evaluation chips.

### **Pin Function Overview**

| Pin                                        | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                  | Output drive type                                                                               | Option                                                                        | Value on reset       |

|--------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------|

| P00<br>P01<br>P02<br>P03                   | I/O | I/O ports P00 to P03 Input or output in 4-bit or 1-bit units P00 to P03 have control functions in HALT mode.                                                                                                                                                                                                                                                                                                              | P-channel: pull-up MOS type N-channel: small sink current type                                  | Either with pull-up MOS or N-channel OD output     Reset output level         | High or low (option) |

| P10<br>P11<br>P12<br>P13                   | I/O | I/O ports P10 to P13 • Input or output in 4-bit or 1-bit units                                                                                                                                                                                                                                                                                                                                                            | P-channel: pull-up MOS type N-channel: small sink current type                                  | Either with pull-up     MOS or N-channel OD     output     Reset output level | High or low (option) |

| P20/Si0<br>P21/SO0<br>P22/SCK0<br>P23/INT0 | 1/0 | I/O ports P20 to P23 Input or output in 4-bit or 1-bit units P20 is also used as the serial input SI0 pin. P21 is also used as the serial output SO0 pin. P22 is also used as the serial clock SCK0 pin. P23 is also used as the INT0 interrupt request, as the timer 0 event counter and for pulse width measurement input.                                                                                              | P-channel: CMOS type N-channel: small sink current type +15 V withstand voltage in N-channel OD | Either CMOS or N-channel OD output                                            | High                 |

| P30/INT1<br>P31/POUT0<br>P32/POUT1         | I/O | I/O ports P30 to P32 Input or output in 3-bit or 1-bit units P30 is also used as the INT1 interrupt request. P31 is also used for square wave output from timer 0. P32 is also used for square wave output from timer 1 and PWM output.                                                                                                                                                                                   | P-channel: CMOS type N-channel: small sink current type +15 V withstand voltage in N-channel OD | Either CMOS or N-<br>channel OD output                                        | High                 |

| P33/HOLD                                   |     | Hold mode control input  Hold mode is entered if a HOLD instruction is executed when HOLD is fow.  When in hold mode, the CPU is reactivated by setting HOLD to the high level.  P33 can also be used as an input port together with P30 to P32.  When P33/HOLD is low, the CPU will not be reset by a low level on RES. Therefore, RES cannot be used in applications that set P33/HOLD low when power is first applied. |                                                                                                 |                                                                               |                      |

| P40<br>P41<br>P42<br>P43                   | 1/Q | I/O ports P40 to P43  • Input or output in 4-bit or 1-bit units  • I/O in 8-bit units when used in conjunction with P50 to P53  • Output of 8-bit ROM data when used in conjunction with P50 to P53                                                                                                                                                                                                                       | P-channel: pull-up MOS type N-channel: small sink current type                                  | Either CMOS or N-<br>channel OD output                                        | High                 |

| P50<br>P51<br>P52<br>P53                   | I/O | VO ports P50 to P53  Input or output in 4-bit or 1-bit units  VO in 8-bit units when used in conjunction with P40 to P43  Output of 8-bit ROM data when used in conjunction with P40 to P43                                                                                                                                                                                                                               | P-channel: pull-up MOS type N-channel: small sink current type                                  | Either CMOS or N-<br>channel OD output                                        | High                 |

### Continued from preceding page.

| Pin                                          | I/O | Function                                                                                                                                                                                                                                                         | Output drive type                                                                                                    | Option                                                    | Value on reset       |

|----------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------|

| P60/SI1<br>P61/SO1<br>P62/SCK1<br>P63/PIN1   | I/O | I/O ports P60 to P63 Input or output in 4-bit or 1-bit units P60 is also used as the serial input S11 pin. P61 is also used as the serial output SO1 pin. P62 is also used as the serial clock SCK1 pin. P63 is also used as the timer 1 event counter input.    | P-channel: CMOS type N-channel: small sink current type +15 V withstand voltage in N-channel OD                      | CMQS or N-channel OD output                               | High                 |

| P70<br>P71<br>P72<br>P73                     | 0   | Dedicated output ports P70 to P73  Output in 4-bit or 1-bit units The latched output data can be read with input instructions.                                                                                                                                   | P-channel: pull-up MOS type N-channel: intermediate sink<br>current type +15 V withstand voltage in N-<br>channel OD | With pull-up MOS transistor or N-channel OD output        | High                 |

| P80<br>P81<br>P82<br>P83                     | 0   | Dedicated output ports P80 to P83  Output in 4-bit or 1-bit units The latched output data can be read with input instructions. Ap-channel OD output option is available.                                                                                         | P-channel: CMOS type     N-channel: small sink current type                                                          | CMOS or P-channel OD output     The output level at reset | High or low (option) |

| P90/INT2<br>P91/INT3<br>P92/INT4<br>P93/INT5 | I/O | I/O ports P90 to P93  Input or output in 4-bit or 1-bit units P90 is also used as the INT2 interrupt request. P91 is also used as the INT3 interrupt request. P92 is also used as the INT4 interrupt request. P93 is also used as the INT5 interrupt request.    | P-channel: CMOS type     N-channel: small sink current type                                                          | CMOS or N-channel     OD output                           | High                 |

| PA0<br>PA1<br>PA2<br>PA3                     | 0   | Dedicated output ports PA0 to PA3  Output in 4-bit or 1-bit units The latched output data can be read with input instructions.                                                                                                                                   | P-channel: pull-up MOS type     N-channel: intermediate sink current type                                            | With pull-up MOS or<br>N-channel OD output                | High                 |

| PB0<br>PB1<br>PB2<br>PB3                     | 0   | Dedicated output ports PB0 to PB3  Output in 4-bit or 1-bit units The latched output data can be read with input instructions.                                                                                                                                   | P-channel: CMOS type N-channel: small sink current type                                                              | With pull-up MOS or<br>N-channel OD output                | High                 |

| PC0<br>PC1<br>PC2/VREF0<br>PC3/VREF1         | 1/0 | I/O ports PC0 to PC3 Input or output in 4-bit or 1-bit units PC2 is also used as the VREF0 comparator comparison voltage pin PC3 is also used as the VREF1 comparator comparison voltage pin.                                                                    |                                                                                                                      | CMOS or N-channel<br>OD output                            | High                 |

| PD0/CMP0<br>PD1/CMP1<br>PD2/CMP2<br>PD3/CMP3 | 1   | Dedicated input ports PD0 to PD3 Can be switched to function as comparator inputs under software control. The comparison voltage for PD0 is VREF0. The comparison voltage for PD1 to PD3 is VREF1. Comparison can be specified in units of PD0, PD1, (PD2, PD3). |                                                                                                                      |                                                           | Normal input         |

### Continued from preceding page.

| Pin                                | I/O | Function                                                                                                                   | Output drive type | Option                                                                 | Value on reset |

|------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------|----------------|

| PE0/TRA<br>PE1/TRB                 | I   | Dedicated input port     Can be switched under software control to function as a three-value input port.                   |                   |                                                                        | Normal input   |

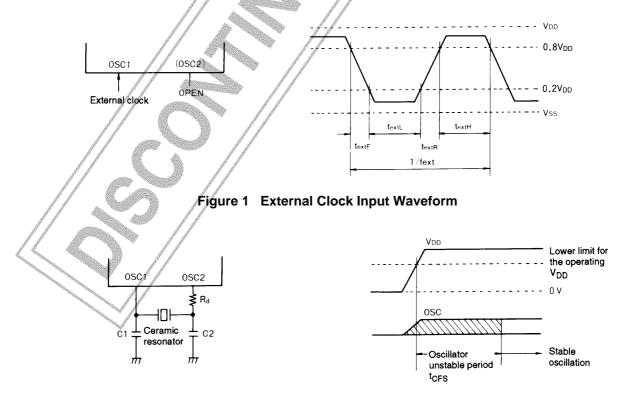

| OSC1<br>OSC2                       | 0   | System clock oscillator connections<br>When an external clock is used,<br>leave OSC2 open and input the<br>signal to OSC1. |                   | Selection of either a<br>ceramic oscillator or<br>external clock input |                |

| RES                                | I   | System reset input  • The CPU is initialized (reset) if a low level is input to RES when P33/HOLD is at the high level.    |                   |                                                                        |                |

| TEST                               | I   | CPU testing This pin must be connected to V <sub>SS</sub> during normal operation.                                         |                   |                                                                        |                |

| V <sub>DD</sub><br>V <sub>SS</sub> |     | Power supply connections                                                                                                   |                   |                                                                        |                |

Note: Pull-up MOS output: An output with a pull-up MOS transistor

CMOS output: A complementary output

OD output: An open drain output

### **User Option Types**

1. Port 0, 1 and 8 reset time output level option

The output levels of I/O ports 0, 1 and 8 at reset can be selected from the following two options in 4-bit units.

| Option                          | Conditions and notes              |

|---------------------------------|-----------------------------------|

| High level output at reset time | Ports 0, 1 and/or 8 in 4-bit sets |

| Low level output at reset time  | Ports 0, 1 and/or 8 in 4-bit sets |

### 2. Oscillator circuit option

| Option             | Circuit                 | Conditions and notes                         |

|--------------------|-------------------------|----------------------------------------------|

| External clock     | OSC1                    | This input is a Schmitt specification input. |

| Ceramic oscillator | Ceramic Eresonator OSC2 |                                              |

Note: There is no RC oscillator option.

### 3. Watchdog timer option

The presence or absence of a program runaway detection function (watchdog timer) can be selected as an option.

### 4. Port output type option

• One of the following two output circuit options can be selected for each bit in ports P0, P1, P2, P3 (except for the P33/HOLD pin), P4, P5, P6, P7, P9, PA, PB and PC.

| Option                              | Circuit                 | Conditions and notes                                                                                                                                                                       |

|-------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open drain output                   | Output data input data  | P7, PA and PB are output only pins. P2, P3, P6 and P9 are Schmitt inputs.                                                                                                                  |

| Built-in pull-up<br>resistor output | Output data  Input data | P7, PA and PB are output only pins. P2, P3, P6 and P9 are Schmitt inputs. CMOS outputs (P2, P3, P6, P9 and PC) and pull-up MOS outputs (P0, P1, P4, P5, P7, PA and PB) are differentiated. |

• The P8 circuits can be selected from the following two options in bit units.

| Option                              | Circuit          | Conditions and notes |

|-------------------------------------|------------------|----------------------|

| Open drain output                   | Output data      |                      |

| Built-in pull-up<br>resistor output | Output data  DSB |                      |

• The PD comparator inputs and the PE three-value inputs are selected in software.

# **Specifications**

# Absolute Maximum Ratings at $Ta=25^{\circ}C,\,V_{SS}=0~V$

| Parameter                   | Symbol                | Conditions                                                                 | Ratings                       | Unit  | Note     |

|-----------------------------|-----------------------|----------------------------------------------------------------------------|-------------------------------|-------|----------|

| Maximum supply voltage      | V <sub>DD</sub> max   | $V_{DD}$                                                                   | -0.3 to +7.0                  | V     |          |

| Input voltage               | V <sub>IN</sub> (1)   | P2, P3 (except for the P33/HOLD pin) and P6                                | -0.3 to +15.0                 | V     | 1        |

| input voltage               | V <sub>IN</sub> (2)   | Other inputs                                                               | -0.3 to V <sub>DD</sub> + 0.3 | V     | 2        |

| Output voltage              | V <sub>OUT</sub> (1)  | P2, P3 (except for the P33/HOLD pin),<br>P6, P7 and PA                     | -0.3 to +15.0                 | V     | <b>1</b> |

|                             | V <sub>OUT</sub> (2)  | Other outputs                                                              | –0.3 to V <sub>DD</sub> + 0.3 | V/    | 2        |

|                             | I <sub>ON</sub> (1)   | P0, P1, P2, P3 (except for the P33/HOLD pin),<br>P4, P5, P6, P8, P9 and PC | 4                             | mA    | 3        |

| Output ourrent nor nin      | I <sub>ON</sub> (2)   | P7, PA, PB                                                                 | 20                            | // mA | 3        |

| Output current per pin      | -I <sub>OP</sub> (1)  | P0, P1, P4, P5, P7, PA, PB                                                 | 2                             | mA    | 4        |

|                             | -I <sub>OP</sub> (2)  | P2, P3 (except for the P33/HOLD pin),<br>P6, P8, P9 and PC                 | 4                             | mA    | 4        |

|                             | Σl <sub>ON</sub> (1)  | P2, P3 (except for the P33/HOLD pin),<br>P4, P5, P6, P7 and P8             | 75                            | mA    | 3        |

| Total pin aurrent           | Σl <sub>ON</sub> (2)  | P0, P1, P9, PA, PB, PC                                                     | 75                            | mA    | 3        |

| Total pin current           | –Σl <sub>OP</sub> (1) | P2, P3 (except for the P33/HOLD pin),<br>P4, P5, P6, P7 and P8             | 25                            | mA    | 4        |

|                             | –Σl <sub>OP</sub> (2) | P0, P1, P9, PA, PB, PC                                                     | 25                            | mA    | 4        |

| Allowable power dissipation | Pd max                | Ta = -30 to +70°C: DIP64S (QIP64E)                                         | 600 (430)                     | mW    | 5        |

| Operating temperature       | Topr                  |                                                                            | -30 to +70                    | °C    |          |

| Storage temperature         | Tstg                  |                                                                            | -55 to +125                   | °C    |          |

- Note: 1. Applies to open drain output specification pins. The rating from the "other pin" entry applies for specifications other than the open drain output specification.

- 2. Levels up to the free-running oscillation level are allowed for the oscillator input and output pins.

- 3. Inflow current (For P8, the CMOS output specifications apply.)

- 4. Outflow current (Applies to pull-up output specification and CMOS output specification pins except P8.)

- We recommend using reflow soldering methods to mount the QFP package version.

Contact your Sanyo sales representative to discuss process conditions if techniques in which the whole package is immersed in a solder bath (solder dip or spray techniques) are used.

# Allowable Operating Ranges at $Ta = -30 \text{ to} + 70^{\circ}\text{C}$ , $V_{SS} = 0 \text{ V}$ , $V_{DD} = 3.0 \text{ to} 5.5 \text{ V}$ unless specified otherwise

| Parameter                                    | Symbol                  | Conditions                                                                               | min                     | typ | max                      | Unit        | Note |

|----------------------------------------------|-------------------------|------------------------------------------------------------------------------------------|-------------------------|-----|--------------------------|-------------|------|

| Operating supply voltage                     | N <sub>DD</sub>         | V <sub>DD</sub>                                                                          | 3.0                     |     | 5.5                      | V           |      |

| Memory retention supply voltage              | V <sub>DD</sub> (H)     | V <sub>DD</sub> . In hold mode                                                           | 1.8                     |     | 5.5                      | V           |      |

|                                              | V <sub>IH</sub> (1)     | P2, P3 (except for the P33/HOLD pin), P6:<br>With the output n-channel transistor off    | 0.8 V <sub>DD</sub>     |     | 13.5                     | V           | 1    |

| Input high level Voltage                     | V <sub>IH</sub> (2)     | P33/HOLD, P9, RES, OSC1:<br>With the output n-channel transistor off                     | 0.8 V <sub>DD</sub>     |     | V <sub>DD</sub>          | V           | 2    |

| Input high level voltage                     | V <sub>IH</sub> (3)     | P0, P1, P4, P5, PC, PD, PE:<br>With the output n-channel transistor off                  | 0.75<br>V <sub>DD</sub> |     | V <sub>DD</sub>          | ٧           | 3    |

|                                              | V <sub>IH</sub> (4)     | PE: When three-state input is used                                                       | 0.8 V <sub>DD</sub>     |     | V <sub>DD</sub>          | V           |      |

| Intermediate level input voltage             | V <sub>IM</sub>         | PE: When three-state input is used                                                       | 0.4 V <sub>DD</sub>     |     | 0.6 V <sub>DD</sub>      | V           |      |

|                                              | V <sub>CMM</sub> (1)    | PD0, PC2: When comparator input is used                                                  | 1.5                     |     | V <sub>DD</sub>          | V           |      |

| Common-mode input voltage range              | V <sub>CMM</sub> (2)    | PD1, PD2, PD3, PC3: When comparator input is used                                        | V <sub>SS</sub>         |     | V <sub>DD</sub> –<br>1.5 | V           |      |

|                                              | V <sub>JL</sub> (1)     | P2, P3 (except for the P33/HOLD pin), P6, P9, RES, OSC1:N-channel output, transistor off | V <sub>SS</sub>         |     | 0.2 V <sub>DD</sub>      | V           | 2    |

|                                              | / V <sub>IL</sub> (2)   | P33/ <del>HOLD</del> : V <sub>DD</sub> = 1.8 to 5.5 V                                    | V <sub>SS</sub>         |     | 0.2 V <sub>DD</sub>      | V           |      |

| Low level input voltage                      | V <sub>IL</sub> (3)     | P0, P1, P4, P5, PC, PD, PE, TEST: N-channel output, transistor off                       | V <sub>SS</sub>         |     | 0.25<br>V <sub>DD</sub>  | V           | 3    |

|                                              | V <sub>IL</sub> (4)     | PE: When three-state input is used                                                       | V <sub>SS</sub>         |     | 0.2 V <sub>DD</sub>      | V           |      |

| Operating frequency (instruction cycle time) | fop (T <sub>CYC</sub> ) |                                                                                          | 0.4 (10)                |     | 4.35<br>(0.92)           | MHz<br>(µs) |      |

Note: 1. Applies to open drain specification pins. However, the rating for V<sub>IH</sub> (2) applies to the P33/HOLD pin. Ports P2, P3 and P6 cannot be used as input pins when CMOS output specifications are used.

- 2. Applies to open drain specification pins. P9, which has CMOS output specifications, can be used as input pins.

- 3. When PE is used as a three-value input, V<sub>IH</sub> (4), V<sub>IM</sub> and V<sub>IL</sub> (4) apply. Port PC cannot be used as input pins when CMOS output specifications are used.

#### Continued from preceding page.

|    | Parameter                                         | Symbol                                | Conditions                                                                                                                                  | min | typ | max  | Unit | Note |  |

|----|---------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|------|--|

| [E | [External clock input conditions]                 |                                       |                                                                                                                                             |     |     |      |      |      |  |

|    | Frequency                                         | f <sub>ext</sub>                      | OSC1: See Figure 1. With the signal input to OSC1 and with OSC2 open (with external clock input selected for the oscillator circuit option) | 0.4 |     | 4.35 | MHz  |      |  |

|    | Pulse width t <sub>extH</sub> , t <sub>extL</sub> |                                       | OSC1: See Figure 1. With the signal input to OSC1 and with OSC2 open (with external clock input selected for the oscillator circuit option) | 100 |     |      | an s |      |  |

|    | Rise and fall times                               | t <sub>extR</sub> , t <sub>extF</sub> | OSC1: See Figure 1. With the signal input to OSC1 and with OSC2 open (with external clock input selected for the oscillator circuit option) |     |     | 30   | ns   |      |  |

# Electrical Characteristics at Ta = -30 to $+70^{\circ}C$ , $V_{SS} = 0$ V, $V_{DD} = 3.0$ to 5.5 V unless otherwise specified

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Parameter                     | Symbol               | Conditions                                                                                               | min                      | typ                 | max                 | Unit | Note |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|----------------------------------------------------------------------------------------------------------|--------------------------|---------------------|---------------------|------|------|

| Input high level current   Input low level voltage   P2, P3 (except for the P33/HOLD pin), P6, P8, P9, VDD - PC: Obt = Input low level voltage   P0, P1, P4, P5, P7, PA, PB: IoH = ≠50 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               | I <sub>IH</sub> (1)  |                                                                                                          |                          |                     | 5.0                 | μA   | 1    |

| Input low level current   Input some property   Input some prope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Input high level current      | I <sub>IH</sub> (2)  | (except for PD, PE, PC2 and PC3):  V <sub>IN</sub> = V <sub>DD</sub> , N-channel output, transistor off  |                          |                     | 1.0                 | μA   | 1    |

| Input low level current    II_L (1)   V_{IN} = V_{SS}, N-charinel output, transistor off   -1.0   µA   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               | I <sub>IH</sub> (3)  | N-channel output, transistor off                                                                         | μΑ                       | 1                   |                     |      |      |

| II   L   C   PC2, PC3, PD, PE: VIN = VSS, N-channel output, transistor off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Input low lovel current       | I <sub>IL</sub> (1)  | Inputs other than PD, PE, PC2, PC3: V <sub>IN</sub> = V <sub>SS</sub> , N-channel output, transistor off | -1.0                     |                     |                     | μΑ   | 2    |

| VoH (1)   PC: I <sub>OH</sub> = -1 mA   P2; P3 (except for the P33/HOLD pin), P6, P8, P9, VoD - 0.5   VoH (2)   P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -50 μA   VoD - 1.0   VoH (2)   P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -30 μA   VoD - 0.5   VoH (2)   P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -30 μA   VoD - 0.5   VoH (2)   P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -30 μA   VoD - 0.5   VoH (2)   P0, P1, P2, P3, P4, P5, P6, P8, P9, PC   (except for the P33/HOLD pin): I <sub>OL</sub> = 1.6 mA   VoH (2)   P7, PA, PB: I <sub>OL</sub> = 8 mA   VoH (2)   P7, PA, PB: I <sub>OL</sub> = 8 mA   VoH (2)   P7, PA, PB: I <sub>OL</sub> = 8 mA   VoH (2)   P2, P3, P6, P7, PA; Vi <sub>N</sub> = 13.5 V   Soh (except for P2, P3, P6, P7, P8 and PA): Vi <sub>N</sub> = V <sub>DD</sub>   1.0 μA   6   I <sub>OFF</sub> (2)   (except for P2, P3, P6, P7, P8 and PA): Vi <sub>N</sub> = V <sub>DD</sub>   1.0 μA   6   I <sub>OFF</sub> (2)   P01, P02, P03: Vi <sub>N</sub> = V <sub>SS</sub> to V <sub>DD</sub> - 1.5 V   ±50   ±300   mV   V <sub>OFF</sub> (2)   P01, P02, P03: Vi <sub>N</sub> = 1.5 V to V <sub>DD</sub>   ±50   ±300   mV   V <sub>OFF</sub> (2)   P09: Vi <sub>N</sub> = 1.5 V to V <sub>DD</sub>   0.5 V <sub>DD</sub>   0.5 V <sub>DD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub>   V   I <sub>O</sub> = V <sub>OD</sub>   I <sub>O</sub> = V <sub>OD</sub> | Imput low level current       | I <sub>IL</sub> (2)  |                                                                                                          | -1.0                     |                     |                     | μA   | 2    |

| Output high level voltage  Output high level voltage  P2, P8 (except for the P33/HOLD pin), P6, P8, P9, O.5  PC' I <sub>OH</sub> = -0.1 mA  P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -50 μA  V <sub>OH</sub> (2)  P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -30 μA  Output pull-up current  I <sub>PO</sub> P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -30 μA  V <sub>DD</sub> - 0.5  Output low level voltage  Vol. (1) P0, P1, P4, P5, P7, PA, PB: V <sub>IN</sub> = V <sub>SS</sub> , V <sub>DD</sub> = 5.5 V -1.6  mA 4  P0, P1, P2, P3, P4, P5, P6, P8, P9, PC (except for the P33/HOLD pin): I <sub>OL</sub> = 1.6 mA  Vol. (2) P7, PA, PB: I <sub>OL</sub> = 8 mA  I <sub>OF</sub> (1) P2, P3, P6, P7, P8 and PA): V <sub>IN</sub> = 13.5 V  I <sub>OF</sub> (2) I <sub>OF</sub> (3) P8: V <sub>IN</sub> = V <sub>SS</sub> -1.0  I <sub>OF</sub> (3) P8: V <sub>IN</sub> = V <sub>SS</sub> -1.0  I <sub>OF</sub> (3) P0, P1, P2, P3, P6, P7, P8 and PA): V <sub>IN</sub> = V <sub>DD</sub> -1.0  I <sub>OF</sub> (3) P8: V <sub>IN</sub> = V <sub>SS</sub> -1.0  I <sub>OF</sub> (4) PD1, PD2, PD3: V <sub>IN</sub> = V <sub>SS</sub> -1.0  I <sub>OF</sub> (2) PD0; V <sub>IN</sub> = 1.5 V to V <sub>DD</sub> -1.5 V -1.6  I <sub>OF</sub> (3) P3: V <sub>IN</sub> = V <sub>SS</sub> -1.0  I <sub>OF</sub> (2) PD0; V <sub>IN</sub> = 1.5 V to V <sub>DD</sub> -1.5 V -1.0  I <sub>O</sub> (1) V <sub>OF</sub> (2) P2, P3, RES, P6, P9, OSC1, (RC, EXT) -1.0  I <sub>O</sub> (1) V <sub>O</sub> (2) P2, P3, RES, P6, P9, OSC1, (RC, EXT) -1.0 I <sub>O</sub> (1) V <sub>O</sub> (2) P2, P3, RES, P6, P9, OSC1, (RC, EXT) -1.0 I <sub>O</sub> (1) V <sub>O</sub> (2) P3 (1) V <sub>O</sub> (3) P3 (1) V <sub>O</sub> (4) V <sub>O</sub> (5) V <sub>O</sub> (6) P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -30 μA V <sub>O</sub> (7) V <sub>O</sub> (8) V <sub>O</sub> (8) V <sub>O</sub> (9) V                                                                                                                                                                                                      |                               | \/ (1)               |                                                                                                          | V <sub>DD</sub> –<br>1.0 |                     |                     | V    | 3    |

| P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -50 μA   V <sub>DD</sub> - 1.0   V   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Output high level valtege     | VOH (1)              |                                                                                                          |                          |                     |                     | V    | 3    |

| Output pull-up current   Ipo   P0, P1, P4, P5, P7, PA, PB: IoH = -30 μA   VDD = 0.5   V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output high level voltage     | V (2)                |                                                                                                          | V <sub>DD</sub> –<br>1.0 |                     |                     | W    | 4    |

| Output low level voltage         V <sub>OL</sub> (1)         P0, P1, P2, P3, P4, P5, P6, P8, P9, PC (except for the P33/HOLD pin): I <sub>OL</sub> = 1.6 mA         0.4         V         5           Output low level voltage         V <sub>OL</sub> (2)         P7, PA, PB: I <sub>OL</sub> = 8 mA         1.5         V           Output off leakage current         I <sub>OFF</sub> (1)         P2, P3, P6, P7, P8: V <sub>IN</sub> = 13.5 V         5.0         μA         6           Output off leakage current         I <sub>OFF</sub> (2)         P2, P3, P6, P7, P8: V <sub>IN</sub> = 13.5 V         5.0         μA         6           Comparator offset voltage         V <sub>IN</sub> = V <sub>SS</sub> O V <sub>DD</sub> - 1.5 V         ±50         ±300         mV           Comparator offset voltage         V <sub>IN</sub> = V <sub>SS</sub> to V <sub>DD</sub> - 1.5 V         ±50         ±300         mV           Estimate of the position of the po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               | VOH (2)              | P0, P1, P4, P5, P7, PA, PB: I <sub>OH</sub> = -30 μA                                                     | V <sub>DD</sub> –<br>0.5 |                     |                     | V    | 7    |

| Output low level voltage         VOL (1) (except for the P33/HOLD pin): I <sub>OL</sub> = 1.6 mA         0.4 V         5           VOL (2) P7, PA, PB: I <sub>OL</sub> = 8 mA         1.5 V           Output off leakage current         I <sub>OFF</sub> (1) P2, P3, P6, P7, PA: V <sub>IN</sub> = 13.5 V         5.0 μA         6           Output off leakage current         I <sub>OFF</sub> (2) (except for P2, P3, P6, P7, P8 and PA): V <sub>IN</sub> = V <sub>DD</sub> 1.0 μA         6           I <sub>OFF</sub> (3) P8: V <sub>IN</sub> = V <sub>SS</sub> -1.0         μA         7           Comparator offset voltage         V <sub>OFF</sub> (1) PD1, PD2, PD3: V <sub>IN</sub> = V <sub>SS</sub> to V <sub>DD</sub> - 1.5 V         ±50 ±300 mV           [Schmitt characteristics]         Hysteresis voltage         V <sub>HIS</sub> V <sub>I</sub> P2, P3, RES, P6, P9, OSC1, (RC, EXT)         0.5 V <sub>DD</sub> 0.8 V <sub>DD</sub> V           Low level threshold voltage         V <sub>I</sub> H         P2, P3, RES, P6, P9, OSC1, (RC, EXT)         0.5 V <sub>DD</sub> 0.5 V <sub>DD</sub> V           [Ceramic oscillator]         J <sub>CF</sub> OSC1, OSC2: See Figure 2, 4 MHz         4.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Output pull-up current        | l <sub>PO</sub>      | P0, P1, P4, P5, P7, PA, PB: V <sub>IN</sub> = V <sub>SS</sub> , V <sub>DD</sub> = 5.5 V                  | -1.6                     |                     |                     | mA   | 4    |

| Vol (2)   P7, PA, PB: I <sub>OL</sub> = 8 mA   1.5   V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Output low level voltage      | V <sub>OL</sub> (1)  |                                                                                                          |                          |                     | 0.4                 | ٧    | 5    |