PLL-SPLIT VIF/SIF

#### DESCRIPTION

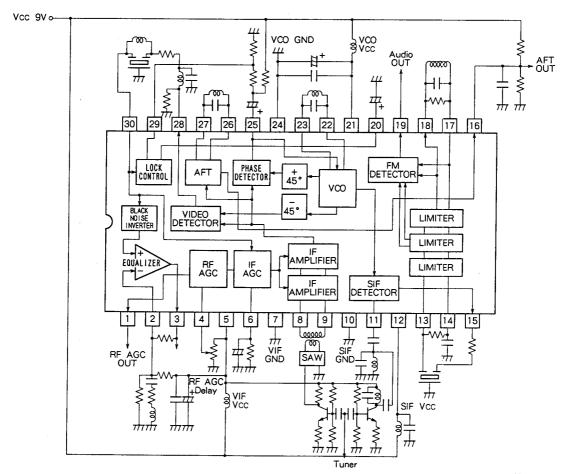

The M51362SP is a semiconductor IC consisting of IF signal processor suitable for color TV sets and VCRs with AV which is a revision of M51365SP.

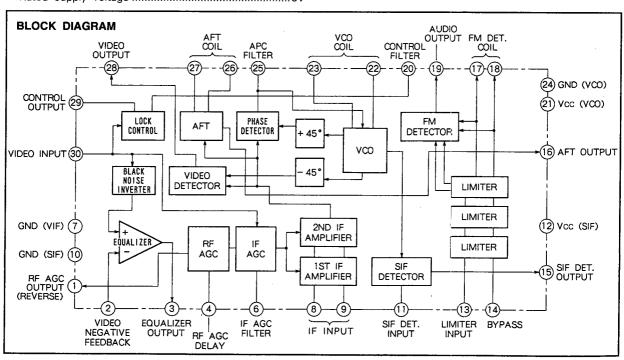

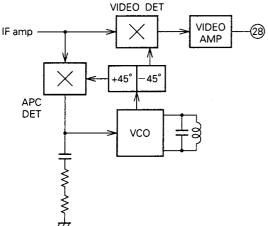

The circuit includes VIF amplifier, Video detector, VCO, APC detector, AFT, video equalizer, IF/RF AGC, SIF detector, SIF limiter, FM detector functions.

### **FEATURES**

- A full synchronous detector circuit using PLL as video detector provides excellent DG, DP, 920kHz beat and cross color characteristics.

- The PLL-SPLIT method in which video IF and audio IF signal processings are separated and VCO output is used to obtain intercarrier provides good sound sensitivity and reduces buzz. In consumer sets, intercarrier is also available from the video detector output.

- Built-in video equalizer is suitable for VCRs and color TV sets equipped with video output terminals.

- The quadrature detector circuit for FM detector has good linearity with a simple coil.

- The M51362SP has better video S/N ratio than M51365SP by 2~4dB.

### **APPLICATIONS**

TV sets, VCR tuners

### RECOMMENDED OPERATING CONDITIONS

#### PIN CONFIGURATION (TOP VIEW) RF AGC OUTPUT (REVERSE) 1 VIDEO INPUT VIDEO NEGATIVE FEEDBACK CONTROL OUTPUT **EQUALIZER OUTPUT** VIDEO OUTPUT RF AGC DELAY AFT COIL Vcc (VIF) IF AGC FILTER APC FILTER M51362SF GND (VIF) 团 GND (VCO) 24 8 IF INPUT VCO COIL GND (SIF) Vcc (VC0) SIF det. INPUT CONTROL FILTER Vcc (SIF) AUDIO OUTPUT LIMITER INPUT FM det. COIL 14 **BYPASS** SIF det. OUTPUT AFT OUTPUT Outline 30P4B

### PLL-SPLIT VIF/SIF

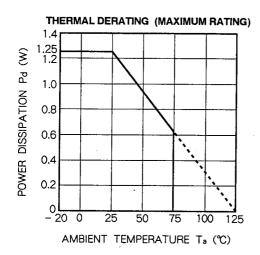

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter             | Ratings  | Unit |

|--------|-----------------------|----------|------|

| Vcc    | Supply voltage        | 14       | V    |

| Pd     | Power dissipation     | 1250     | mW   |

| Topr   | Operating temperature | - 20~75  | ొ    |

| Tstg   | Storage temperature   | - 40~125 | ొ    |

# **ELECTRICAL CHARACTERISTICS** (Ta = $25 \, ^{\circ}$ C, Vcc = 9V unless otherwise noted) VIF SECTION

|                    |                                       |      | Test       | Test conditions |        |      |                      |              |                             |                    |        | Limits |        |                   |  |

|--------------------|---------------------------------------|------|------------|-----------------|--------|------|----------------------|--------------|-----------------------------|--------------------|--------|--------|--------|-------------------|--|

| Symbol             | Parameter                             | cir  | 1031       |                 | signal | Exte | ernal po<br>supply ( | wer<br>/)    | * Switches should           | C.                 | Min.   | Typ.   | Max.   | Unit              |  |

|                    | •                                     | cuit | point      | VIF             | SIF1   | V1   | V <sub>6</sub>       | V20          | usually be set              | to 1.              | IVIII. | Typ.   | IVIAX. |                   |  |

| Icc (VIF)          | Circuit current (VIF)                 | 1    | A1         | -               | _      | 3    | -                    | -            | SW1 = 2                     |                    | 33     | 45     | 57     | mA                |  |

| V <sub>28</sub>    | Video detector output<br>DC voltage 1 | 1    | TP9        | _               | _      | 3    | 0                    | -            | SW3 = 2                     |                    | 3.4    | 3.75   | 4.1    | ٧                 |  |

| Vз                 | Video detector output<br>DC voltage 2 | 1    | TP2        | _               | _      | 3    | 0                    | _            | SW3 = 2                     |                    | 4.4    | 4.8    | 5.2    | ٧                 |  |

| VO det1            | Video detector output 1               | 1    | TP9        | SG1             |        | 3    | <u> </u>             | _            |                             |                    | 1.15   | 1.45   | 1.75   | VP-P              |  |

| VO det2            | Video detector output 2               | 1    | TP2        | SG1             |        | 3    | -                    | -            |                             |                    | 1.6    | 1.95   | 2.3    | V <sub>P</sub> -P |  |

| P/N                | Video S/N                             | 1    | TP10       | SG6             | _      | 3    |                      | _            | SW6 = 2                     | (note 1)           | 44     | 52     |        | dB                |  |

| Bw                 | Video frequency characteristics       | 1    | TP9        | SG3             | _      | თ    | _                    | -            | (                           | note 2)            | 5.5    | 7.5    |        | MHz               |  |

| Vin (min)          | Input sensitivity                     | 1    | TP9        | SG4             | -      | ო    | -                    | -            | (                           | (note 3)           |        | 46     | 51     | dΒμ               |  |

| Vin (max)          | Maximum allowable input               | 1    | TP9        | SG5             | -      | 3    | -                    | -            | (                           | note 4)            | 107    | 110    |        | dΒμ               |  |

| GR                 | AGC control range                     | 1    | _          | _               | -      | _    | -                    | _            | (                           | note 5)            | 58     | 64     |        | dB                |  |

| VIH                | IF AGC maximum voltage                | 1    | TP3        | _               | _      | 3    | -                    | _            |                             |                    | 6.5    | 8.6    |        | V                 |  |

| Vi (80dBµ)         | IF AGC (80dB μ)                       | 1    | TP3        | SG6             | _      | 3    | _                    | _            |                             |                    | 4.3    | 4.9    | 5.5    | V                 |  |

| VIL                | IF AGC minimum voltage                | 1    | TP3        | SG7             | _      | 3    | _                    | _            |                             |                    | 3.4    | 3.9    | 4.4    | V                 |  |

| Vo siF-1           | SIF det.<br>4.5MHz output(100dBµ)     | 1    | TP4        | SG2             | SG8    | 3    | -                    | -            |                             | ·                  | 104    | 109    | 114    | dB μ              |  |

| Vo siF-2           | SIF det.<br>4.5MHz output(80dB µ)     | 1    | TP4        | SG2             | SG9    | 3    | _                    | -            |                             |                    | 90     | 96     | 101    | dB μ              |  |

| V16                | AFT output voltage                    | 1    | TP5        | _               | -      | 3    | 0                    | -            |                             |                    | 3.2    | 4.3    | 5.4    | V                 |  |

| μ .                | AFT detector sensitivity              | 1    | TP5        | SG10            | -      | 3    | _                    | - T          | (                           | note 6)            | 48     | 70     | 92     | mV/kHz            |  |

| V16H               | AFT maximum voltage                   | 1    | TP5        | SG10            | -      | 3    | _                    | -            | (                           | note 7)            | 8      | 8.7    |        | V                 |  |

| V <sub>16L</sub>   | AFT minimum voltage                   | 1    | TP5        | SG10            | _      | 3    | -                    | _            | (                           | note 8)            | -      | 0.38   | 1.0    | V                 |  |

| V <sub>1</sub> H   | RF AGC maximum voltage                | 1    | TP1        | SG2             | _      | 2    | -                    | -            |                             |                    | 7      | 7.85   |        | V                 |  |

| V1L                | RF AGC minimum voltage                | 1    | TP1        | SG2             |        | 4    |                      | _            |                             |                    |        | 0      | 1.0    | V                 |  |

| CL-U1              | Capture range (U)                     | 1    | TP9        | SG11            |        | 3    | -                    | -            | (                           | note 9)            | 0.45   | 0.8    |        | MHz               |  |

| CL-L1              | Capture range (L)                     | 1    | TP9        | SG11            | -      | 3    |                      | _            | (n                          | ote 10)            | 1.4    | 2.0    |        | MHz               |  |

| CL-T               | Capture range (T)                     | 1    | _          |                 |        |      | _                    | _            | (n                          | ote 11)            | 2.0    | 2.8    |        | MHz               |  |

| CL-U2              | Capture range (U)                     | 1    | TP9        | SG11            | _      | 3    |                      | _            | SW5 = 2                     | note 9)            | 0.45   | 0.8    | 1.2    | MHz               |  |

| CL-L2              | Capture range (L)                     | 1    | TP9        | SG11            | _      | 3    | _                    | -            |                             | ote 10)            | 1.0    | 1.6    | 2.2    | MHz               |  |

| V <sub>20</sub> TH | Lock detector threshold voltage       | 1    | TP8        | _               |        | 3    | 5                    | Vari<br>able |                             | ote 12)            | 3.6    | 4.0    | 4.4    | V                 |  |

| V <sub>29L</sub>   | Minimum voltage at pin @              | ·    | TP8        |                 | _      | 3    | 5                    | Vari<br>able |                             | ote 13)            | 0.0    | 0.05   | 0.5    | v                 |  |

| FC1                | EQ frequency characteristics 1        | 1    | TP9<br>TP2 | SG12            | -      | 3    | -                    | - abie       | Re                          | efer to<br>ote 14) | 1.4    | 2.4    | 3.4    | dВ                |  |

| FC2                | EQ frequency characteristics 2        | 1    | TP9<br>TP2 | SG13            |        | 3    | -                    | -            |                             | efer to<br>ote 14) | 4.2    | 5.7    | 7.2    | dB                |  |

| FC3                | EQ frequency characteristics 3        | 1    | TP9<br>TP2 | SG14            | -      | 3    | -                    | -            |                             | efer to<br>ote 14) | 9.5    | 12.0   | 14.5   | dB                |  |

| IM                 | Intermodulation                       | 1    | ТР9        | SG15            | -      | 3    | Vari<br>able         | -            | $\nabla W \cdot \nabla = V$ | efer to<br>ote 15) | 34     | 39     |        | ďΒ                |  |

| DG                 | DG                                    | 1    |            | SG16            | -      | 3    | -                    |              | (no                         | ote 16)            |        | 2      | 5      | %                 |  |

| DP                 | DP                                    | 1    | TP9        | SG16            | -      | 3    | _                    | -            | (no                         | ote 16)            |        | 2      | 5      | deg.              |  |

### VIF SECTION (cont.)

|                  |                                     | Tes  | Test  |        |        |    | Te                    | st co       | nditions  |           |    |         | Limits | mits   |      |  |  |

|------------------|-------------------------------------|------|-------|--------|--------|----|-----------------------|-------------|-----------|-----------|----|---------|--------|--------|------|--|--|

| Symbol           | Parameter                           | cir  | 1     | Input  | signal | Ex | ternal po<br>supply(V | we <i>r</i> | * Switche | es should |    | Min.    | Тур.   | Max.   | Unit |  |  |

|                  |                                     | cuit | point | VIF    | SIF1   | V١ | V <sub>6</sub>        | V20         | usually   | be set to | 1. | IVIII). | Typ.   | iviax. |      |  |  |

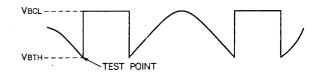

| Vвтн             | Black spot inverter threshold level | 1    | TP2   | SG1    | -      | 3  | Vari<br>able          | _           | SW3 = 2   | (note 17  | )  | 1.3     | 1.7    | 2.1    | ٧    |  |  |

| V <sub>BCL</sub> | Black spot inverter clamp level     | 1    | TP2   | SG1    | _      | 3  | Vari<br>able          | _           | SW3 = 2   | (note 17  | ') | 3.7     | 4.2    | 4.7    | ٧    |  |  |

| Vsync            | Sync tip level at pin 3             | 1    | TP2   | SG2    |        | 3  | -                     | -           |           |           |    | 2.1     | 2.5    | 2.9    | V    |  |  |

| Rin (V)          | VIF input resistance                | 2    |       | 90dB µ | -      | 3  | -                     | -           |           |           |    |         | 0.9    |        | kΩ   |  |  |

| Cin (V)          | VIF input capacitance               | 2    |       | 90dB µ | -      | 3  | -                     | _           |           |           |    |         | 6.6    |        | pF   |  |  |

| Rin (S1)         | SIF1 input resistance               | 2    |       |        | 90dB µ | 3  | -                     | -           |           |           |    |         | 2.1    |        | kΩ   |  |  |

| Cin (S1)         | SIF1 input capacitance              | 2    |       | _      | 90dB µ | 3  | -                     | -           |           |           |    |         | 2.5    |        | ρF   |  |  |

### SIF SECTION

|           |                            | Tes               | Test | Ĺ             |        |           | Te                   | st co           | onditions                              |      | Limits |      |       |

|-----------|----------------------------|-------------------|------|---------------|--------|-----------|----------------------|-----------------|----------------------------------------|------|--------|------|-------|

| Symbol    | l Parameter                | neter cir<br>cuit |      | Input<br>SIF2 | signal | Ext<br>Vi | ernal po<br>upply (1 | V <sub>20</sub> | * Switches should usually be set to 1. | Min. | Тур.   | Max. | Unit  |

| lcc (SIF) | Circuit current (SIF)      | 1                 | A2   | -             |        | 0         | -                    | -               | SW2 = 2                                | 6.1  | 8.7    | 11.4 | mA    |

| V19       | AF output DC voltage       | 1                 | TP6  |               |        | 0         | _                    | -               |                                        | 4.1  | 4.9    | 5.7  | V     |

| VOAFMAX   | Maximum AF output          | 1                 | TP6  | SG17          |        | 0         | _                    | _               |                                        | 225  | 300    | 375  | mVrms |

| THDAF     | AF output distortion       | 1                 | TP6  | SG21          |        | 0         | _                    | _               |                                        |      | 0.2    | 1.0  | %     |

| Vin (lim) | Input limiting sensitivity | 1                 | TP6  | SG18          |        | 0         | -                    |                 | (note 13)                              |      | 34     | 42   | dB u  |

| AMR       | AMR                        | 1                 | TP6  | SG19          |        | 0         | _                    | -               | (note 19)                              | 58   | 68     |      | dB    |

| S/N       | AF S/N                     | 1                 | TP6  | SG20          |        | 0         |                      | -               | (note 20)                              | 58   | 73     |      | dB    |

# **ELECTRICAL CHARACTERISTICS TEST METHOD** Note1. Video S/N "P/N"

- a. Input SG6 in VIF IN.

- b. The noise appearing at pin @ is determined by measuring the r.m.s. voltage at TP10 through low pass filter (-3dB at 5MHz).

c. P/N = 20 log

$$\left\{ \frac{\text{Vodet 1 (VP-P) x 0.7}}{\text{noise (Vrms)}} \right\}$$

,

where Vodet 1 denotes video detector output 1.

# Note2. Video frequency characteristics "Bw"

a. Set SG3 as follows:

$$\begin{array}{lll} f_1 = 58.75 MHz \ ' \ V_i = 90 dB \mu \\ f_2 = 57.75 MHz \ \ V_i = 70 dB \mu \end{array} \right\} \ mixed \ signal$$

- b. Measure the element of 1MHz at TP9 and the result is defined as V1.

- c. Decrease the frequency until element (f1-f2) at TP9 reaches 3dB less than V1. Then, read the frequency.

- $d.Bw = 58.75 f_2 (MHz)$

### Note3. Input sensitivity "Vin (min)"

- a. Input SG4 in VIF IN.

- b. Decrease the SG4 level and the level at which detector output at pin 2 reaches 3dB less than Vodet 1 is defined as input sensitivity.

### Note4. Maximum allowable input "Vin (max)"

- a. Set SG5 to 90dBµ and input it in VIF IN.

- b. Detector output at pin 29 at this time is defined as

- c. Increase the voltage of SG5 and voltage at which detector output reaches 3dB less than V2 is defined as maximum allowable input.

### Note5 AGC control range "GR"

- a. AGC control range is defined as follows:

- GR = Maximum allowable input Input sensitivity

# Note6 AFT detector sensitivity " $\mu$ "

a. Input SG10 in VIF IN.

$\mu = \frac{3000\text{mV}}{\text{(mV/kHz)}}$

- b. Measure difference of frequency between 3.0V and 6.0V of DC voltage at TP5 and the difference is defined as Δf.

- c. AFT detector sensitivity  $\boldsymbol{\mu}$  is defined as follows:

58.75MHz

f (MHz)

## PLL-SPLIT VIF/SIF

# Note7. AFT maximum voltage "V16H"

a. Maximum DC voltage in the figure on the previous page is defined as V<sub>16H</sub>.

# Note8. AFT minimum voltage "V16L"

b. Minimum DC voltage in the figure on the previous page is defined as V<sub>16</sub>L.

### Note9. Capture range (U) "CL-U-1," "CL-U-2"

- a. Input SG11 in VIF IN and increase the frequency till VCO lock is released.

- b. Decrease the frequency of SG11 and the frequency at which VCO locks again is defined as fv (MHz).

- c. Capture range (U) is defined as fv 58.75 (MHz).

# Note10. Capture range (L) "CL-L-1," "CL-L-2"

- a Input SG11 in VIF IN and decrease the frequency till VCO lock is released.

- b. Increase the frequency of SG11 and the frequency at which VCO locks again is defined as ft (MHz).

- c. Capture range (L) is defined as 58.75 ft (MHz).

### Note11. Capture range (T) "CT-T"

a. "CL-T" is defined as "CL-U-1" + "CL-L-1" (MHz).

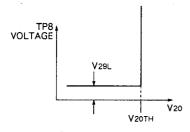

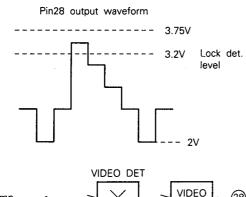

### Note12. Lock detector threshold voltage "V20TH"

- a Set the voltage at V20 to 3V and observe TP8.

- b. Increase the voltage at V<sub>20</sub> and the point at which TP8 voltage changes drastically is defined as V<sub>20ТН</sub> (threshold 1V).

### Note13. Minimum voltage at pin @ "V29L"

a. Minimum voltage in Note12 is defined as V<sub>29</sub>L.

# Note14. EQ frequency characteristics "FC1" "FC2" "FC3"

- a. Input SG12, SG13 or SG14 to VIF IN.

- b.Measure the level of element (f1-f2) at TP9 and it is defined as VEO IN (dB $\mu$ ).

- c. Measure the level of element ( $f_1$ - $f_2$ ) at TP2 and it is defined as VEQ OUT (dB $\mu$ ).

- d.EQ frequency characteristics is defined as follows: FC1~3 = VEQ OUT - VEQ IN (dB)

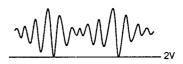

### Note15. Intermodulation "IM"

- a. Input SG15 in VIF IN.

- b. Observe TP9 with oscilloscope, and adjust the voltage of V<sub>6</sub> so that the minimum level of detector output waveform will come to 2V.

c. Observe TP9 with spectrum analyzer at this time, and the ratio of the 920kHz level to the 3.58MHz level is defined as intermodulation.

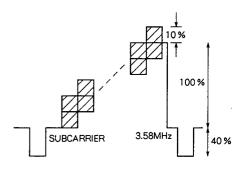

### Note16.DG, DP "DG, DP"

- a. Modulated waves of SG16 is generated by 87.5% video modulation of the 10-step waves as shown in the figure below.

- b. Measure DG and DP at TP9 with vectorscope.

# Note17. Black spot inverter threshold level, clamp level "VB TH, VB CL"

- a. Input SG1 in VIF IN.

- b. By varying V<sub>6</sub>, output the waveform as shown in the figure below to TP2 and measure each DC voltage.

### Note18 Input limiting sensitivity "Vin (lim)"

- a. Set SG18 to 80dBµ and input it in SIF2 IN.

- b. Decrease the output level of SG18 until detector output at TP6 becomes 3dB smaller than Vo AF MAX.

The level of SG18 at this time is input limiting sensitivity.

## Note19. AMR "AMR"

- a. Input SG19 in SIF2 IN.

- b. Measure the output voltage at TP6 and it is defined as VAM.

- c. AMR is defined as follows:

$$AMR = 20 \log \left\{ \frac{Vo \text{ AF MAX (mVrms)}}{V_{AM} \text{ (mVrms)}} \right\} (dB)$$

# PLL-SPLIT VIF/SIF

# Note20. AF S/N "S/N"

- a. Input SG20 in SIF2 IN.

- b. Measure the output voltage at TP6 and it is defined as  $\mbox{Vn}$ .

- c. AF S/N is defined as follows:

$$S/N = 20 log \left\{ \frac{Vo AF MAX (mVrms)}{VN (mVrms)} \right\} (dB)$$

- \* Amplitude level of all AM modulated waves are the peak level of modulated waves.

- The following is used for the mixer:

• With Vco coil, IF AGC 0V and non-input condition, adjust free run frequency to 58.75MHz.

# **INPUT SIGNAL**

|        | Particular                                                                                                                                                                                                                                              |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SG No. |                                                                                                                                                                                                                                                         |

| SG1    | fo=58.75MHz Vi=90dB $\mu$ 77.78%AM (Corresponding to 87.5%)                                                                                                                                                                                             |

| SG2    | fo = 58.75MHz Vi = 90dB μ                                                                                                                                                                                                                               |

| SG3    | $ \begin{array}{l} f_1 = 58.75 \text{MHz} \ \ \text{V}_i = 90 \text{dB} \ \mu \\ f_2 = 53 \pm 5 \text{MHz} \ \ \text{V}_i = 70 \text{dB} \ \mu \end{array} \right\} \ \text{mixed signal} $                                                             |

| SG4    | fo = 58.75MHz Vi = Vaviable fm = 20kHz 77.78% AM                                                                                                                                                                                                        |

| SG5    | fo = 58.75MHz Vi = Vaviable fm = 20kHz 16 % AM                                                                                                                                                                                                          |

| SG6    | fo = 58.75MHz Vi = 80dB μ                                                                                                                                                                                                                               |

| SG7    | $f_0 = 58.75MHz \ V_i = 110dB \ \mu$                                                                                                                                                                                                                    |

| SG8    | fo = 54.25MHz V <sub>i</sub> = 100dB μ                                                                                                                                                                                                                  |

| SG9    | $f_0 = 54.25MHz \ V_i = 80dB \mu$                                                                                                                                                                                                                       |

| SG10   | fo = $58.75MHz \pm 5MHz V_i = 90dB \mu$                                                                                                                                                                                                                 |

| SG11   | fo=58.75MHz ± 5MHz Vi=90dB µ fm=20kHz 77.78%AM                                                                                                                                                                                                          |

| SG12   | $ \begin{array}{l} f_1 = 58.75 \text{MHz}  V_i = 90 \text{dB} \; \mu \\ f_2 = 58.25 \text{MHz}  V_i = 60 \text{dB} \; \mu \end{array} \; \right\} \; \text{mixed signal} $                                                                              |

| SG13   | $\begin{array}{l} f_1 = 58.75 \text{MHz} \ \ \text{Vi} = 90 \text{dB} \ \mu \\ f_2 = 55.75 \text{MHz} \ \ \text{Vi} = 60 \text{dB} \ \mu \end{array} \right\} \ \text{mixed signal} \label{eq:f1}$                                                      |

| SG14   | $\begin{array}{l} f_1 = 58.75 \text{MHz} \ \ \text{Vi} = 90 \text{dB} \ \mu \\ f_2 = 54.75 \text{MHz} \ \ \text{Vi} = 60 \text{dB} \ \mu \end{array} \right\} \ \text{mixed signal} \end{array}$                                                        |

| SG15   | $\left.\begin{array}{l} f_1 = 58.75 \text{MHz} \ \ \text{Vi} = 90 \text{dB} \ \mu \\ f_2 = 55.17 \text{MHz} \ \ \text{Vi} = 80 \text{dB} \ \mu \\ f_3 = 54.25 \text{MHz} \ \ \text{Vi} = 80 \text{dB} \ \mu \\ \end{array}\right\} \text{mixed signal}$ |

| SG16   | $f_0 = 58.75 MHz$ standard $10 - step$ modulation $m = 87.5 \%$ video modulation, sync tip level $90dB \mu$                                                                                                                                             |

| SG17   | $f_0 = 4.5MHz \pm 25kHz$ dev $V_i = 100dB \mu$ $f_m = 400Hz$                                                                                                                                                                                            |

| SG18   | $f_0 = 4.5MHz \pm 25kHZ$ dev $V_i = Vaviable$ $f_m = 400Hz$                                                                                                                                                                                             |

| SG19   | $f_0 = 4.5MHz$ $V_i = 100dB \mu 30 \% AM$ $f_m = 400Hz$                                                                                                                                                                                                 |

| SG20   | $f_0 = 4.5 MHz \ V_i = 100 dB \mu$                                                                                                                                                                                                                      |

| SG21   | $f_0 = 4.5MHz \ V_i = 100dB\mu \ f_m = 400Hz \pm 7.5kHz \ dev$                                                                                                                                                                                          |

| ·      |                                                                                                                                                                                                                                                         |

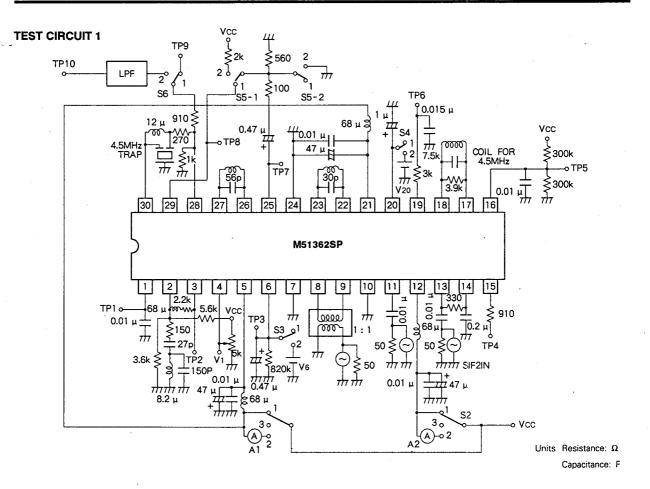

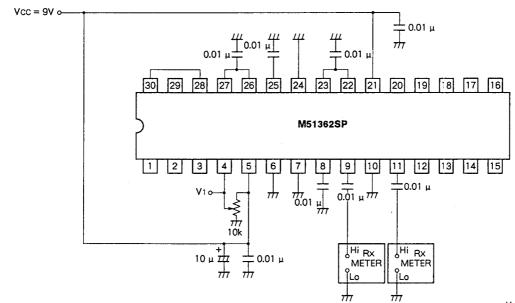

### PLL-SPLIT VIF/SIF

### **TEST CIRCUIT 2**

Units Resistance:  $\Omega$

Capacitance: F

### **TYPICAL CHARACTERISTICS**

## **APPLICATION EXAMPLE**

Units Resistance:  $\Omega$

Capacitance: F

# PLL-SPLIT VIF/SIF

## PRECAUTIONS FOR APPLICATION

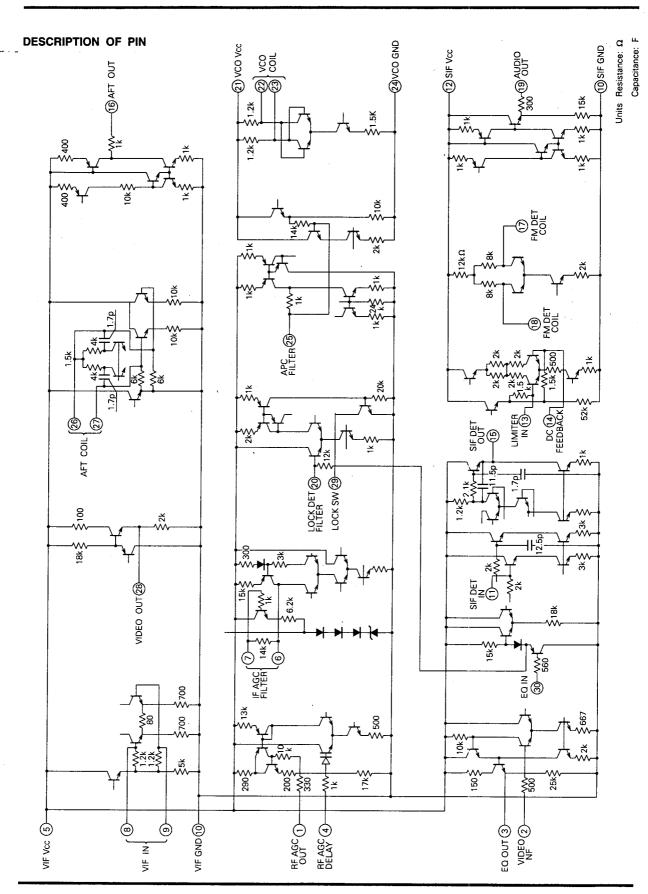

### 1.VIF Amplifier

The VIF amplifier is a two-stage amplifier without DC feedback.

With a gain of approx. 40dB, the VIF amplifier is connected to a video detector via an internal capacitor.

Maximum input amplitude is determined by the input dynamic range of the VIF amplifier, allowing up to  $110dB\mu$  input. During excessive input, surpassing this limit will cause the linearity to worsen, while leaving amplitude unchanged. Since gain control has the characteristic that AGC speed is fastest in the range  $50{\sim}60dB\mu$ , to prevent sag, select an appropriate filter time constant.

IF input impedance is approx. 1K  $\!\Omega\!$  and must be input in balanced type.

### 2. Video Detector, PLL Section

The PLL system produces a pure carrier wave. The PLL is locked as shown in the diagram below.

The VIDEO DET and APC DET employ a double balanced mixer.

Detector output (pin 3) is 1.5VP-P (Vcc = 9V, negative sync). Detector output is almost proportional to supply voltage. Pin 3 is an emitter follower, containing a  $2K\Omega$  emitter resistor, and requires an externally attached resistor ( $2K\Omega{\sim}1K\Omega$ ) as it is insufficient alone to drive a 4.5MHz trap.

The lock detector determines locked/unlocked conditions by the average level of detector output.

In pin 29, the threshold is 3.2V.

The time constant switch is pin 3.

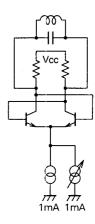

The VCO circuit diagram is shown to the right, and illustrates how sinking current is varied to adjust frequency.

The variable range falls between -1.7MHz and +1.3MHz at a capacity of 27PF (45.75MHz).

The variable range widens as the capacity decreases, while the temperature drift characteristic and harmonics worsen. Vcc and GND of the VCO section are independent of those of the VIF, while the same DC voltage must be supplied as for the VIF.

### 3.SIF Det.

4.5MHz issues from pin (3), however, for M51362SP, inputting 41.25MHz thru pin (1) causes 4.5MHz to be output from pin (5), the product of multiplying 45.75MHz by the carrier wave gained at the VCO.

Since conversion gain is 18dB, which is constant, note that at a lower level than the delay point, the output level is also lowered linearly.

Input impedance is approx.  $2K\Omega$ , output pin 5 is an emitter follower type circuit, current sink is 0.6mA, and a  $300\Omega$  resistor is connected in series.

### 4. AFT

The AFT circuit is of the conventional type. Output is also of the conventional current-drive type.

Since internal operating current is reduced, use a load resistor three times larger than the conventional one. A defeat terminal is not provided here.

Therefore, using the middle point in the coil between pins 3 and 2, lower the voltage of pins 3 and 2 to less than 1V. The internal resistor of pins 3 and 2 is  $6K\Omega$ .

#### 5.IF/RF AGC

The IF AGC amplifier is a two-stage amplifier, with pin **(6)** & pin **(7)** serving as a filter terminal.

Output to pin **(6)** is a current-drive type, and a current sink is 0.5mA.

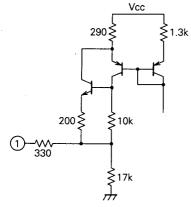

The RF AGC is a reverse output type; its pin ① output is illustrated in the figure to the right.

Output voltage is (7.8V~0V) at Vcc = 9V.

Black spot inverter works before EQ amp. Voltage lower than sync chip by 0.45V (pin 29) is to be threshold.

Clamp voltage is nearly at the white level.

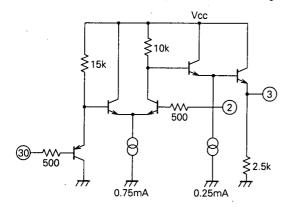

### 6.EQ Amplifier

Basically, the EQ amplifier is as shown in the diagram to the right.

Providing the feedback to pin ②, it has the frequency characteristic.

It can also be used as an amplifier with a fixed gain.

### 7.SIF Section

As Vcc and GND of the SIF section are independent of those of the VIF, the supply voltage of the SIF section can be changed.

The limiter amplifier is a triple amplification device, including an internal differential amplifier. Pin (4) is a DC feedback

terminal.

The resistor between pins (3) and (4) is provided to prevent parasitic oscillation.

The FM detector employs a quadrature detection method and requires a tank coil and damping resistor at pins @ and ...

Note that use of a ceramic discriminator would not obtain a good characteristic.

Pin 9 audio output also employs an emitter follower and the output impedance is approx.  $700\Omega$ .

### Principle of M51362SP PLL Section

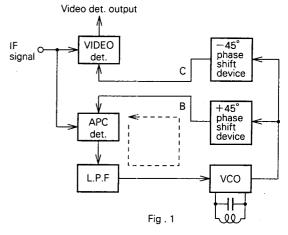

M51362SP's PLL section is formed as shown in Fig. 1. The locked loop is indicated by broken lines.

The APC and video detector are double balance-type multipliers, and the LPF is a lag-lead filter with external C.R.

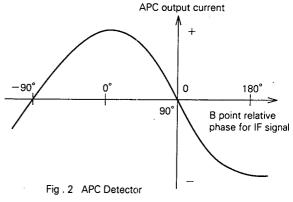

The APC detector is a phase comparator and outputs voltage corresponding to the phase difference between the IF signal and VCO output (output through +45° phase shift device).

The phase comparator usually has such a characteristic as the one illustrated in Fig. 2: When the phase angle of B is +90° out-of-phase for the IF signal, the APC output current becomes 0, while APC output current becomes positive when the phase angle lags.

### PLL-SPLIT VIF/SIF

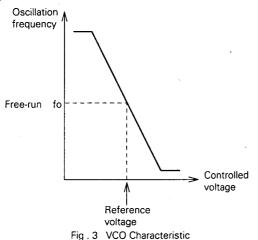

Output current is converted into voltage, and unnecessary frequency is cut off via LPF. Then, the voltage is applied to VCO as controlled voltage. Here, the VCO characteristic is shown in Fig. 3, and for the IF signal, the phase at B relative to the IF signal is -90°.

The procedure by which the VCO follows the IF signal is described below: For example, when the phase of the IF signal lags (the phase at B relative to the IF signal leads more than -90°), APC output current becomes positive, controlled current increases, frequency tends to decrease and, consequently, the phase lags.

So at point B, the VCO locked in phase angle is -90°. Meanwhile, when the frequency of the IF signal becomes high, APC output is negative, controlled voltage decreases, and the VCO frequency becomes higher, because the instantaneous phase is equivalent to leading.

However, with phase error inversely proportional to loop gain, the VCO locks.

Free-run frequency is oscillation frequency produced when center voltage is applied to the VCO.

When locked, the input frequency lock range depends on the variable frequency range, and the lower loop gain narrows this range. Description of the capture procedure for the IF signal is omitted here due to its complexity. The capture range is narrower than that of the lock in relation to loop gain, and narrower than the LPF bandwidth.

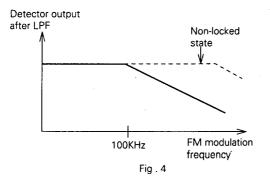

When the M51362SP is in the non-locked state and a locked condition is detected, the LPF time constant is reduced to widen the capture range.

The frequency response characteristic under the locked state is shown in Fig. 4; cut-off frequency is approx. 100KHz, and is equivalent to the bandwidth of the carrier wave reproduced from the IF signal.

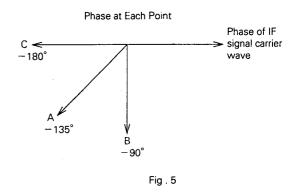

Here, the AM detector section is now described. If, in Fig. 5, the phase at point B is locked at  $-90^{\circ}$ , phase lags by  $45^{\circ}$  at point A, this means the IF signal carrier wave will be  $-135^{\circ}$ .

Consequently, the carrier wave phase at point C, where the signal is input into the video detector, lags by an additional 45°, producing -180° (out-of-phase).

A correct phase produces the most complete and effective demodulation of the video signal. (See Fig. 5).

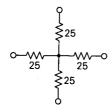

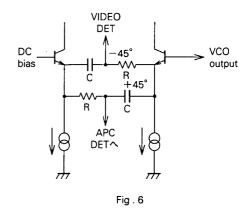

Fig.6 illustrates the basic circuit of the phase shift device. Each phase shift device comprises an LPF ( $-45^{\circ}$ ), an HPF ( $+45^{\circ}$ ) having simple C and R and set so that the phase will rotate by  $\pm 45^{\circ}$  at 45.75 MHz.

Consequently, although the phase rotation varies in the other IF band, the relative phase angle is 90°, independent of frequency, as the values of R and C are set equal to one another.

# PLL-SPLIT VIF/SIF

# SPECIAL PARTS

Coil Specification f = 45.75MHz

1) VCO coil pin 29, 29

Qu Co(pF) Turns Bobbin Wire  $92\pm20\%$  27 (1–6)  $6\frac{1}{2}$ t 10K type 0.12 $\Phi$  OUEW

Variable range widens as Co is reduced.

- 2) AFT coil pin ⊗, Ø

Qu Co(pF) Turns Bobbin Wire

84±20% 59±6% (1–6) 4 1/4 t 10K type 0.12Φ

- SIF coil pin 1 Filter passing only 41.25MHz. Can be used in AFT coil.

When SAW filter (41.25MHz) is used, compensation for loss is necessary.

- 4) SIF FM det. coil pin ⑦, ⑱

Qu Co(pF) Turns Bobbin Wire

60±20% 68pF (4-6) 36t 10K type 0.12Φ

OUEW