# HMCS45A(HD38820,HD38825)-

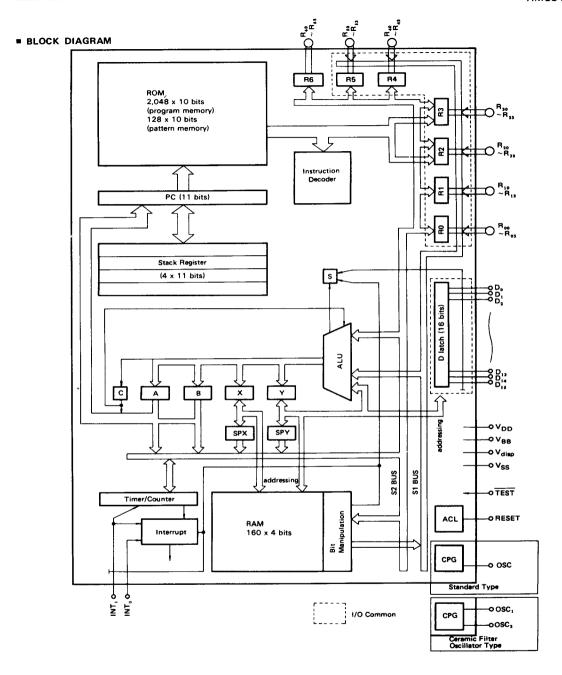

The HMCS45A is the PMOS 4-bit single chip microcomputer which contains ROM, RAM, I/O and Timer/Event Counter on single chip. The HMCS45A is designed to perform efficient controller function as well as arithmetic function for both binary and BCD data. The PMOS technology of the HMCS45A provides high voltage I/O capability for direct driving vacuum-fluorescent

#### **■ FEATURES**

- 4-bit Architecture

- 2,048 Words of Program ROM (10 bits/Word) 128 Words of Pattern ROM (10 bits/Word)

- 160 Digits of Data RAM (4 bits/Digit)

- 44 I/O Lines and 2 External Interrupt Lines

- Timer/Event Counter

- 10 usec Instruction Cycle Time

- All Instructions except One Instruction; Single Word and Single Cycle

- **BCD Arithmetic Instructions**

- Pattern Generation Instruction

- Table Look Up Capability —

- - Powerful Interrupt Function 3 Interrupt Sources

- -2 External Interrupt Lines

- Timer/Event Counter

- Multiple Interrupt Capability

- Bit Manipulation Instructions for Both RAM and I/O

- High Voltage I/O Capability, -49V max.

- Option of I/O Configuration Selectable on Each Pin; Pull Up MOS or Open Drain

- Built-in RC Oscillator; Standard Type (HD38820)

- Built-in Ceramic Filter Oscillator; Ceramic Filter Oscillator Type (HD38825)

- Built-in Power-on Reset Circuit

- Stand-by Mode (RAM Data Hold); 8mW max.

- PMOS Technology

- Single, 10V Power Supply

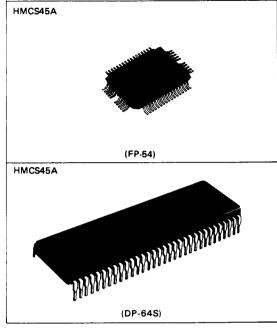

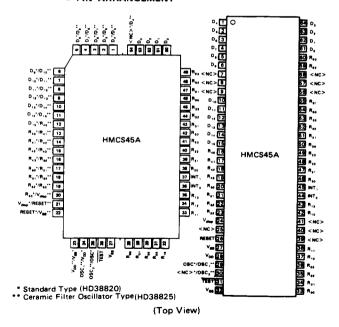

PIN ARRANGEMENT

(2) HITACHI

( HITACHI

#### ■ ABSOLUTE MAXIMUM RATINGS

| Item                         | Symbol            | Value       | Unit | Remarks                                          |

|------------------------------|-------------------|-------------|------|--------------------------------------------------|

| Pin Voltage (1)              | -V <sub>T1</sub>  | -0.3 to +18 | V    | Except for pins specified by -V <sub>T2</sub>    |

| Pin Voltage (2)              | -v <sub>T2</sub>  | -0.3 to +50 | V    | Applied to high break-down voltage pins [Note 3] |

| Maximum Power Consumption    | P <sub>C</sub>    | 400         | mW   |                                                  |

| Maximum Total Output Current | - ΣI <sub>o</sub> | 45          | mA   | [Note 4]                                         |

| Operating Temperature        | Topr              | -20 to +75  | °C   |                                                  |

| Storage Temperature          | T <sub>stq</sub>  | -55 to +125 | °C   |                                                  |

[NOTE 1] Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under the conditions of "ELECTRICAL CHARACTERISTICS-1, -2." If these conditions are exceeded, it could affect reliability of LSI.

[NOTE 2] All voltages are with respect to VSS.

- [NOTE 3] High break-down voltage pins can be specified by user among the following pins. They are specified at ROM ordering using the "Mask Option List". (Unspecified pins are low break-down voltage pins.)

- $D_0$  to  $D_{19}$ ,  $R_{00}$  to  $R_{03}$ ,  $R_{10}$  to  $R_{19}$ ,  $R_{20}$  to  $R_{29}$ ,  $R_{30}$  to  $R_{33}$ ,  $R_{40}$  to  $R_{43}$ ,  $R_{50}$  to  $R_{53}$ ,  $R_{60}$  to  $R_{63}$ , INT $_0$ , INT $_1$ , RESET,  $V_{disp}$ . Other pins cannot be specified as high break-down voltage pin.

[NOTE 4] Maximum Total Output Current is the total sum of output currents which can flow out simultaneously from output pins and I/O common pins.

### ■ ELECTRICAL CHARACTERISTICS-1 ( $-V_{DD} = -V_{BB} = 10V \pm 10\%$ , $-V_{disp} = 49V$ max., $T_a = -20$ to +75°C)

| 14                        | S. mahal           | Test Conditions                            |                     | Value |      |      | Note |

|---------------------------|--------------------|--------------------------------------------|---------------------|-------|------|------|------|

| Item                      | Symbol             | 1 est Conditions                           | min                 | typ   | max  | Unit | NOTE |

| 1 (11 // Malana /1)       |                    | -V <sub>DD</sub> =-V <sub>BB</sub> =9V     | 4.0                 | -     | 49   | V    | 3    |

| Input "Low" Voltage (1)   | -V <sub>1L1</sub>  | -V <sub>DD</sub> =-V <sub>BB</sub> =11V    | 4.7                 | _     | 45   | *    | "    |

| t (1) (2)                 | - V <sub>IL2</sub> | -V <sub>DD</sub> =-V <sub>BB</sub> =9V     | 4.0                 |       | 49   | v    | 4    |

| Input "Low" Voltage (2)   |                    | - V <sub>DD</sub> =- V <sub>BB</sub> = 11V | 4.7                 | _     | 45   | _ `  |      |

| Input "High" Voltage (1)  | - V <sub>IH1</sub> |                                            | - "                 | _     | 2.55 | V    | 3    |

| Input "High" Voltage (2)  | - V <sub>IH2</sub> |                                            | T -                 | _     | 2.0  | V    | 4    |

| Output "Low" Voltage (1)  | V <sub>OL1</sub>   | -V <sub>disp</sub> =49V                    | 45                  | _     | -    | V    | 5    |

| Output "Low" Voltage (2)  | -V <sub>OL2</sub>  | 56kΩ to -49V                               | 45                  | _     | -    | V    | 6    |

| Output "High" Voltage (1) | - V <sub>OH1</sub> | -I <sub>OH</sub> =3mA                      | _                   |       | 1.8  | V    | 7    |

| Output "High" Voltage (2) | - V <sub>OH2</sub> | -I <sub>OH</sub> =10mA                     | _                   | _     | 1.8  | V    | 8    |

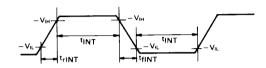

| Interrupt Input Hold Time | t <sub>INT</sub>   |                                            | 2·T <sub>inst</sub> | _     |      | μs   |      |

| Interrupt Input Fall Time | t <sub>fINT</sub>  |                                            | -                   | _     | 50   | μs   |      |

| Interrupt Input Rise Time | t <sub>rINT</sub>  |                                            |                     | _     | 50   | μs   |      |

| Input Leakage Current     | - I <sub>IL</sub>  | -V <sub>in</sub> =0 to 49V                 | _                   | _     | 50   | μΑ   | 9    |

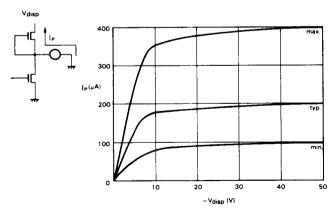

| Pull up MOS Current       | l <sub>P</sub>     | -V <sub>disp</sub> =45V                    | 100                 | _     | 400  | μΑ   | 2    |

| Superior Course           | -I <sub>DD</sub>   |                                            | -                   | _     | 30   | mA   |      |

| Supply Current            | -I <sub>BB</sub>   |                                            | <u> </u>            | _     | 4    | mA   | İ    |

(to be continued)

|                                       |                       | T                                                    | Value |            |           | l lmia    | Note |

|---------------------------------------|-----------------------|------------------------------------------------------|-------|------------|-----------|-----------|------|

| Item                                  | Symbol                | Test Conditions                                      | min   | typ        | max       | Unit      | NOTE |

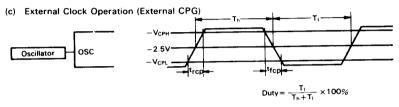

| External Clock Operation [Standard    | Type]                 |                                                      |       | <b>-</b> : | <b></b> . | . <b></b> |      |

| External Clock Frequency              | f <sub>cp</sub>       |                                                      | 200   | _          | 440       | kHz       |      |

| External Clock Duty                   | Duty                  |                                                      | 45    | 50         | 55        | %         |      |

| External Clock Rise Time              | t <sub>rcp</sub>      |                                                      | 0     | -          | 0.2       | μs        |      |

| External Clock Fall Time              | t <sub>fcp</sub>      |                                                      | 0     | _          | 0.2       | μs        |      |

| External Clock "Low" Level            |                       | -V <sub>DD</sub> =-V <sub>BB</sub> =9V               | 4.0   |            | 17        | V         |      |

|                                       | -V <sub>CPL</sub>     | -V <sub>DD</sub> =-V <sub>BB</sub> =11V              | 4.7   | 1 -        | ''        | •         |      |

| External Clock "High" Level           | -V <sub>CPH</sub>     |                                                      | _     | _          | 1.0       | ٧         | T    |

| Instruction Cycle Time                | T <sub>inst</sub>     | T <sub>inst</sub> =4/f <sub>cp</sub>                 | 9.1   | -          | 20        | μs        |      |

| Internal Clock Operation (Rf Cf Oscil | lation) [Standard T   | ype]                                                 |       |            | •         |           |      |

| Clock Oscillation Frequency           | fosc                  | $R_f = 30k\Omega \pm 2\%$ ,<br>$C_f = 100pF \pm 5\%$ | 320   |            | 480       | kHz       |      |

| Instruction Cycle Time                | T <sub>inst</sub>     | T <sub>inst</sub> =4/f <sub>OSC</sub>                | 8.4   |            | 12.5      | μs        |      |

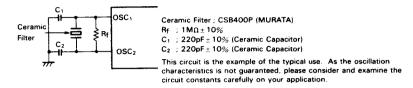

| Internal Clock Operation (Ceramic Fi  | Iter Oscillation) [Ce | ramic Filter Oscillator Type]                        |       |            |           |           |      |

| Clock Oscillation Frequency           | fosc                  | Ceramic Filter                                       | 392   | 1          | 408       | kHz       |      |

| Instruction Cycle Time                | Tinst                 | T <sub>inst</sub> =4/f <sub>OSC</sub>                | 9.8   | -          | 10.2      | μs        |      |

Specifications of low break-down voltage pins specified by user are as follows.

$(-V_{DD} = -V_{BB} = 10V \pm 10\%, -V_{disp} = 17V \text{ max., } Ta = -20 \text{ to } +75^{\circ}\text{C})$

|                          |                    | Total Conditions                        | Value |      | Unit | Note |

|--------------------------|--------------------|-----------------------------------------|-------|------|------|------|

| ltem                     | Symbol             | Test Conditions                         | min   | max  | Unit | NOTE |

|                          |                    | -V <sub>DD</sub> =-V <sub>BB</sub> =9V  | 4.0   | 17   | V    | 3    |

| Input "Low" Voltage (1)  | -V <sub>IL1</sub>  | -V <sub>DD</sub> =-V <sub>BB</sub> =11V | 4.7   | ] '′ | *    |      |

| (0)                      |                    | -V <sub>DD</sub> =-V <sub>BB</sub> =9V  | 4.0   | 17   | v    | 4    |

| Input "Low" Voltage (2)  | -V <sub>IL2</sub>  | -V <sub>DD</sub> =-V <sub>BB</sub> =11V | 4.7   | ] '′ |      |      |

| Output "Low" Voltage (1) | - V <sub>OL1</sub> | - V <sub>disp</sub> = 10V               | 8.5   | -    | V    | 5    |

| Output "Low" Voltage (2) | - V <sub>OL2</sub> | 56kΩ to -10V                            | 8.5   |      | V    | 6    |

| Input Leakage Current    | - I <sub>IL</sub>  | -V <sub>in</sub> =0 to 17V              | _     | 5    | μΑ   | 9    |

| Pull up MOS Current      | IР                 | -V <sub>disp</sub> =10V                 | 80    | 350  | μΑ   | 2    |

[NOTE 1] All voltages are with respect to  $V_{SS}$ .

[NOTE 2] Pull up MOS current (the current which flows in  $V_{disp}$  through pull up MOS when the pin is connected to  $V_{SS}$ ) varies with the value of  $V_{disp}$ . It is shown as follows.

Figure 1 IP vs. Vdisp

## **OHITACHI**

[NOTE 3] This is applied to  $D_0$  to  $D_{16}$ ,  $R_{00}$  to  $R_{03}$ ,  $R_{10}$  to  $R_{13}$ ,  $R_{20}$  to  $R_{23}$ ,  $R_{30}$  to  $R_{33}$ ,  $R_{40}$  to  $R_{43}$ ,  $R_{50}$  to  $R_{53}$ . [NOTE 4] This is applied to INT $_0$ , INT $_1$ , and RESET. The system is in the reset state when RESET is at "1" (High) level, and in the operating state at "0"

(Low) level. When Built-in Reset is used, RESET should be connected to V<sub>DD</sub>.

[NOTE 5] This is applied to With Pull up MOS pins.

[NOTE 6] This is applied to No Pull up MOS pins.

[NOTE 7] This is applied to R<sub>00</sub> to R<sub>03</sub>, R<sub>10</sub> to R<sub>13</sub>, R<sub>20</sub> to R<sub>23</sub>, R<sub>30</sub> to R<sub>33</sub>, R<sub>40</sub> to R<sub>43</sub>, R<sub>50</sub> to R<sub>53</sub>, R<sub>60</sub> to R<sub>63</sub>.

[NOTE 8] This is applied to Do to Dis [NOTE 9] Pull up MOS current is excluded.

### ■ ELECTRICAL CHARACTERISTICS-2 (Ta=-20 to +75°C)

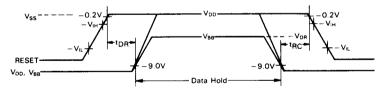

#### Reset

|                        |                   | <b>T.</b> 1. O. 1. M. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.                                                                                           | Value               |     | Unit  |  |

|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-------|--|

| ltem                   | Symbol            | Test Conditions                                                                                                                                        | min                 | max | Oiiii |  |

| Power Supply Fall Time | t <sub>fDD</sub>  | Built-in Reset                                                                                                                                         | 0.1                 | 10  | ms    |  |

| Power Supply OFF Time  | t <sub>OFF</sub>  | Built-in Reset                                                                                                                                         | 1                   |     | ms    |  |

|                        |                   | External Reset  - V <sub>DD</sub> = - V <sub>BB</sub> = 9 to 11V [Standard Type] (External Clock Operation, R <sub>f</sub> C <sub>f</sub> Oscillation) | 1                   | _   | ms    |  |

| RESET Pulse Width (1)  | t <sub>RST1</sub> | External Reset  -V <sub>DD</sub> =-V <sub>BB</sub> =9 to 11V  [Ceramic Filter Oscillator Type]  (Ceramic Filter Oscillation)                           | 4                   | 4 - |       |  |

| RESET Pulse Width (2)  | t <sub>RST2</sub> | External Reset -V <sub>DD</sub> =-V <sub>BB</sub> =9 to 11V                                                                                            | 2·T <sub>inst</sub> | _   | μs    |  |

| RESET Rise Time        | t <sub>rRST</sub> | -V <sub>DD</sub> =-V <sub>BB</sub> =9 to 11V                                                                                                           | -                   | 20  | ms    |  |

| RESET Fall Time        | t <sub>fRST</sub> | -V <sub>DD</sub> =-V <sub>BB</sub> =9 to 11V                                                                                                           | _                   | 20  | ms    |  |

[NOTE] All voltages are with respect to V<sub>SS</sub>.

#### Data Hold

|                         | 0                 | Test Conditions                                                                             | Value |     | Unit    |  |

|-------------------------|-------------------|---------------------------------------------------------------------------------------------|-------|-----|---------|--|

| Item                    | Symbol            | rest Conditions                                                                             | min   | max | 1 01111 |  |

| Data Hold Voltage       | -V <sub>DR</sub>  | RESET=-0.2V                                                                                 | 2.0   | _   | _ v     |  |

| Data Hold Current       | - I <sub>DR</sub> | RESET=-0.2V, -V <sub>DR</sub> =2V                                                           | _     | 4   | mA      |  |

| Data Save Time          | t <sub>DR</sub>   |                                                                                             | 100   |     | μs      |  |

|                         |                   | [Standard Type]<br>(External Clock Operation,<br>R <sub>f</sub> C <sub>f</sub> Oscillation) | 1     | -   |         |  |

| Operation Recovery Time | t <sub>RC</sub>   | [Ceramic Filter Oscillator Type]<br>(Ceramic Filter Oscillation)                            | 4     | _   | ms      |  |

[NOTE] All voltages are with respect to V<sub>SS</sub>.

### SIGNAL DESCRIPTION

The input and output signals for the HMCS45A, shown in PIN ARRANGEMENT, are described in the following paragraphs.

#### $V_{DD}$ , $V_{BB}$ and $V_{SS}$

Power is supplied to the HMCS45A using these pins. V<sub>DD</sub> is power of logic parts except RAM, VBB is power of RAM and VSS is ground connection.

$V_{disp}$  is used as power supply of Pull up MOS and has no relation to internal logic operation.

This pin resets the HMCS45A independently of the automatic resetting capability (ACL; Built-in Reset Circuit) already in the HMCS45A. The HMCS45A can be reset by pulling RESET high. Refer to RESET FUNCTION for additional information.

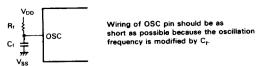

#### OSC (OSC<sub>1</sub> and OSC<sub>2</sub>)

These pins provide control input for the built-in oscillator circuit. Resistor and capacitor, ceramic filter circuit, or an external oscillator can be connected to these pins to provide a system clock with various degrees of stability/cost tradeoffs. Lead length and stray capacitance on these two pins should be minimized.

Refer to OSCILLATOR for recommendations about these pins.

#### • TEST

This pin is not for user application and must be connected to

#### INT<sub>o</sub> and INT,

These pins generate interrupt request to the HMCS45A. Refer to INTERRUPTS for additional information.

ullet R<sub>00</sub> to R<sub>03</sub>, R<sub>10</sub> to R<sub>13</sub>, R<sub>20</sub> to R<sub>23</sub>, R<sub>30</sub> to R<sub>33</sub>, R<sub>40</sub> to R<sub>43</sub>,

R<sub>50</sub> to R<sub>53</sub>

These 24 lines are arranged into six 4-bit Data Input/Output Common Channels. The 4-bit registers (Data I/O Register) are attached to these channels. Each channel is directly addressed by the operand of input/output instruction.

Refer to INPUT/OUTPUT for additional information.

#### R<sub>60</sub> to R<sub>63</sub>

These 4 lines are the 4-bit Data Output Channel. The 4-bit register (Data I/O Register) is attached to this channel. This channel is directly addressed by the operand of input/output instruction.

Refer to INPUT/OUTPUT for additional information.

#### • D<sub>0</sub> to D<sub>15</sub>

These lines are sixteen 1-bit Discrete Input/Output Common Pins. The 1-bit latches are attached to these pins. Each pin is addressed by the Y register. The Do to D3 pins are also addressed directly by the operand of input/output instruction.

Refer to INPUT/OUTPUT for additional information.

#### - ROM

#### **ROM Address Space**

ROM is used as a memory for the instructions and the patterns (constants). The instruction used in the HMCS45A consists of 10 bits. These 10 bits are called "a word", which is a unit for writing into ROM.

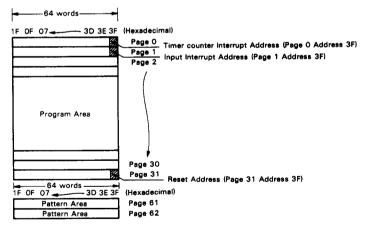

The ROM address is composed of the program area (page 0 to page 31) and the pattern area (pages 61, 62). (64 words/page).

The ROM capacity is 2,176 words (1 word = 10 bits) in all. Only the program area can contain both the instructions and the patterns (constants).

The ROM address space is shown in Figure 2.

Figure 2 ROM Address Space

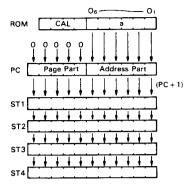

#### Program Counter (PC)

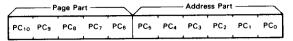

The program counter is used for addressing of ROM. It consists of the page part and the address part as shown in Figure 3.

Figure 3 Configuration of Program Counter

Once a certain value is loaded into a page part, the content is unchanged until other value is loaded by the program. Any number among 0 to 31 can be set in the page part.

The address part is a 6-bit polynomial counter and counts up for each instruction cycle time. The sequence in the decimal and hexadecimal system is shown in Table 1. This sequence forms a loop and has neither the starting nor ending point. It doesn't generate an overflow carry. Consequently, the program on a same page is executed in order unless the value of the bank part is changed.

Table 1 Program Counter Address Part Sequence

| Decimal | Hexadecimal | Decimal | Hexadecimal | Decimal | Hexadecimal |

|---------|-------------|---------|-------------|---------|-------------|

| 63      | 3F          | 5       | 05          | 9       | 09          |

| 62      | 3E          | 11      | ОВ          | 19      | 13          |

| 61      | 3D          | 23      | 17          | 38      | 26          |

| 59      | 3B          | 46      | 2E          | 12      | ос          |

| 55      | 37          | 28      | 1C          | 25      | 19          |

| 47      | 2F          | 56      | 38          | 50      | 32          |

| 30      | 1E          | 49      | 31          | 37      | 25          |

| 60      | зс          | 35      | 23          | 10      | OA.         |

| 57      | 39          | 6       | 06          | 21      | 15          |

| 51      | 33          | 13      | OD          | 42      | 2A          |

| 39      | 27          | 27      | 18          | 20      | 14          |

| 14      | OE          | 54      | 36          | 40      | 28          |

| 29      | 1D          | 45      | 2D          | 16      | 10          |

| 58      | 3A          | 26      | 1A          | 32      | 20          |

| 53      | 35          | 52      | 34          | 0       | 00          |

| 43      | 2B          | 41      | 29          | 1       | 01          |

| 22      | 16          | 18      | 12          | 3       | 03          |

| 44      | 2C          | 36      | 24          | 7       | 07          |

| 24      | 18          | 8       | 08          | 15      | OF          |

| 48      | 30          | 17      | 11          | 31      | 1F          |

| 33      | 21          | 34      | 22          |         |             |

| 2       | 02          | 4       | 04          |         |             |

#### Designation of ROM Address and ROM Code

100

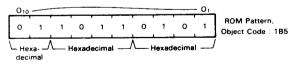

The page part of the ROM address is represented by decimal and the address part is divided into 2 parts (2 bits and 4 bits) and represented by hexadecimal.

One word (10 bits) is divided into three parts (2 bits, 4 bits and 4 bits from the most significant bit  $O_{10}$ ) and represented by hexadecimal. The examples are shown in Figure 4.

#### (a) ROM Address

### (b) ROM Code

Figure 4 Designation of ROM Address and ROM Code

( HITACHI

#### **■ PATTERN GENERATION**

The pattern (constants) can be accessed by the pattern instruction (P). The pattern can be written in any address of the ROM address space.

#### Reference

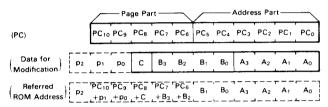

ROM addressing for reference of the patterns is achieved by modifying the program counter with the accumulator, the B register, the Carry F/F and the operand p. Figure 5 shows how to modify the program counter. The address part is replaced with the accumulator and the lower 2 bits of B register, while the page part is ORed with the upper 2 bits of B register, the Carry F/F and the operand p (po, pi). The upper bit (p2) of the operand is for referring to the pattern area.

The contents of the program counter is only modified apparently and is not changed. Then the address is counted up after the execution of the pattern instruction and the next instruction is executed.

The pattern instruction is executed in 2 cycles.

Even when interrupt is enable, interrupt is disabled in the second cycle of the pattern instruction. However, the interrupt request is latched into the interrupt request F/F.

#### Generation

The pattern of referred ROM address is generated as the following two ways:

(i) The pattern is loaded into the accumulator and B register.

(ii) The pattern is loaded into the Data I/O registers R2 and R3.

The command bits  $(O_9, O_{10})$  in the pattern determine which way is taken.

Mode (i) is performed when  $O_9$  is "1" and mode (ii) is performed when  $O_{10}$  is "1".

Mode (i) and mode (ii) are simultaneously performed when both  $O_9$  and  $O_{10}$  are "1".

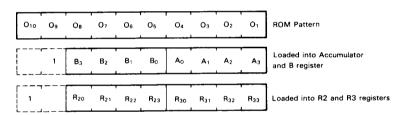

The correspondence of each bit of the pattern is shown in Figure 6.

Examples of how to use the pattern instruction is shown in Table ?

Figure 5 ROM Addressing for Pattern Generation

Figure 6 Correspondence of Each Bit of Pattern

Table 2 Example of how to use Pattern Instruction

| Bet      | Before Execution |     |   |   |                | D-111-  |   | After E | xecution | 1  |

|----------|------------------|-----|---|---|----------------|---------|---|---------|----------|----|

| PC Value | р                | С   | В | Α | ROM<br>Address | Pattern | В | Α       | R2       | R3 |

| 0-3F     | 1                | 0   | Α | 0 | 10-20          | 12D     | 2 | В       | _        | _  |

| 0-3F     | 7                | 1   | 4 | 0 | 61-00          | 22D     | _ |         | 4        | В  |

| 30-00    | 4                | 0/1 | 0 | 9 | 62-09          | 32D     | 2 | В       | 4        | В  |

| 30-00    | 4                | 0/1 | F | 9 | 63-39          |         |   |         |          |    |

<sup>&</sup>quot;-" means that the value is unchanged after the execution.

#### **■ BRANCH**

ROM is accessed according to the program counter sequence and the program is executed. In order to jump to any address out of the sequence, there are four ways.

They are explained in the following paragraphs.

#### • BR

By BR instruction, the program branches to an address in the current page.

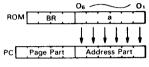

The lower 6 bits of ROM Object Code (operand a, O<sub>6</sub> to O<sub>1</sub>) are transferred to the lower 6 bits of the program counter. This instruction is a conditional instruction and executed only when

### **OHITACHI**

<sup>&</sup>quot;0/1" means that either "0" or "1" will do.

the Status F/F is "1". If it is "0", the instruction is skipped and the Status F/F becomes "1". The operation is shown in Figure 7.

#### • LPU

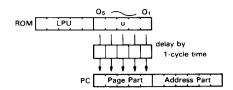

By LPU instruction, a jump between pages is performed.

The lower 5 bits of the ROM Object Code (operand u) are transferred to the page part of the program counter with a delay of 1 instruction cycle time. Therefore, the cycle just after the issuing of this instruction is on the same page and the page jump is performed at the next cycle.

This instruction is a conditional instruction and performed only when the Status is "1". But the Status is unchanged (remains "0") even if it is skipped. The operation is shown in Figure 8.

Figure 7 BR Operation

Figure 8 LPU Operation

#### • BRL

By BRL instruction, the program branches to an address in any page.

This instruction is a macro instruction of LPU and BR instructions, which is divided into two steps as follows.

$$\begin{array}{ccc} BRL & a-b \rightarrow LPU & a \\ < Jump \text{ to address b on page a} > & BR & b \end{array}$$

BRL instruction is a conditional instruction because of its characteristics of LPU and BR instructions, and is executed only when the Status F/F is "1". If the Status F/F is "0", the instruction is skipped and the Status F/F becomes "1".

#### • TBR (Table Branch)

By TBR instruction, the program branches referring to the table.

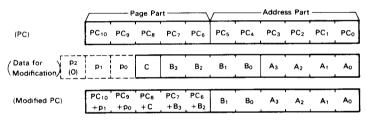

The program counter is modified with the accumulator, the B register, the Carry F/F, the operand p. The method for modification is shown in Figure 9.

Figure 9 Modification of Program Counter by TBR Instruction

The accumulator and the lower 2 bits of B register are assigned into the address part of the program counter. The upper 2 bits of B register, Carry F/F, and the operand p<sub>1</sub>, p<sub>0</sub> are ORed with the page part of the program counter.

TBR instruction is executed regardless of the Status F/F, and does not affect the Status F/F.

#### **■ SUBROUTINE JUMP**

There are two types of subroutine jumps. They are explained in the following paragraphs.

#### • CAL

By CAL instruction, subroutine jump to an address in the Subroutine Page is performed.

The Subroutine Page is page 0.

The address next to CAL instruction address is pushed onto the stack ST1 and the contents of the stacks ST1, ST2 and ST3 are pushed onto the stacks ST2, ST3 and ST4 respectively as shown in Figure 10.

The page part of the program counter is 0. The lower 6 bits (operand a,  $O_6$  to  $O_1$ ) of the ROM Object Code are transferred to the address part of the program counter.

The HMCS45A has 4 levels of stack (ST1, ST2, ST3 and ST4) which allows the programmer to use up to 4 levels of subroutine jumps (including interrupts).

CAL is a conditional instruction and executed only when the Status F/F is "1". If the Status F/F is "0", it is skipped and the Status F/F changes to "1".

#### • CALL

By CALL instruction, subroutine jump to an address in any page is performed.

This instruction is a macro instruction of LPU and CAL. The subroutine jumps to the page specified by LPU enables the subroutine jump to an optional address.

$$\begin{array}{ccc} CALL & a-b \rightarrow LPU & a \\ < Subroutine jump to address b on page \ a > & CAL \ b \end{array}$$

CALL instruction is conditional because of characteristics of LPU and CAL instructions and is executed when the Status F/F is "1". If the Status F/F is "0", it is skipped and the Status F/F changes to "1".

### ( HITACHI

Figure 10 Subroutine Jump Stacking Order

#### m RAM

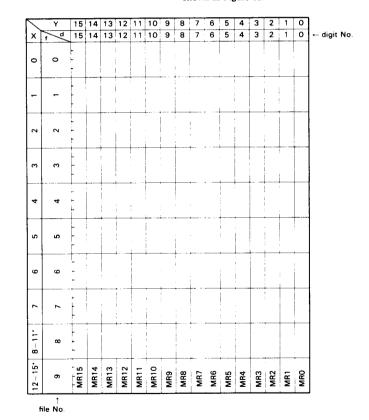

RAM is a memory used for storing data and saving the contents of the registers. Its capacity is 160 digits (640 bits) where one digit consists of 4 bits.

Addressing of RAM is performed by a matrix of the file No. and the digit No.

The file No. is set in the X register and the digit No. in the Y register for reading, writing or testing. Specific digits in RAM can be addressed not via the X register and Y register. These digits, 16 digits (MR0 to MR15), are called "Memory Register (MR)". The memory register can be exchanged with the accumulator by XAMR instruction.

The RAM address space is shown in Figure 11.

If an instruction consists of a simultaneous read/write operation of RAM (exchange between the contents of RAM and those of the register), the writing data doesn't affect the reading data because read operation precedes write operation.

The RAM bit manipulation instruction enables any addressed RAM bit to be set, reset or tested. The bit assignment is specified by the operand n of the instruction.

The bit test makes the Status F/F "1" and makes it "0" when the assigned bit is "0".

Correspondence between the RAM bit and the operand n is shown in Figure 12.

The file 8 is selected when X register has any value among 8 to 11, and the file 9 is selected when 12 to 15.

Figure 11 RAM Address Space

### **@**HITACHI

Figure 12 RAM Bit and Operand n

#### ■ REGISTER

The HMCS45A has six 4-bit registers and two 1-bit registers available to the programmer. The 1-bit registers are the Carry F/F and the Status F/F. They are explained in the following paragraphs.

#### • Status F/F (S)

The Status F/F latches the result of logical or arithmetic operations (Not Zero, Overflow) and bit test operations. The Status F/F affects conditional instructions (LPU, BR and CAL instructions). These instructions are executed only when the Status F/F is "1". If it is "0", these instructions are skipped and the Status F/F becomes "1"

### • Accumulator (A; A Register) and Carry F/F (C)

The result of the Arithmetic Logic Unit (ALU) operation (4 bits) and the overflow of the ALU are loaded into the accumulator and the Carry F/F respectively. The Carry F/F can be set, reset or tested. Combination of the accumulator and the Carry F/F can be right or left rotated. The accumulator is the main register for ALU operation and the Carry F/F is used to store the overflow generated by ALU operation when the calculation of two or more digits (4 bits/digit) is performed.

#### B Register (B)

The result of ALU operation (4 bits) is loaded into this register. The B register is used as a sub-accumulator to stack data temporarily and also used as a counter.

#### X Register (X)

104

The result of ALU operation (4 bits) is loaded into this register. The X register is exchangeable with the SPX register and addresses the RAM file.

#### • SPX Register (SPX)

The SPX register is exchangeable with the X register.

The SPX register is used to stack the contents of the X register and expand the addressing system of RAM in combination with the X register.

#### Y Register (Y)

The result of ALU operation (4 bits) is loaded into this register. The Y register is exchangeable with the SPY register. The Y register can calculate itself simultaneously with transferring data by the bus lines, which is usable for the calculation of two or more digits (4 bits/digit). The Y register addresses the RAM digits and 1-bit Discrete I/Os.

#### • SPY Register (SPY)

The SPY register is exchangeable with the Y register. The SPY register is used to stack the contents of the Y register and expand the addressing system of RAM and 1-bit Discrete I/Os in combination with the Y register.

#### ■ INPUT/OUTPUT

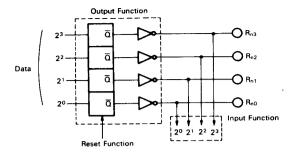

### • 4-bit Data Input/Output Channel (R)

The HMCS45A has six 4-bit Data I/O Common Channels (R0 to R5) and one 4-bit Output Channel (R6).

The 4-bit registers (Data I/O Register) are attached to these channels.

Each channel is directly addressed by the operand p of input/output instruction.

The data is transferred from the accumulator and the B register to the Data I/O Registers R0 to R6 via the bus lines. ROM bit patterns are loaded into the Data I/O Registers R2 and R3 by the pattern instruction.

The input instruction inputs the 4-bit data into the accumulator and the B register through the channels R0 to R5. Note that, since the Data I/O Register output is directly connected to the pin even during execution of input instruction, the input data is wired logic of the Data I/O Register output and the pin input.

Therefore, the Data I/O Register should be set to 0 (all bits of the Data I/O Register is "0") not to affect the pin input before execution of input instruction.

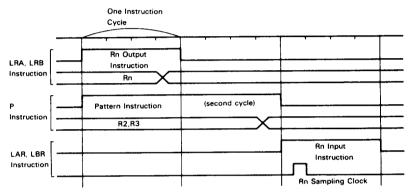

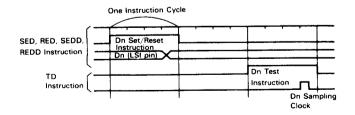

The block diagram is shown in Figure 13. The I/O timing is shown in Figure 14.

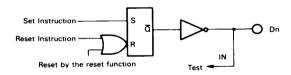

#### • 1-bit Discrete Input/Output Common Pin (D)

The HMCS45A has sixteen 1-bit Discrete I/O Common Pins. The 1-bit Discrete I/O is addressed by the Y register. The addressed latch can be set or reset by output instruction and level ("0" or "1") of the addressed pin can be tested by an input instruction.

Note that, since the latch output is directly connected to the pin even during execution of input instruction, the input data is wired logic of the latch output and the pin input. Therefore, the latch should be reset to "0" not to affect the pin input before execution of input instruction.

The  $D_0$  to  $D_3$  are also addressed directly by the operand n of input/output instruction and can be set or reset.

The block diagram is shown in Figure 15 and the I/O timing is in Figure 16.

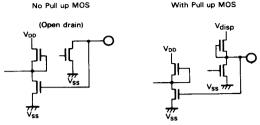

#### • I/O Configuration

The I/O configuration of each pin can be specified among Open Drain and With Pull up MOS using a mask option as shown in Figure 17.

Figure 13 4-bit Data I/O Block Diagram

Figure 14 4-bit Data I/O Timing

Figure 15 1-bit Discrete I/O Block Diagram

Figure 16 1-bit Discrete I/O Timing

### **@**HITACHI

Applied Pins; Reo to Res

No Pull up MOS

With Pull up MOS

Vdisp

Vss

(a) Configuration of Output Pin

Applied Pins;  $D_0$  to  $D_{15}$ ,  $R_{00}$  to  $R_{03}$ ,  $R_{10}$  to  $R_{13}$ ,  $R_{20}$  to  $R_{23}$ ,  $R_{30}$  to  $R_{33}$ ,  $R_{40}$  to  $R_{43}$ ,  $R_{50}$  to  $R_{53}$

(b) Configuration of I/O Pin

Figure 17 I/O Configuration

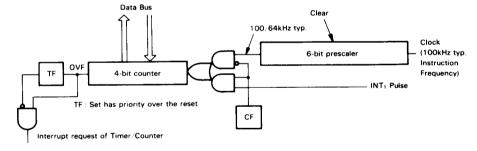

#### **■ TIMER/COUNTER**

The timer/counter consists of 4-bit counter and 6-bit prescaler as shown in Figure 18.

The counter operates in the Timer Mode or Counter Mode according to the counting object. In the timer mode it counts overflow output pulse from the prescaler, and in the Counter Mode it counts INT, input pulse (counts leading edge), and increments to 15. Mode selection is determined according to the state of the CF. When the counter reaches zero (returns from 15), overflow output pulse is generated and the counter continues to count  $(14 \rightarrow 15 \rightarrow 0 \rightarrow 1 \rightarrow \cdots)$ .

The relation between the specified value of the counter and specified time in the Timer Mode is shown in Table 3.

The prescaler is a 6-bit frequency divider. It generates 100/64 kHz pulses by dividing the system clock by 64. The prescaler is cleared when the data is loaded into the 4-bit counter by LTA, LTI instructions. The frequency division is 0 when the prescaler

is cleared. At the 64th clock, an overflow output pulse is generated from the prescaler. During operation of the LSI, the prescaler operates and cannot be stopped.

The CF is the flip-flop (F/F) which controls the counter input. When the CF F/F is "1", input pulse of INT, is input to the counter (Counter Mode). When the CF is "0", prescaler overflow output pulse is input to the counter (Timer Mode).

The TF is the flip-flop (F/F) which masks the interrupt request from the timer/counter. It is set, reset and tested by instructions. If the overflow output pulse of the counter is generated when the TF F/F is "0", an interrupt request occurs and the TF F/F becomes "1". If the overflow output pulse is generated when the TF F/F is "1", no interrupt request occurs. So it can be used as timer/counter interrupt mask.

The pulse width of INT, in the Counter Mode should be two or more cycles both at "High" and "Low" levels as shown in Figure 19.

Figure 18 Timer/Counter Block Diagram

Table 3 Timer Range

| Specified<br>Value | Cycles | Time (ms) | Specified<br>Value | Cycles | Time (ms) |

|--------------------|--------|-----------|--------------------|--------|-----------|

| 0                  | 1,024  | 10.24     | 8                  | 512    | 5.12      |

| 1                  | 960    | 9.60      | 9                  | 448    | 4.48      |

| 2                  | 896    | 8.96      | 10                 | 384    | 3.84      |

| 3                  | 832    | 8.32      | 11                 | 320    | 3.20      |

| 4                  | 768    | 7.68      | 12                 | 256    | 2.56      |

| 5                  | 704    | 7.04      | 13                 | 192    | 1.92      |

| 6                  | 640    | 6.40      | 14                 | 128    | 1.28      |

| 7                  | 576    | 5.76      | 15                 | 64     | 0.64      |

[NOTE] Time is based on instruction frequency 100kHz. (one instruction cycle =  $10\mu s$ )

Figure 19 The Pulse Width of the INT<sub>1</sub> pin in the Counter Mode

### ■ INTERRUPT

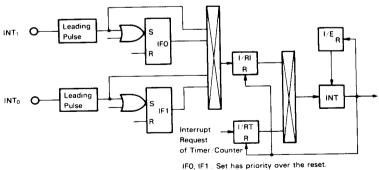

The HMCS45A can be interrupted in two different ways: through the external interrupt input pins (INT<sub>0</sub>, INT<sub>1</sub>) and the timer/counter interrupt request. When any interrupt occurs, processing is suspended, the Status F/F is unchanged, the contents of the present program counter is pushed onto the stack ST1 and the contents of the stacks ST1, ST2 and ST3 are pushed onto the stacks ST2, ST3 and ST4 respectively. At that time, the Interrupt Enable F/F (I/E) is set and the address jumps to a fixed destination (Interrupt Address), and then the interrupt routine is executed. Stacking the registers other than the program counter must be performed by the program. The interrupt routine must end with RTNI (Return Interrupt) instruction which sets the I/E F/F simultaneously with the RTN instruction.

The Interrupt Address:

Input Interrupt Address . . . . . Page 1 Address 3F

Timer/Counter Interrupt Address . . . . .

Page 0 Address 3F

The input interrupt has priority over the timer/counter interrupt.

The INT<sub>0</sub> and INT<sub>1</sub> pins have interrupt request functions.

Each pin consists of a circuit which generates leading pulse and the interrupt mask F/F (IF0, IF1). An interrupt is enabled (unmasked) when the IF0 F/F or IF1 F/F is reset. When the INT<sub>0</sub> or INT<sub>1</sub> pin changes from "0" to "1" (from "Low" level to "High" level), a leading pulse is generated to produce an interrupt request. At the same time, the IF0 F/F or IF1 F/F is set. When the IF0 F/F or IF1 F/F is set, it is an interrupt mask for INT<sub>0</sub> or INT<sub>1</sub>. (If a leading pulse is generated, no interrupt request occurs.)

An interrupt request generated by the leading pulse is latched into the input interrupt request F/F (I/RI) on the input side. If the Interrupt Enable F/F (I/E) is "1" (Interrupt Enable State), an interrupt occurs immediately and the I/RI F/F and the I/E F/F are reset. If the I/E F/F is "0" (Interrupt Disable State), the I/RI F/F is held at "1" until the HMCS45A gets into the Interrupt Enable State.

The IFO F/F, the IF1 F/F, the INT<sub>0</sub> pin and the INT<sub>1</sub> pin can be tested by interrupt instruction. Therefore, the INT<sub>0</sub> and the INT, can be used as additional input pins with latches.

An interrupt request from the timer/counter is latched into the timer interrupt request F/F (I/RT). The succeeding operations are the same as an interrupt from the input. Only the exception is that, since an interrupt from the input precedes a timer/counter interrupt, the input interrupt occurs if both the I/RI F/F and the I/RT F/F are "1" (when the input interrupt and the timer/counter interrupts are generated simultaneously). During this processing, the I/RT F/F remains "1". The timer/counter interrupt can be implemented after the input interrupt servicing is achieved.

The interrupt circuit block diagram is shown in Figure 20.

Figure 20 Interrupt Circuit Block Diagram

### **@HITACHI**

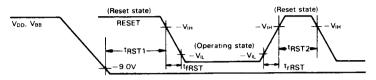

#### **■ RESET FUNCTION**

The reset is performed by setting the RESET pin to "1" ("High" level) and the HMCS45A gets into operation by setting it to "0" ("Low" level); Refer to Figure 21. Moreover, the HMCS45A has the automatic reset function (ACL; Built-in Reset Circuit). The Built-in Reset Circuit restricts the rise condition of the power supply; Refer to Figure 22. When the Built-in Reset Circuit is used, RESET should be connected to V<sub>SS</sub>.

Internal state of the HMCS45A is specified as follows by the

reset function.

- Program Counter (PC) is set to 3F address on 31 page (31-3F).

- · I/RI, I/RT, I/E and CF are reset to "0".

- · IF0, IF1 and TF are set to "1"

- I/O latch and registers (D<sub>0</sub> to D<sub>15</sub>, R0 to R6) are set to "0".

Note that other blocks (Status, Register, Timer/Counter, RAM, etc.) are not cleared.

- tRST1 includes the time required from the power ON until the operation gets into the constant state.

- · tRST2 is applied when the operation is in the constant state.

Figure 21 RESET Timing

Figure 22 Power Supply Timing for Built-in Reset Circuit

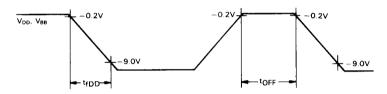

#### **■ DATA HOLD FUNCTION**

The Data Hold Function is the function to hold the data of RAM at low power dissipation. In the Data Hold Mode, all the data of RAM are held.

The power supply consists of  $V_{DD}$  and  $V_{BB}$ , but these are used as one power supply (that is,  $V_{DD} = V_{BB}$ ) in the operation.

V<sub>disp</sub> is only used as a power supply of Pull up MOS of I/O pin.

$V_{DD}$  is the power supply of logic parts except RAM and  $V_{BB}$  is that of RAM. Therefore, the "Data Hold" is feasible at  $V_{DD}$  OFF and  $V_{BB}$  ON. The system should be in the reset state during the "Data Hold" in order to prevent RAM from writing at  $V_{DD}$  OFF.

Figure 23 Data Hold Timing

#### ■ OSCILLATOR

The HMCS45A contains its own on-board oscillator and clock circuit (Built-in CPG) requiring only an external timing control element. Also the HMCS45A can be provided an externally gen-

erated clock as a frequency source by an external oscillator (External CPG).

The user can select one clock operation mode using a mask option as shown in Figure 24.

(C) HITACHI

(a) Internal Clock Operation Using Rf and Capacitor Cf (Built-in CPG; Rf Cf Oscillator)

(b) Internal Clock Operation Using Ceramic Filter Circuit (Built-in CPG; Ceramic Filter Oscillator)

Figure 24 Clock Operation Mode

109

110

#### ■ INSTRUCTION LIST

The instructions of the HMCS45A are listed according to their functions, as shown in Table 4.

Table 4 Instruction List

| Group                  | Mnemonic  | Function                                                     | Status  |

|------------------------|-----------|--------------------------------------------------------------|---------|

|                        | LAB       | B → A                                                        |         |

|                        | LBA       | A → B                                                        |         |

| Register · Register    | LAY       | Y → A                                                        |         |

| Instruction            | LASPX     | SPX → A                                                      |         |

|                        | LASPY     | SPY → A                                                      |         |

|                        | XAMR m    | A ↔ MR (m)                                                   |         |

|                        | LXA       | $A \rightarrow X$                                            |         |

|                        | LYA       | $A \rightarrow Y$                                            |         |

|                        | LXI i     | i → X                                                        |         |

|                        | LYI i     | i → Y                                                        | ļ       |

| DAMA Address Besister  | IY        | Y+1 → Y                                                      | NZ      |

| RAM Address Register   | DY        | Y-1 → Y                                                      | NB      |

| Instruction            | AYY       | $Y+A \rightarrow Y$                                          | С       |

|                        | SYY       | $Y-A \rightarrow Y$                                          | NB      |

|                        | XSPX      | X SPX                                                        |         |

|                        | XSPY      | Y SPY                                                        |         |

|                        | XSPXY     | X SPX, Y SPY                                                 |         |

|                        | LAM (XY)  | M → A (XY ↔ SPXY)                                            |         |

|                        | LBM (XY)  | M → B (XY ↔ SPXY)                                            |         |

| RAM · Register         | XMA (XY)  | M → A (XY → SPXY)                                            |         |

| Instruction            | XMB (XY)  | M → B (XY → SPXY)                                            |         |

|                        | LMAIY (X) | $A \rightarrow M, Y+1 \rightarrow Y (X \leftrightarrow SPX)$ | NZ      |

|                        | LMADY (X) | $A \rightarrow M, Y-1 \rightarrow Y (X \rightarrow SPX)$     | NB      |

|                        | LMIIY i   | $i \rightarrow M, Y+1 \rightarrow Y$                         | NZ      |

| Immediate Transfer     | LAI i     | i → A                                                        | :       |

| Instruction            | LBI i     | i → B                                                        |         |

|                        | Ali       | $A+i \rightarrow A$                                          | С       |

|                        | IB        | B+1 → B                                                      | NZ      |

|                        | DB        | B-1 → B                                                      | NB      |

|                        | AMC       | $M+A+C$ (F/F) $\rightarrow A$                                | С       |

|                        | SMC       | $M-A-C$ (F/F) $\rightarrow A$                                | NB      |

|                        | AM        | M+A → A                                                      | С       |

|                        | DAA       | Decimal Adjustment (Addition)                                |         |

|                        | DAS       | Decimal Adjustment (Subtraction)                             |         |

| Arithmetic Instruction | NEGA      | A+1 → A                                                      |         |

|                        | сомв      | B→B                                                          |         |

|                        | SEC       | "1" → C (F/F)                                                |         |

|                        | REC       | "O" → C (F/F)                                                |         |

|                        | тс        | Test C (F/F)                                                 | C (F/F) |

|                        | ROTL      | Rotation Left                                                |         |

|                        | ROTR      | Rotation Right                                               |         |

|                        | OR        | $A \cup B \rightarrow A$                                     |         |

(to be continued)

| Group                   | Mnemonic | Function                               | Status |

|-------------------------|----------|----------------------------------------|--------|

|                         | MNEI i   | <b>M</b> ≠ i                           | NZ     |

|                         | YNEI i   | Y ≠ i                                  | NZ     |

|                         | ANEM     | A ≠ M                                  | NZ     |

| Compare Instruction     | BNEM     | B ≠ M                                  | NZ     |

| ,                       | ALEI i   | A ≤ i                                  | NB     |

|                         | ALEM     | A ≤ M                                  | NB     |

|                         | BLEM     | B ≤ M                                  | NB     |

|                         | SEM n    | "1" → M (n)                            |        |

| RAM Bit Manipulation    | REM n    | "O" → <b>M</b> (n)                     |        |

| Instruction             | TM n     | Test M (n)                             | M (n)  |

|                         | BR a     | Branch on Status 1                     | 1      |

|                         | CAL a    | Subroutine Jump on Status 1            | 1      |

| ROM Address             | LPU u    | Load Program Counter Upper on Status 1 | 1      |

| Instruction             | TBR p    | Table Branch                           |        |

|                         | RTN      | Return from Subroutine                 |        |

|                         | SEIE     | "1" → I/E                              |        |

|                         | SEIFO    | "1" → IFO                              |        |

|                         | SEIF1    | "1" → IF1                              |        |

|                         | SETF     | "1" → TF                               |        |

|                         | SECF     | "1" → CF                               |        |

|                         | REIE     | "0" → I/E                              | 1      |

|                         | REIFO    | "0" → IFO                              |        |

|                         | REIF1    | "0" → IF1                              |        |

|                         | RETF     | "0" → TF                               |        |

| Industrial Installation | RECF     | "0" → CF                               |        |

| Interrupt Instruction   | TIO      | Test INT <sub>0</sub>                  | INT    |

|                         | TI1      | Test INT,                              | INT,   |

|                         |          | Test IFO                               | IFO    |

|                         | TIFO     | Test IF1                               | IF1    |

|                         | TIF1     | Test TF                                | TF     |

|                         | TTF      | i → Timer/Counter                      |        |

|                         | LTI      | F.                                     | -      |

|                         | LTA      | A → Timer/Counter                      |        |

|                         | LAT      | Timer/Counter → A                      |        |

|                         | RTNI     | Return Interrupt                       |        |

|                         | SED      | "1" → D (Y)                            |        |

|                         | RED      | "O" → D (Y)                            |        |

|                         | TD       | Test D (Y)                             | D (Y)  |

|                         | SEDD n   | "1" → D (n)                            |        |

| Input/Output            | REDD n   | "O" → D (n)                            |        |

| Instruction             | LAR p    | R(p) → A                               |        |

|                         | LBR p    | R(p) → B                               |        |

|                         | LRA p    | A → R(p)                               |        |

|                         | LRB p    | B → R(p)                               |        |

|                         | Рр       | Pattern Generation                     |        |

|                         | NOP      | No Operation                           |        |

# **® HITACHI**

[NOTE] 1. (XY) after a mnemonic code has four meanings as follows.

Mnemonic only Instruction execution only

Mnemonic with X

After instruction execution, X → SPX

Mnemonic with Y

After instruction execution, Y → SPY

Mnemonic with XY After instruction execution, X → SPX, Y → SPY

[Example] LAM M → A

LAMX M → A, X → SPX

LAMY M → A, Y → SPY

LAMXY M → A, Y → SPY, Y → SPY

2. Status column shows the factor which brings the Status F/F "1" under judgement instruction or instruction accompanying the judgement.

NZ ...... ALU Not Zero

C ...... ALU Overflow in Addition, that is, Carry

NB...... ALU Overflow in Subtraction, that is, No Borrow Except above...... Contents of the status column affects the Status F/F directly.

3. The Carry F/F (C(F/F)) is not always affected by executing the instruction which affects the Status F/F.

Instructions which affect the Carry F/F are eight as follows.

AMC SEC

SMC REC

DAA ROTL

DAS ROTR

4. All instructions except the pattern instruction (P) are executed in 1 cycle. The pattern instruction (P) is executed in 2 cycles.

HMCS45A Mask Option List

#### (1) I/O Option

| Pin<br>Name       |                 | I/O Option |                                                  |              | Pin              | 1/0 | I/O Option |   | Remarks |

|-------------------|-----------------|------------|--------------------------------------------------|--------------|------------------|-----|------------|---|---------|

|                   | 1/0             | Α          | В                                                | Remarks      | Name             |     | Α          | В | nemarks |

| D <sub>o</sub>    | 1/0             |            |                                                  |              | Roo              | I/O |            |   |         |

| D,                | 1/0             |            |                                                  |              | R <sub>o1</sub>  | 1/0 |            |   |         |

| D <sub>2</sub>    | 1/0             |            |                                                  |              | R <sub>02</sub>  | I/O |            |   |         |

| D <sub>3</sub>    | 1/0             |            |                                                  |              | R <sub>o3</sub>  | 1/0 |            |   |         |

| D <sub>4</sub>    | 1/0             |            |                                                  |              | R <sub>10</sub>  | 1/0 |            |   |         |

| D <sub>5</sub>    | 1/0             |            |                                                  |              | R,,              | 1/0 |            |   |         |

| D <sub>6</sub>    | 1/0             |            |                                                  |              | R,2              | 1/0 |            |   |         |

| D,                | 1/0             |            |                                                  |              | R <sub>13</sub>  | 1/0 |            |   | 1       |

| D <sub>8</sub>    | 1/0             |            |                                                  |              | R <sub>20</sub>  | 1/0 |            |   |         |

| D,                | 1/0             |            |                                                  |              | R <sub>21</sub>  | 1/0 |            |   |         |

| D <sub>10</sub>   | I/O             |            |                                                  |              | R <sub>22</sub>  | 1/0 |            |   |         |

| D <sub>11</sub>   | I/O             | ,.         |                                                  |              | R <sub>23</sub>  | 1/0 |            |   |         |

| D <sub>12</sub>   | 1/0             |            |                                                  |              | R <sub>30</sub>  | 1/0 |            |   |         |

| D <sub>13</sub>   | 1/0             |            |                                                  |              | R <sub>31</sub>  | 1/0 |            |   |         |

| D <sub>14</sub>   | 1/0             |            |                                                  |              | R <sub>32</sub>  | 1/0 |            |   |         |

| D <sub>15</sub>   | 1/0             | ******     |                                                  |              | R <sub>33</sub>  | 1/0 |            |   |         |

| - '-              |                 | · · ·      |                                                  |              | R <sub>40</sub>  | 1/0 |            |   |         |

|                   |                 |            | T                                                |              | R <sub>41</sub>  | 1/0 |            |   |         |

|                   |                 |            |                                                  |              | R <sub>42</sub>  | 1/0 |            |   |         |

|                   |                 |            |                                                  |              | R <sub>43</sub>  | 1/0 |            |   |         |

|                   |                 |            | <del>                                     </del> |              | R <sub>50</sub>  | 1/0 |            |   |         |

|                   |                 |            |                                                  |              | R <sub>5</sub> , | 1/0 |            |   |         |

|                   |                 |            |                                                  |              | R <sub>52</sub>  | 1/0 |            | 1 |         |

|                   |                 |            |                                                  |              | R <sub>53</sub>  | 1/0 |            |   |         |

| INT <sub>o</sub>  | 1               |            |                                                  |              | Reo              | 0   |            |   |         |

| INT,              | 1               |            |                                                  | _            | R <sub>e</sub> , | 0   |            |   |         |

| RESET             |                 |            |                                                  | <del> </del> | R <sub>62</sub>  | 0   |            |   |         |

| V <sub>disp</sub> | Power<br>Supply | <u> </u>   |                                                  |              | Rea              | 0   |            |   |         |

★ Specify the I/O composition with a mark of "○" in the applicable composition column.

A: High Break-down Voltage

B: With pull up MOS

\*\*The pull up MOS\*\*

\*\*The pull up

#### (2) Package

| Package |

|---------|

| FP-54   |

| DP-64S  |

★ Mark "\rightarrow" in "\sum " for the selected package.

#### (3) CPG

| CPG |                                                         |  |  |  |  |

|-----|---------------------------------------------------------|--|--|--|--|

|     | External CPG                                            |  |  |  |  |

|     | Built-in CPG (R <sub>f</sub> C <sub>f</sub> Oscillator) |  |  |  |  |

|     | Built-in CPG (Ceramic Filter Oscillator)                |  |  |  |  |

☆ Mark "\square" in "□" for the selected CPG.

### (1) HITACHI

Hitachi America Ltd. • 2210 O'Toole Ave. • San Jose, CA 95131 • (408) 435-8300

113