#### **FEATURES**

- First-in, first-out dual-port memory

- Low-power CMOS process

- · Fully asynchronous operation

- · Simultaneous read and write

- Fully expandable in depth and width

- · Access time: 20 ns

- Dependable empty, half-full, and full warning flags

- · Rate buffer applications

- Multi-processing master/slave applications

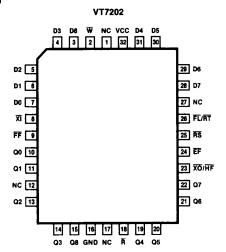

- 28-lead, 600 mil plastic DIP

- 32-lead PLCC

### DESCRIPTION

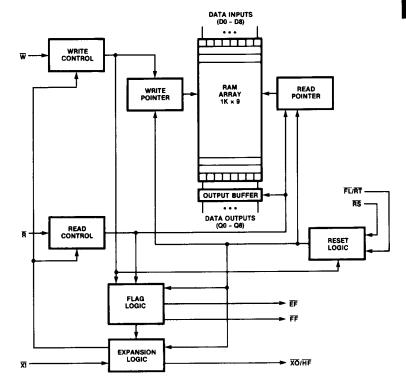

The VT7202 is a first-in, first-out (FIFO) memory that uses a high-performance static RAM array with internal logic to ensure totally asynchronous operation. Full, half-full, and empty flags are provided to allow the device to operate without external logic. The VT7202 also contains logic that allows for unlimited expansion in both word size and depth.

Although the VT7202 uses a static RAM array as its memory element, a system of read and write pointers has been included to sequence through the array. Data is toggled in and out of the device by means of the Write Enable  $(\overline{\mathbb{W}})$  and Read Enable  $(\overline{\mathbb{R}})$  signals. The VT7202

has an access time of 20 ns and a read/write cycle time of 30 ns (33 MHz). Its 1,024 × 9 organization permits the use of control or parity bits at the option of the user, and also allows a 1,024-deep word structure without the need for expansion.

1.024 × 9 FIFO MEMORY

The VT7202 is fabricated using VLSI Technology's high-performance CMOS process. Its design is ideally suited to asynchronous and simultaneous reading and writing in multi-processing and rate buffer applications. The FIFO is available in both plastic dual in-line and plastic leaded chip carrier packages.

#### **PIN DIAGRAM**

#### **BLOCK DIAGRAM**

#### **PIN DIAGRAM**

#### PIN NAMES

| Data Inputs                  |

|------------------------------|

| Data Outputs                 |

| Reset                        |

| Write Enable                 |

| Read Enable                  |

| First Load/Retransmit        |

| Expansion-In                 |

| Expansion-Out/Half-Full Flag |

| Full Flag                    |

| Empty Flag                   |

| Power (5 V)                  |

| Ground (0 V)                 |

|                              |

### **FUNCTIONAL DESCRIPTION**

The VT7202 is a first-in, first-out (FIFO) memory that is organized 1,024 words by 9 bits. It uses a high-performance static RAM as its memory array element. A system of read and write pointers sequences through the array, with data being toggled in and out by the Write Enable (W) and Read Enable (R) signals. The VT7202 can operate in one of several modes.

It should be noted that a reset cycle is required after power-on.

#### **OPERATING MODES**

# SINGLE-DEVICE MODE

When only one VT7202 is used, up to 1,024 9-bit words may be written into it and retrieved on a first-in, first-out basis. In this mode, the  $\overline{XO/HF}$  pin is a half-full flag and the Expansion-In  $(\overline{XI})$  pin should be grounded.

## WIDTH EXPANSION MODE

Word width may be expanded in 9-bit increments simply by connecting the input and output control signals to multiple devices and paralleling the

data inputs and outputs. In this mode, the flags of any one VT7202 may be used (the flag outputs should not be wired together).

# DEPTH EXPANSION MODE (DAISY CHAIN)

Multiple VT7202s can be interconnected to produce a single FIFO of greater than 1,024 words. This daisy chaining is accomplished by:

- Connecting the First-Load (FL) pin of the first FIFO to ground.

- 2. Pulling FL HIGH on all the other FIFOs.

- Connecting the Expansion-Out (XO) pin of each FIFO to the Expansion-In (XI) pin of the next FIFO. The XO pin of the last (or deepest) FIFO is connected to the XI pin of the first device (the one with FL grounded).

Externally ORing all Empty Flag (EF) pins produces a valid Empty flag. The same is true for the Full Flag (FF) pins. The Retransmit (RT) capability and Half-Full (HF) flag are not available in this mode.

## COMPOUND EXPANSION MODE

The width and depth expansion modes may be combined to produce larger FIFO arrays.

#### SIGNAL DESCRIPTIONS

# INPUTS

#### Reset (RS)

A reset cycle is required after power-on.

Holding the Reset  $(\overline{\text{RS}})$  input signal LOW for the minimum reset pulse width initiates a reset cycle, during which both the read and write pointers are moved to the first location in the FIFO memory. Immediately after the cycle, the Empty Flag  $(\overline{\text{EF}})$  is asserted (goes LOW), and the Full Flag  $(\overline{\text{FF}})$  and Half-Full Flag  $(\overline{\text{HF}})$  are disasserted (go HIGH).

Both Write Enable  $(\overline{W})$  and Read Enable  $(\overline{R})$  must be HIGH (inactive) during the reset cycle.

## Write Enable (W)

The falling edge of the Write Enable  $(\overline{W})$  signal initiates a write cycle if the Full Flag is not set. Data set-up and hold times, however, must be met relative to the rising edge of  $\overline{W}$ . Data is stored in the FIFO memory independently of any read actions.

Each write cycle increments the write pointer. When the memory becomes half full, the Half-Full Flag (HF) is asserted (goes LOW) and remains in that state until the FIFO becomes less than half full. When HF is disasserted (goes HIGH), it changes on the rising (trailing) edge of the Read Enable (R) signal.

When the VT7202 becomes full, FF is asserted and further write operations are inhibited until one or more words of data are read from the FIFO. The Full Flag is then disasserted following the next valid read cycle.

#### Read Enable (R)

The falling edge of the Read Enable (R) signal initiates a read cycle if the Empty Flag is not set. Data is read out on a first-in, first-out basis, and is not affected by concurrent write operations.

When the last word of data is read out of the FIFO,  $\overline{EF}$  is asserted (goes LOW). The Empty Flag is disasserted (goes HIGH) following the next valid write cycle. If  $\overline{R}$  has not been asserted, the data outputs are in the high-impedance state.

## Expansion-In (XI)

The Expansion-In (XI) input is used in the depth expansion mode to produce a FIFO of greater than 1,024 words. The XI pin of one device in a daisy chain configuration is connected to the Expansion-Out (XO) pin of the previous device. In single-device mode, the XI pin is grounded.

First Load/Retransmit (FL/RT)

The function of the First Load/Retransmit (FL/RT) input depends upon the device operating mode.

In depth expansion mode, the FL/RT pin is grounded on the first device to be loaded. It is pulled HIGH on all the other devices in the daisy chain, and the filling sequence for those devices is determined by the Expansion-In (XI) and Expansion-Out (XO) signals.

In single-device mode, a LOW applied to the FL/RT input resets the read pointer to the beginning of the FIFO memory so that data can be re-read. The Write Enable (W) and the Read Enable (R) inputs must be HIGH while FL/RT is low.

Data In (D0-D8)

Data inputs

#### OUTPUTS Empty Flag (EF)

The Empty Flag (EF) output is asserted (goes LOW) when the FIFO is empty. This inhibits read operations until one or more write operations are completed, or until the FIFO is set to retransmit.

Full Flag (FF)

The Full Flag (FF) output is asserted (goes LOW) when the FIFO is full. This inhibits write operations until one or more read operations are completed, or until the FIFO is reset.

# Expansion-Out/Half-Full Flag (XO/HF)

The function of the XO/HF output depends on how the device is used. In the single-device mode, the HF signal is asserted (goes LOW) when the FIFO is half full (or more). It remains in that state until the FIFO becomes less than half full. When HF is disasserted (goes HIGH), it changes on the rising (trailing) edge of the Read Enable (R) signal.

In the depth expansion mode, this pin must be connected to the Expansion-In  $(\overline{XI})$  pin of the next device. The  $\overline{XO}$  pin of the last (deepest) FIFO is connected to the  $\overline{XI}$  pin of the first FIFO. Note that the first FIFO is the one that has its First Load  $(\overline{FL})$  input grounded. This allows devices to be daisy chained. The Half-Full Flag ( $\overline{HF}$ ) is not available in multiple device mode.

#### Data Out (Q0-Q8)

Data outputs. When the Read Enable (R) signal is not asserted, Q0-Q8 are in the high-impedance state.

## **ABSOLUTE MAXIMUM RATINGS**

Storage

Temperature -65°C to +150°C

Voltage on Any Terminal

Relative to Ground -0.5 V to +7.0 V

Applied Output

Voltage -0.5 V to +7.0 V

Applied Input

Voltage

-0.5 V to + 7.0 V

**Short Circuit Current Power Dissipation**

30 mA

1.0 W

Stresses above those listed may cause permanent damage to the device. These are stress ratings only, and functional operation of this device under these or any conditions above those listed in this data sheet is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC CHARACTERISTICS TA = 0°C to +70°C, VCC = 5 V ± 10%, Note 1

| Symbol | Parameter                         | Min  | Тур | Max    | Unit | Conditions                |

|--------|-----------------------------------|------|-----|--------|------|---------------------------|

| VIH    | Input HIGH Voltage                | 2.2  |     | VCC +1 | ٧    | Note 2                    |

| VIL    | Input LOW Voltage                 | -1.0 |     | 0.8    | ٧    | Note 3                    |

| VOH    | Output HIGH Voltage               | 2.4  |     |        | V    | IOUT = −1 mA              |

| VOL    | Output LOW Voltage                |      |     | 0.4    | ٧    | iOUT = 4 mA               |

| IIL    | Input Leakage Current (Any Input) | -1   |     | 1      | μА   | 0.4 V≤VIN≤VOUT            |

| IOL    | Output Leakage Current            | -10  |     | 10     | μA   | R≥VIH, 0.4 V≤VOUT         |

| ICC1   | Power Supply Current              |      |     | 80     | mA   | Average operating current |

| ICC2   | Power Supply Current              |      |     | 8      | mA   | R = W = RS = FL = VIH     |

| ISB    | Standby Current                   |      |     | 5      | mA   |                           |

#### CAPACITANCE TA = 25°C, f = 1 MHz

| Symbol | Parameter          | Тур | Max | Unit | Conditions |

|--------|--------------------|-----|-----|------|------------|

| CIN    | Input Capacitance  | 7   | 10  | pF   |            |

| COUT   | Output Capacitance | 8   | 10  | pF   |            |

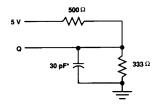

## **AC TEST CONDITIONS**

| Input Voltage Levels   | 0 V to 3 V |

|------------------------|------------|

| Input Transition Times | 5 ns       |

| Input Reference Level  | 1.5 V      |

| Output Reference Level | 1.5 V      |

| Output Load            | Figure 1   |

## **AC TESTING LOAD CIRCUIT**

FIGURE 1. OUTPUT LOAD CIRCUIT

\* INCLUDES SCOPE AND TEST JIG.

- 1. Operation across temperature range is guaranteed with 400 feet per minute of air flow.

- 2. All input pins are diode-clamped to VCC. Some testers may not have enough drive capability to reach maximum input voltage.

- 3. VIL min. is -2.0 V for pulse widths of less than 20 ns.

| Symbol  | Parameter                              | VT7202-20 |     | VT7202-35 |     | VT7202-50 |     |      |            |

|---------|----------------------------------------|-----------|-----|-----------|-----|-----------|-----|------|------------|

|         |                                        | Min       | Max | Min       | Max | Min       | Max | Unit | Conditions |

| READ CY | CLE                                    |           |     |           |     |           |     |      |            |

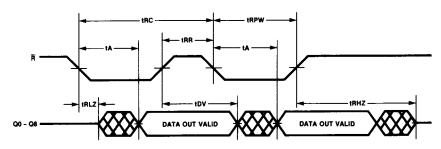

| tRC     | Read Cycle Time                        | 30        |     | 45        |     | 65        |     | ns   |            |

| tA      | Access Time                            |           | 20  |           | 35  |           | 50  | ns   |            |

| tRR     | Read Recovery Time                     | 10        |     | 10        |     | 15        |     | ns   |            |

| tRPW    | Read Pulse Width                       | 30        |     | 35        |     | 50        |     | ns   |            |

| tRLZ    | Read Pulse LOW to Data Outputs Low Z   | 5         |     | 5         |     | 10        |     | ns   | Note 2     |

| tRHZ    | Read Pulse HIGH to Data Outputs High Z |           | 15  | Ī         | 20  |           | 30  | ns   | Note 2     |

| tDV     | Data Valid from Read Pulse HIGH        | 5         |     | 5         |     | 5         |     | ns   |            |

| WRITE C | YCLE                                   |           |     |           |     |           |     |      | -          |

| tWC     | Write Cycle Time                       | 30        |     | 45        |     | 65        |     | ns   |            |

| tWR     | Write Recovery Time                    | 10        |     | 10        |     | 15        |     | ns   |            |

| tWPW    | Write Pulse Width                      | 20        |     | 35        |     | 50        |     | ns   | Note 2     |

| tDS     | Data Set-Up Time                       | 10        |     | 18        |     | 30        |     | ns   |            |

| tDH     | Data Hold Time                         | 0         |     | 0         |     | 5         |     | ns   |            |

## **TIMING DIAGRAMS**

## READ CYCLE

## WRITE CYCLE

- 1. Timing referenced as in "AC Test Conditions."

- 2. Values guaranteed by design; not currently tested.

| TIMING CHARACTERISTICS TA | A = 0°C to +70°C, VCC = 5 V ± 10%, Note 1 |

|---------------------------|-------------------------------------------|

|---------------------------|-------------------------------------------|

| Symbol  | Parameter                | VT72 | VT7202-20 |     | VT7202-35 |     | 02-50 |          |            |

|---------|--------------------------|------|-----------|-----|-----------|-----|-------|----------|------------|

|         |                          | Min  | Max       | Min | Max       | Min | Max   | Unit     | Conditions |

| RESET C | CYCLE, Note 2            |      |           |     |           |     | •     |          |            |

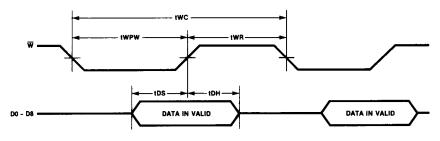

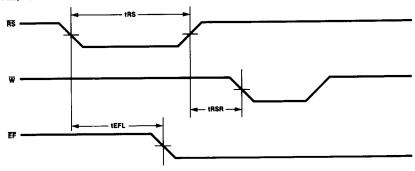

| tRSC    | Reset Cycle Time         | 30   |           | 45  |           | 65  |       | ns       |            |

| tRS     | Reset Pulse Width        | 20   | Ι         | 35  |           | 50  |       | ns       |            |

| tRSR    | Reset Recovery Time      | 10   |           | 10  |           | 15  |       | ns       |            |

| tEFL    | Reset to Empty Flag LOW  |      | 20        |     | 45        |     | 65    | ns       |            |

| RETRAN  | SMIT CYCLE               |      |           |     |           |     |       | <u> </u> |            |

| tRTC    | Retransmit Cycle Time    | 30   |           | 45  |           | 65  |       | ns       |            |

| tRT     | Retransmit Pulse Width   | 20   |           | 35  |           | 50  |       | ns       |            |

| tRTR    | Retransmit Recovery Time | 10   |           | 10  |           | 15  |       | ns       |            |

## **TIMING DIAGRAMS**

## **RESET CYCLE, Note 2**

#### RETRANSMIT CYCLE

- 1. Timing referenced as in "AC Test Conditions."

- 2.  $\overline{W}$  and  $\overline{R} = VIH$  during reset.

## TIMING CHARACTERISTICS TA = 0°C to +70°C, VCC = 5 V ±10%, Note 1

| Symbol   | Parameter             | VT72 | VT7202-20 |     | VT7202-35 |     | VT7202-50 |      | Ì          |

|----------|-----------------------|------|-----------|-----|-----------|-----|-----------|------|------------|

|          |                       | Min  | Max       | Min | Max       | Min | Max       | Unit | Conditions |

| FLAG TII | MING                  |      |           |     |           |     |           |      |            |

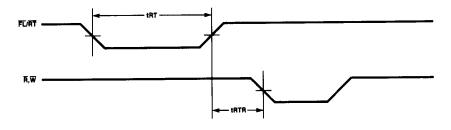

| tEFL     | Reset to EF LOW       |      | 25        |     | 45        |     | 65        | ns   |            |

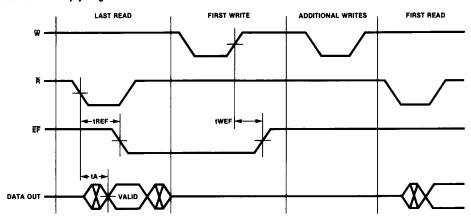

| tREF     | Read LOW to EF LOW    |      | 20        |     | 30        |     | 45        | ns   | _          |

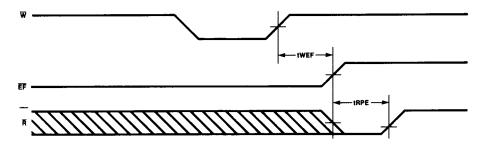

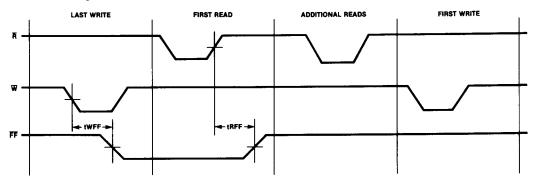

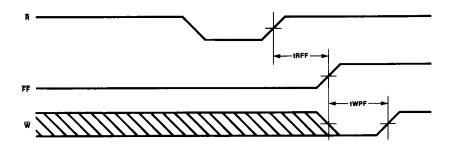

| tRFF     | Read HIGH to FF HIGH  |      | 20        |     | 30        |     | 45        | ns   |            |

| tWEF     | Write HIGH to EF HIGH |      | 20        |     | 30        |     | 45        | ns   |            |

| tWFF     | Write LOW to FF LOW   |      | 20        |     | 30        |     | 45        | ns   |            |

| tWHF     | Write LOW to HF LOW   |      | 25        |     | 45        |     | 65        | ns   |            |

| tRHF     | Read HIGH to HF HIGH  |      | 25        |     | 45        |     | 65        | ns   |            |

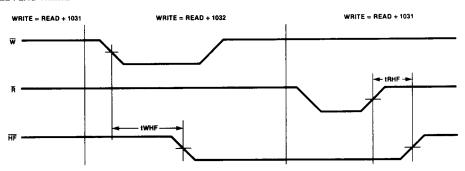

## **TIMING DIAGRAMS**

## EMPTY FLAG TIMING: Empty Flag from Last Read to First Write

## EMPTY FLAG TIMING: Effective Read Pulse Width after EF HIGH, Note 2

- 1. Timing referenced as in "AC Test Conditions."

- 2. tRPE = tRPW.

# TIMING DIAGRAMS (Cont.)

# FULL FLAG TIMING: Full Flag from Last Write to First Read

# FULL FLAG TIMING: Effective Write Pulse Width after FF HIGH (tWPF = tWPW)

#### HALF-FULL FLAG TIMING