QPSK receiver TDA8051

# **FEATURES**

- · High operating input sensitivity

- · Gain controlled amplifier

- PLL controlled carrier frequency

- · Low crosstalk between I and Q channel outputs

- 3-wire transmission bus

- 5 V supply voltage.

#### **APPLICATIONS**

• BPSK/QPSK demodulation.

# **GENERAL DESCRIPTION**

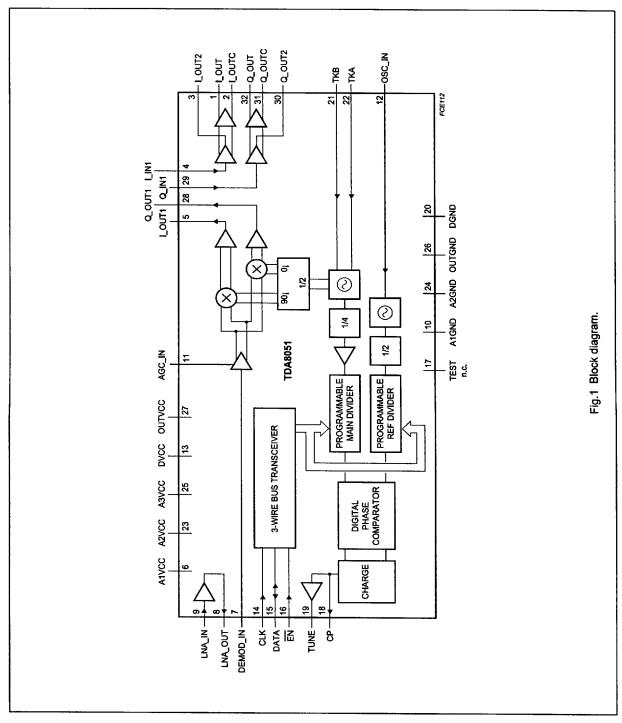

This TDA8051 is a monolithic bipolar IC intended for Quadrature Phase Shift Key (QPSK) demodulation. It includes:

- · Low noise RF and gain controlled amplifier

- Two matched mixers

- Symmetrical Voltage Controlled Oscillator (VCO) with 0 to 90° signal generator whose frequency is controlled by an integrated Phase Lock Loop (PLL) circuit.

- Two matched amplifiers for output base-band active filtering and output buffers

The gain control is produced by output level detection compared with an external pre-fixed reference. The PLL consists of:

- · Divide by four preamplifier

- 12-bit programmable main divider

- Crystal oscillator with 8-bit programmable reference divider

- Phase/frequency detector combined with charge pump to drive tuning amplifier

- 30 V output

### **QUICK REFERENCE DATA**

All AC units are RMS values unless otherwise specified.

| SYMBOL                    | PARAMETER                                                                   | MIN. | TYP. | мах. | UNIT |

|---------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>           | supply voltage range                                                        | 4.75 | 5.00 | 5.25 | V    |

| f <sub>I(LNA)</sub>       | input carrier frequency at LNA input                                        | 44   | _    | 130  | MHz  |

| V <sub>I(LNA)</sub>       | input level at LNA input                                                    | -30  | _    | 0    | dBmV |

| $\Delta\Phi_{	ext{I-Q}}$  | phase error between I and Q channels                                        | _    | ±3   | _    | deg  |

| $\Delta G_{I-Q}$          | gain error between I and Q channels                                         | _    | ±1   | _    | dB   |

| $\alpha_{\text{CT(I-Q)}}$ | crosstalk between I and Q channels                                          | _    | -30  | _    | dBc  |

| IM3                       | 3rd-order intermodulation distortion in I and Q channels (0 dBmV at LNA_IN) | _    | _    | -45  | dBc  |

| Vo                        | voltage output on pin I_OUT and Q_OUT                                       | _    | 48   | _    | dBmV |

| f <sub>step</sub>         | step at output                                                              | 50   | _    | 250  | kHz  |

| f <sub>xtal</sub>         | crystal frequency                                                           | 1    | _    | 4    | MHz  |

| T <sub>amb</sub>          | operating ambient temperature                                               | 0    | _    | 70   | °C   |

### **ORDERING INFORMATION**

| TYPE NUMBER  |      | PACKAGE                                                                 |  |  |  |  |  |  |  |

|--------------|------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1 TPE NOWBER | NAME | IE DESCRIPTION VERSION                                                  |  |  |  |  |  |  |  |

| TDA8751T     | SO32 | O32 plastic small outline package; 32 leads; body width 7.5 mm SOT287-1 |  |  |  |  |  |  |  |

1999 Aug 20

# **QPSK** receiver

TDA8051

### **BLOCK DIAGRAM**

1999 Aug 20

3

**7110826 0179887 166**

QPSK receiver TDA8051

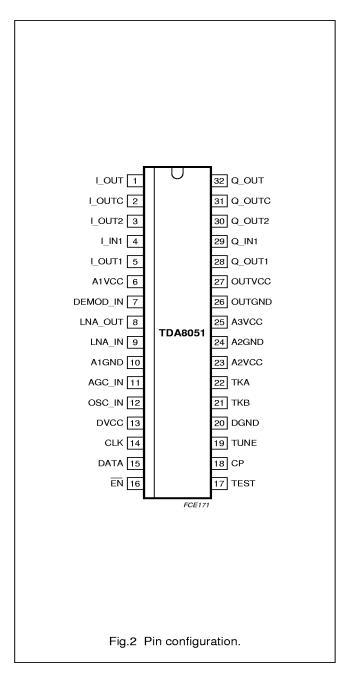

# **PINNING**

| SYMBOL   | PIN | DESCRIPTION                                   |

|----------|-----|-----------------------------------------------|

| I_OUT    | 1   | I data buffered balanced output               |

| I_OUTC   | 2   | I data buffered balanced output               |

| I_OUT2   | 3   | I data filtered output                        |

| I_IN1    | 4   | input to active filter amplifier for I data   |

| I_OUT1   | 5   | I data raw output                             |

| A1VCC    | 6   | analog supply voltage 1                       |

| DEMOD_IN | 7   | demodulator RF input                          |

| LNA_OUT  | 8   | low noise amplifier RF output                 |

| LNA_IN   | 9   | low noise amplifier RF input                  |

| A1GND    | 10  | analog ground 1                               |

| AGC_IN   | 11  | AGC control voltage input                     |

| OSC_IN   | 12  | oscillator input                              |

| DVCC     | 13  | digital supply voltage                        |

| CLK      | 14  | 3-wire bus serial control clock               |

| DATA     | 15  | 3-wire bus serial control data                |

| ĒN       | 16  | 3-wire bus serial control enable (active LOW) |

| TEST     | 17  | not connected                                 |

| СР       | 18  | charge pump output for PLL loop filter        |

| TUNE     | 19  | tuning voltage output                         |

| DGND     | 20  | digital ground                                |

| TKB      | 21  | VCO tank circuit input                        |

| TKA      | 22  | VCO tank circuit input                        |

| A2VCC    | 23  | analog supply voltage 2                       |

| A2GND    | 24  | analog ground 2                               |

| A3VCC    | 25  | analog supply voltage 3                       |

| OUTGND   | 26  | output amplifiers ground                      |

| OUTVCC   | 27  | output amplifiers supply voltage              |

| Q_OUT1   | 28  | Q data raw output                             |

| Q_IN1    | 29  | input to active filter amplifier for Q data   |

| Q_OUT2   | 30  | Q data filtered output                        |

| Q_OUTC   | 31  | Q data buffered balanced output               |

| Q_OUT    | 32  | Q data buffered balanced output               |

QPSK receiver TDA8051

### **FUNCTIONAL DESCRIPTION**

The QPSK modulated signal is applied to the input as an asymmetrical RF signal in the bandwidth 44 to 130 MHz. The spectrum extension to this waveform must be limited by a band-pass filter superseding the IC.

The RF input is either the LNA input, if the level is -30 to 0 dBmVrms, or the DEMOD input if the level is -20 to +10 dBmVrms. The amplified RF signal is then mixed with two clocks in quadrature to provide the base-band demodulated In-phase (I) and Quad-phase (Q) signals.

The VCO operates at twice the RF carrier frequency in the bandwidth 88 - 260 MHz (one octave), therefore the 0 to 90° clocks are generated by a divider by 2.

The VCO frequency can be programmed by an integrated PLL that tunes the external LC tank circuit.

The raw I and Q generated signals contain spurious spikes, therefore each signal is passed through a third order active low-pass filter (RC cell + Sallen-Key structure), whose cut-off frequency is set by external components. The filtered I and Q data signals are then amplified to provide balanced buffer outputs.

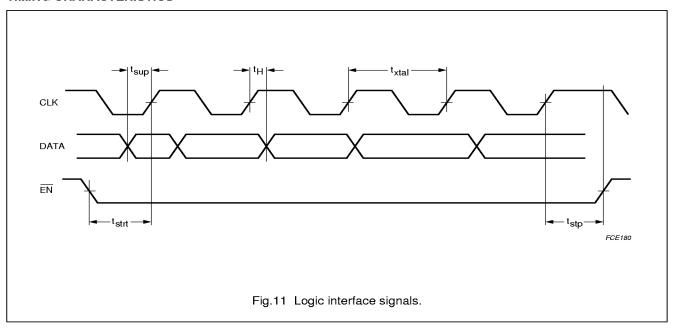

The data sent to the PLL is loaded in bursts, framed by signal  $\overline{EN}$ . Programming clock edges, together with their relevant data bits, are ignored until  $\overline{EN}$  becomes active (LOW). The internal latches are updated with the latest programming data when  $\overline{EN}$  returns to inactive (HIGH). The last 14 bits only are retained within the programming register. No check is made on the number of clock pulses received while programming is enabled. An active clock edge causing a shift of the data bits is generated when  $\overline{EN}$  goes HIGH while CLOCK is still LOW. The main divider ratio and the reference divider ratio are provided via the serial bus (see Table 1).

#### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL                | PARAMETER                                      | MIN. | мах.            | UNIT |

|-----------------------|------------------------------------------------|------|-----------------|------|

| V <sub>CC</sub>       | supply voltage                                 | -0.3 | 6.0             | ٧    |

| V <sub>(max)</sub>    | maximum voltage on all pins except pin 9 (5 V) | -0.3 | V <sub>CC</sub> | ٧    |

| t <sub>sc</sub>       | maximum short circuit duration on outputs      | _    | 10              | s    |

| T <sub>stg</sub>      | storage temperature                            | -40  | +150            | °C   |

| T <sub>j(max)</sub>   | maximum junction temperature                   | _    | 150             | °C   |

| T <sub>amb</sub>      | operating ambient temperature                  | 0    | 70              | °C   |

| V <sub>CC(tune)</sub> | tuning voltage supply                          | -0.3 | 30              | ٧    |

## **HANDLING**

HBM ESD: The IC pins withstand 2 kV except pin 26 (1750 V).

MM ESD: The IC pins withstand 100 V except pins 2 and 31 (75 V).

### THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 65    | K/W  |

QPSK receiver TDA8051

## **CHARACTERISTICS**

Measured in application circuit with the following conditions:  $V_{CC} = 5 \text{ V}$ ;  $T_{amb} = 25^{\circ}\text{C}$ . All AC units are RMS values, unless otherwise specified.

| SYMBOL                | PARAMETER                               | CONDITIONS                                                                 | MIN. | TYP. | MAX.       | UNIT |

|-----------------------|-----------------------------------------|----------------------------------------------------------------------------|------|------|------------|------|

| Supplies              |                                         |                                                                            | •    | •    | •          | 1    |

| V <sub>CCA1</sub>     | analog supply voltage                   |                                                                            | 4.75 | 5    | 5.25       | ٧    |

| I <sub>CCA1</sub>     | analog supply current                   |                                                                            | _    | 23   | _          | mA   |

| V <sub>CCA2</sub>     | analog supply voltage                   |                                                                            | 4.75 | 5    | 5.25       | V    |

| I <sub>CCA2</sub>     | analog supply current                   |                                                                            | _    | 18   | _          | mA   |

| V <sub>CCA3</sub>     | analog supply voltage                   |                                                                            | 4.75 | 5    | 5.25       | V    |

| I <sub>CCA3</sub>     | analog supply current                   |                                                                            | _    | 29   | _          | mA   |

| V <sub>cc(o)</sub>    | output supply voltage                   |                                                                            | 4.75 | 5    | 5.25       | ٧    |

| I <sub>cc(o)</sub>    | output supply current                   |                                                                            | _    | 17   | _          | mA   |

| $V_{CCD}$             | digital supply voltage                  |                                                                            | 4.75 | 5    | 5.25       | ٧    |

| I <sub>CCD</sub>      | digital supply current                  |                                                                            | _    | 13   | _          | mA   |

| V <sub>CC(tune)</sub> | tuning supply voltage                   |                                                                            | _    | _    | 30         | ٧    |

| Low noise             | amplifier: $R_s$ = 75 Ω/ $R_i$ = 75 Ω ι | ınless otherwise specified                                                 |      |      |            |      |

| V <sub>I(DC)</sub>    | DC input level                          | internally set                                                             | _    | 0.85 | _          | ٧    |

| Vi                    | input level                             |                                                                            | -30  | 1-   | 0          | dBmV |

| f <sub>i</sub>        | input carrier frequency                 |                                                                            | 44   | -    | 130        | MHz  |

| Ri                    | input resistance                        |                                                                            | _    | 75   | _          | Ω    |

| Ci                    | input capacitance                       |                                                                            | _    | 2.5  | _          | pF   |

| R <sub>LLNA</sub>     | input return loss                       |                                                                            | _    | -15  | _          | dB   |

| NF <sub>LNA</sub>     | noise figure                            |                                                                            | _    | 7    | 11         | dB   |

| V <sub>leak(LO)</sub> | LO leakage on pin at LNA_IN             | f <sub>N×LO</sub> = 140 – 860 MHz;<br>pin LNA_OUT connected to<br>DEMOD_IN | _    | _    | <b>–15</b> | dBmV |

|                       |                                         | f <sub>LO/2</sub> = 70 - 130 MHz;<br>pin LNA_OUT connected to<br>DEMOD_IN  | _    | -35  | -30        | dBmV |

| G <sub>LNA</sub>      | LNA gain                                | f = 100 MHz;<br>V <sub>I(LNA)</sub> = 0 dBmV                               | 8    | 10   | _          | dB   |

| Vo                    | output level                            | -                                                                          | -20  | _    | +10        | dBmV |

| $\Delta V_o$          | output flatness                         | in 1 MHz bandwidth;<br>V <sub>I(LNA)</sub> = 0 dBmV                        | _    | 0.25 | 0.5        | dB   |

|                       |                                         | 44 to 70 MHz;<br>V <sub>I(LNA)</sub> = 0 dBmV                              | _    | 0.50 | _          | dB   |

|                       |                                         | 70 to 130 MHz;<br>V <sub>I(LNA)</sub> = 0 dBmV                             | _    | 1.3  | 1.5        | dB   |

| IM3                   | 3rd-order intermodulation               | 2 carriers at +10 dBmV each<br>at pin LNA_IN<br>at 103 to 105 MHz          | -    | _    | -60        | dBc  |

1999 Aug 20

QPSK receiver TDA8051

| SYMBOL                     | PARAMETER                                             | CONDITIONS                                                                                                                                        | MIN.                 | TYP. | MAX.                 | UNIT   |

|----------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|--------|

| V <sub>o(DC)</sub>         | DC output level                                       |                                                                                                                                                   | -                    | 1.3  | _                    | V      |

| R <sub>o</sub>             | output resistance                                     |                                                                                                                                                   | _                    | 75   | _                    | Ω      |

| Quadrature                 | demodulator: $R_s = 75 \Omega/R_i = 20$               | ${f 0}$ k $\Omega$ unless otherwise spec                                                                                                          | ified                |      |                      |        |

| V <sub>I(DC)</sub>         | DC input level internally set -                       |                                                                                                                                                   | 1                    | _    | V                    |        |

| Vi                         | input level                                           |                                                                                                                                                   | -20                  | _    | +10                  | dBmV   |

| f <sub>i</sub>             | input carrier frequency                               |                                                                                                                                                   | 44                   | _    | 130                  | MHz    |

| Ri                         | input resistance                                      |                                                                                                                                                   | Ī-                   | 75   | _                    | Ω      |

| Ci                         | input capacitance                                     |                                                                                                                                                   | Ī-                   | 2.5  | _                    | pF     |

| RLi                        | input Return Loss                                     |                                                                                                                                                   | 1-                   | -12  | _                    | dB     |

| $V_{o(I-Q)}$               | output level on pin I_OUT1 or Q_OUT1                  |                                                                                                                                                   | -                    | 22   | _                    | dBmV   |

| B <sub>o(I-Q)</sub>        | output 3 dB bandwidth                                 | LO = 200 MHz;<br>RF = 100 to 130 MHz                                                                                                              | _                    | 35   | 38                   | MHz    |

| C/N                        | carrier to noise ratio at 500 kHz on pin at I_OUT1 or | $V_I = -20 \text{ dBmV};$<br>$V_{o(I \text{ and } Q)} = 22 \text{ dBmV}$                                                                          | _                    | 88   | _                    | dBc/Hz |

|                            | Q_OUT1                                                | $V_I = 10 \text{ dBmV};$<br>$V_{o(I \text{ and } Q)} = 22 \text{ dBmV}$                                                                           | _                    | 93   | _                    | dBc/Hz |

| V <sub>leak(LO)</sub>      | LO leakage on pin<br>DEMOD_IN                         | $f_{LO} = 140 \text{ to } 260 \text{ MHz};$<br>$f_{LO/2} = 70 \text{ to } 130 \text{ MHz}$                                                        | _                    | _    | <b>–15</b>           | dBmV   |

| V <sub>AGC(r)</sub>        | AGC range                                             | $f_{LO} = 200 \text{ MHz};$<br>$f_{RF} = 100.25 \text{ MHz at}$<br>-20  to  +10  dBmV;<br>$f_{BF} = 250 \text{ kHz at } 22 \text{ dBmV}$          | 30                   | _    | _                    | dB     |

| V <sub>AGC(s)</sub>        | AGC slope maximum                                     | f <sub>LO</sub> = 200 MHz;<br>f <sub>RF</sub> = 100.25 MHz at<br>-20 to +10 dBmV;<br>f <sub>BF</sub> = 250 kHz at 22 dBmV                         | _                    | 30   | -                    | dB/V   |

| V <sub>AGC</sub>           | gain control voltage at AGC_IN                        |                                                                                                                                                   | 10% V <sub>CCA</sub> | _    | 90% V <sub>CCA</sub> | V      |

| G <sub>max</sub>           | max. conversion gain                                  | f <sub>LO</sub> = 260 MHz;<br>f <sub>RF</sub> = 130.25 MHz at<br>-20 dBmV; V <sub>AGC</sub> = 4.5 V                                               | 42                   | _    | _                    | dB     |

| G <sub>min</sub>           | min. conversion gain                                  | $f_{LO}$ = 140 MHz;<br>$f_{RF}$ = 70.25 MHz at<br>10 dBmV V <sub>AGC</sub> = 0.5 V                                                                | _                    | _    | 12                   | dB     |

| $\Delta\Phi_{	extsf{I-Q}}$ | phase error between I and Q channels                  | $f_{LO}$ = 140 to 260 MHz;<br>$f_{RF}$ = 70.25 to 130.25 MHz;<br>$f_{BF}$ = 250 kHz at 22 dBmV<br>over specified input range                      | _                    | ±3   | _                    | deg    |

| ΔG <sub>I-Q</sub>          | gain error between I and Q<br>channels                | f <sub>LO</sub> = 140 to 260 MHz;<br>f <sub>RF</sub> = 70.25 to 130.25 MHz;<br>f <sub>BF</sub> = 250 kHz at 22 dBmV<br>over specified input range | _                    | ±1   | -                    | dB     |

QPSK receiver TDA8051

| SYMBOL                     | PARAMETER                                         | CONDITIONS                                                                                                                 | MIN.                      | TYP.   | MAX.        | UNIT    |

|----------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------|--------|-------------|---------|

| $\Delta\Phi_{	extsf{I-Q}}$ | phase error between I and Q channels              | $f_{LO}$ = 88 to 140 MHz;<br>$f_{RF}$ = 44.25 to 70.25 MHz;<br>$f_{BF}$ = 250 kHz at 22 dBmV<br>over specified input range | BmV                       |        | _           | deg     |

| $\Delta G_{\text{I-Q}}$    | gain error between I and Q channels               | f <sub>LO</sub> = 88 to 140 MHz;                                                                                           |                           | ±1     | _           | dB      |

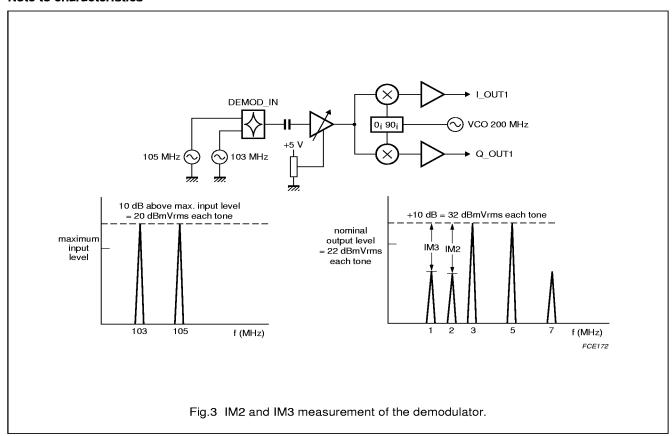

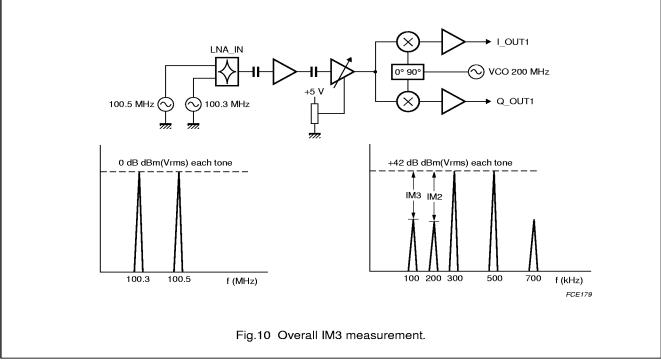

| IM3                        | 3rd-order intermodulation in I and Q channels     | see Fig.3                                                                                                                  | _                         | -      | -45         | dBc     |

| IM2                        | 2nd-order intermodulation in I and Q channels     | see Fig.3                                                                                                                  | _                         | -      | -40         | dBc     |

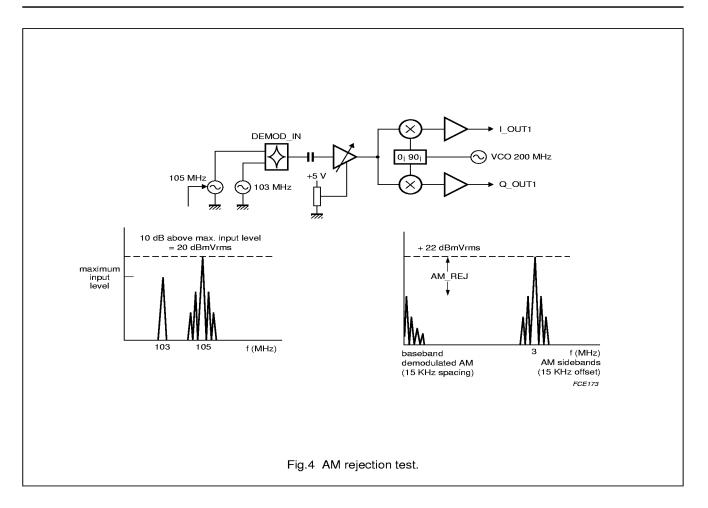

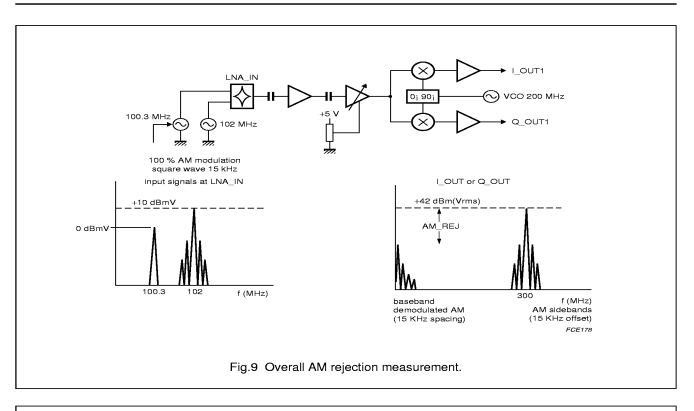

| AMREJ                      | AM rejection at I and Q channels                  | guaranteed by design;<br>see Fig.4                                                                                         | _                         | -      | -38         | dBc     |

| $\Delta V_{o(I/Q)}$        | output flatness at I and Q                        | in 1 MHz bandwidth                                                                                                         | _                         | 0.25   | _           | dB      |

| -()                        | outputs                                           | f = 40 to 70 MHz                                                                                                           | _                         | 3      | _           | dB      |

|                            |                                                   | f = 70 to 130 MHz                                                                                                          | _                         | 3      | _           | dB      |

| V <sub>o(DC)</sub>         | DC output level                                   |                                                                                                                            | _                         | 2.5    | _           | V       |

| R <sub>o</sub>             | output resistance                                 |                                                                                                                            | _                         | 400    | _           | Ω       |

| Output sect                | tion: $R_s = 400 \Omega/R_i = 4 k\Omega/R$ or     | pin I_OUT2 or Q_OUT2 = 20                                                                                                  | $\mathbf{k}\Omega$ unless | otherw | vise specif | ied     |

| V <sub>I(DC)</sub>         | DC input voltage                                  |                                                                                                                            | _                         | 3.6    | _           | V       |

| Vi                         | input level                                       |                                                                                                                            | _                         | 22     | _           | dBmV    |

| Ri                         | input resistance                                  |                                                                                                                            | _                         | 17.5   | _           | kΩ      |

| Ci                         | input capacitance                                 |                                                                                                                            | -                         | 0.4    | -           | pF      |

| G <sub>O</sub>             | gain from<br>I-Q_IN1 to I-Q_OUT2                  | f <sub>BF</sub> = 1 MHz at 22 dBmV                                                                                         | _                         | 3.8    | _           | dB      |

| $\Delta V_{o(I-Q\_out2)}$  | output flatness on                                | f <sub>BF</sub> = 0 to 1.5 MHz                                                                                             | _                         | 0.25   | _           | dB      |

|                            | pins I_OUT2 and Q_OUT2                            | f <sub>BF</sub> = 0 to 6 MHz at 22 dBmV input                                                                              | _                         | 1      | _           | dB      |

| V <sub>o(flt)</sub>        | DC output level at filter output                  |                                                                                                                            | _                         | 2.6    | _           | V       |

| R <sub>o</sub>             | output resistance                                 | f < 20 MHz                                                                                                                 | _                         | 250    | _           | Ω       |

| H <sub>2</sub>             | 2nd harmonic                                      | f <sub>BF</sub> = 1 MHz at 48 dBmV<br>output                                                                               | _                         | -40    | -35         | dBc     |

| H <sub>3</sub>             | 3rd harmonic                                      | f <sub>BF</sub> = 1 MHz at 48 dBmV<br>output                                                                               | _                         | -45    | -40         | dBc     |

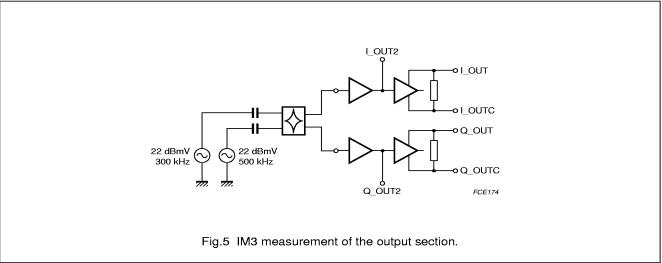

| IM3                        | 3rd-order intermodulation at pins I_OUT and Q_OUT | see Fig.5                                                                                                                  | _                         | -50    | <b>-45</b>  | dBc     |

| α <sub>CT(I-Q)</sub>       | crosstalk between I and Q channels                | f = 5 MHz; see Fig.6                                                                                                       | _                         | -40    | -30         | dBc     |

| N <sub>o</sub>             | output noise power at<br>500 kHz from carrier     | see Fig.7                                                                                                                  | _                         | -56    | _           | dBmv/Hz |

| G <sub>I-Q</sub>           | gain from<br>I-Q_IN1 to I-Q_OUT                   | f <sub>BF</sub> = 1 MHz at 22 dBmV input                                                                                   | _                         | 27     | _           | dB      |

QPSK receiver TDA8051

| SYMBOL                  | PARAMETER                                           | CONDITIONS                             | MIN. | TYP.     | MAX.       | UNIT   |

|-------------------------|-----------------------------------------------------|----------------------------------------|------|----------|------------|--------|

| V <sub>1(I-Q)</sub>     | DC output level on pin I-Q_OUT                      |                                        | -    | 3.1      | _          | V      |

| R <sub>o(dif)</sub>     | output differential resistance                      |                                        | _    | 460      | _          | Ω      |

| Overall: R <sub>s</sub> | = 75 $\Omega/R_i$ = 4 k $\Omega$ unless otherw      | vise specified                         | •    | •        | •          | •      |

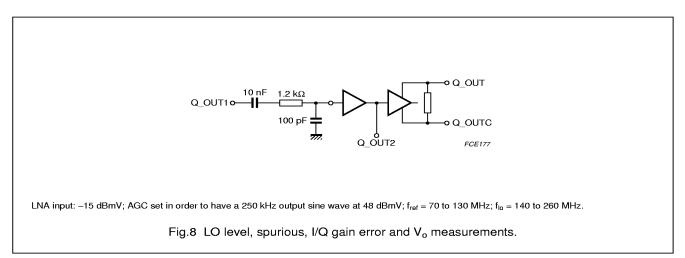

| V <sub>o</sub>          | voltage output on pins I_OUT and Q_OUT              | see Fig.8                              | -    | 48       | _          | dBmV   |

| LO <sub>lev</sub>       | LO level on pins I_OUT and Q_OUT                    | see Fig.8                              | -    | -        | -45        | dBc    |

| S <sub>o</sub>          | spurious emission on pins I_OUT and Q_OUT           | f = 0 to 5 MHz; see Fig.8              | _    | -40      | _          | dBc    |

| $\Delta G_{I-Q}$        | gain error on pins I_OUT and Q_OUT                  | see Fig.8                              | _    | ±1       | _          | dB     |

| AMR                     | AM rejection in I and Q channels                    | guaranteed by design; see<br>Fig.9     | _    | _        | -40        | dBc    |

| IM3                     | 3rd-order intermodulation                           | guaranteed by design; see<br>Fig.10    | -    | _        | <b>-45</b> | dBc    |

| Voltage Co              | ntrolled Oscillator (VCO)                           |                                        | •    | •        | •          | •      |

| f <sub>vco(min)</sub>   | min. oscillation frequency                          | note 1                                 | _    | 88       | _          | MHz    |

| f <sub>vco(max)</sub>   | max. oscillation frequency                          | note 1                                 | _    | 260      | _          | MHz    |

| αN <sub>(osc)</sub>     | oscillator phase noise                              | at 10 kHz                              | _    | -75      | _          | dBc/Hz |

|                         |                                                     | at 100 kHz                             | _    | -95      | _          | dBc/Hz |

| Phase Lock              | red Loop (PLL)                                      |                                        |      |          |            |        |

| Step                    | frequency step size                                 | at pin VCO output                      | 100  | _        | 500        | kHz    |

| RD                      | fixed reference divider ratio                       |                                        | _    | 2        | _          | _      |

| RDR                     | programmable reference divider ratio                |                                        | 2    | -        | 80         | _      |

| ND                      | programmable fix main divider ratio                 |                                        | -    | 4        | _          | _      |

| NDR                     | main divider ratio                                  |                                        | 128  | _        | 2600       | _      |

| I <sub>(CP)</sub>       | charge pump current                                 |                                        | _    | 300      | _          | μΑ     |

| Crystal osc             | illator                                             |                                        |      |          |            |        |

| f <sub>xtal</sub>       | crystal frequency                                   | $r_{xtal} = 25 \text{ to } 200 \Omega$ | 1    | _        | 4          | MHz    |

| Z <sub>i</sub>          | crystal oscillator input impedance (absolute value) | f <sub>xtal</sub> = 4 MHz              | 600  | 120<br>0 | _          | Ω      |

| V <sub>I(DC)</sub>      | DC input level                                      |                                        | _    | 2.9      | _          | V      |

| Vi                      | input level                                         |                                        | _    | 30       | _          | mVrms  |

|                         | •                                                   | -                                      |      |          |            |        |

QPSK receiver TDA8051

| SYMBOL               | PARAMETER                     | CONDITIONS           | MIN. | TYP. | MAX. | UNIT |

|----------------------|-------------------------------|----------------------|------|------|------|------|

| 3-wire bus           |                               |                      | •    |      |      | •    |

| V <sub>IL</sub>      | input Low level               | guaranteed by design | _    | _    | 0.8  | V    |

| V <sub>IH</sub>      | input High level              | guaranteed by design | 2.4  | _    | _    | ٧    |

| f <sub>clk</sub>     | clock frequency               | guaranteed by design | _    | 330  | _    | kHz  |

| t <sub>su</sub>      | input data to CLK set-up time | guaranteed by design | _    | 2    | _    | μs   |

| t <sub>h</sub>       | input data to CLK hold time   | guaranteed by design | _    | 1    | _    | μs   |

| t <sub>d(strt)</sub> | delay to rising clock edge    | guaranteed by design | _    | 3    | _    | μs   |

| t <sub>d(stp)</sub>  | delay from last clock edge    | guaranteed by design | _    | 3    | _    | μs   |

#### **Notes**

- 1. The frequency range of the receiver is 44 to 130 MHz. The local oscillator (LO) operates at twice the output frequency (88 to 260 MHz). Frequency control by varicap diodes allows a variation over one octave.

- 2. Crystal oscillator. The crystal oscillator uses a 4, 2 or 1 MHz crystal in series with a capacitor. The crystal is parallel resonant with load capacitance of 18 to 20 pF. Connection to V<sub>CC</sub> is preferred but can also be to GND.

#### Note to characteristics

QPSK receiver TDA8051

QPSK receiver TDA8051

QPSK receiver TDA8051

QPSK receiver TDA8051

# **TIMING CHARACTERISTICS**

# **DATA FORMAT**

# Table 1

| FIRST   |           |    |    |    |    |    |    |    |    |    |    |     | LAST |

|---------|-----------|----|----|----|----|----|----|----|----|----|----|-----|------|

| Data    |           |    |    |    |    |    |    |    |    |    |    |     |      |

| D11     | D10       | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | AD1 | AD0  |

| Refere  | nce ratio | •  |    |    |    |    |    |    |    |    |    |     |      |

| Х       | Х         | Х  | Х  | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 | 0   | 1    |

| Princip | al ratio  |    |    |    |    |    |    |    |    |    |    |     |      |

| P11     | P10       | P9 | P8 | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 | 1   | 1    |

# **QPSK** receiver

TDA8051

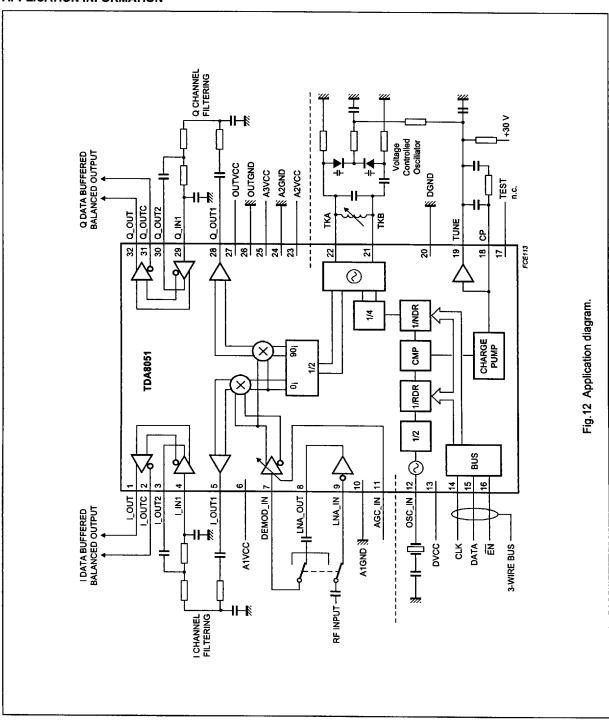

## **APPLICATION INFORMATION**

1999 Aug 20

15

**■ 7110826 0179899 988 ■**

QPSK receiver TDA8051

# **INTERNAL PIN CONFIGURATIONS**

| SYMBOL          | PIN | DESCRIPTION                            | DC VOLTAGE     |

|-----------------|-----|----------------------------------------|----------------|

| I_OUT<br>I_OUTC | 1 2 | OUTGND FCE025                          | 3.1 V<br>3.1 V |

| I_OUT2          | 3   | OUTGND FCE026                          | 2.6 V          |

| I_IN1           | 4   | OUTGND FCE027                          | 3.6 V          |

| I_OUT1          | 6   | OUTGND FCE028  Analog supply voltage 1 | 2.5 V          |

QPSK receiver TDA8051

| SYMBOL   | PIN | DESCRIPTION     | DC VOLTAGE |

|----------|-----|-----------------|------------|

| DEMOD_IN | 7   | 7 FCE127 A1GND  | 1 V        |

| LNA_OUT  | 8   | A1GND FCE128    | 1.3 V      |

| LNA_IN   | 9   | 9 A1GND FCE129  | 0.9 V      |

| A1GND    | 10  | analog ground 1 | 0. V       |

| AGC_IN   | 11  | 11 FCE030       | _          |

QPSK receiver TDA8051

| SYMBOL | SYMBOL PIN DESCRIPTION |                        | DC VOLTAGE |  |  |

|--------|------------------------|------------------------|------------|--|--|

| OSC_IN | 12                     | DVCC<br>FCE031         | 3.0 V      |  |  |

| DVCC   | 13                     | digital supply voltage | 5 V        |  |  |

| ССК    | 14                     | 14 FCE032              | n.a.       |  |  |

| DATA   | 15                     | (5) FCE033             | n.a.       |  |  |

| EN     | 16                     | 16 FCE034              | n.a.       |  |  |

| TEST   | 17                     | not connected          | n.a.       |  |  |

| СР     | 18                     | DOWN BY 18             | 1.9 V      |  |  |

QPSK receiver TDA8051

| SYMBOL | PIN | DESCRIPTION                      | DC VOLTAGE      |  |

|--------|-----|----------------------------------|-----------------|--|

| TUNE   | 19  | FCE036                           | V <sub>VT</sub> |  |

| DGND   | 20  | SUB 20                           | 0 V             |  |

| TKB    | 21  |                                  | 2.4 V           |  |

| TKA    | 22  | 21 A2GND FCE038                  | 2.4 V           |  |

| A2VCC  | 23  | analog DC supply voltage 2       | 5 V             |  |

| A2GND  | 24  | analog ground 2                  | 0 V             |  |

| A3VCC  | 25  | analog supply voltage 3          | 5 V             |  |

| OUTGND | 26  | DGND FCE040                      | o v             |  |

| OUTVCC | 27  | output amplifiers supply voltage | 5 V             |  |

| Q_OUT1 | 28  | OUTGND FCE041                    | 2.5 V           |  |

QPSK receiver TDA8051

| SYMBOL | PIN | DESCRIPTION          | DC VOLTAGE |

|--------|-----|----------------------|------------|

| Q_IN1  | 29  | 29<br>OUTGND FCE042  | 3.6 V      |

| Q_OUT2 | 30  | OUTGND FCE043        | 2.6 V      |

| Q_OUTC | 31  |                      | 3.1 V      |

| Q_OUT  | 32  | OUTGND OUTGND FCE044 | 3.1 V      |

QPSK receiver TDA8051

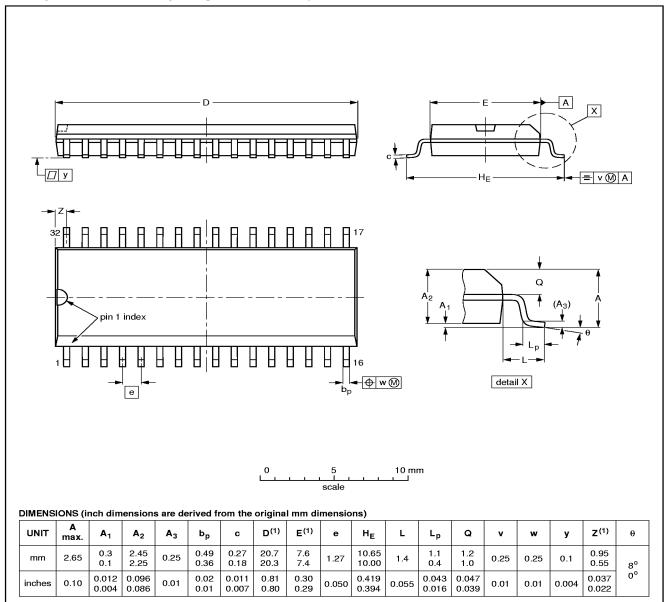

### **PACKAGE OUTLINE**

SO32: plastic small outline package; 32 leads; body width 7.5 mm

SOT287-1

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |     | REFER | ENCES | EUROPEAN   | ISSUE DATE                      |  |

|----------|-----|-------|-------|------------|---------------------------------|--|

| VERSION  | IEC | JEDEC | EIAJ  | PROJECTION | ISSUE DATE                      |  |

| SOT287-1 |     |       |       |            | <del>95-01-25</del><br>97-05-22 |  |

1999 Aug 20

QPSK receiver TDA8051

#### **SOLDERING**

### Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "Data Handbook IC26; Integrated Circuit Packages" (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering is not always suitable for surface mount ICs, or for printed-circuit boards with high population densities. In these situations reflow soldering is often used.

## Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, infrared/convection heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 230 °C.

### Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is **preferred** to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

## Manual soldering

22

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

1999 Aug 20

QPSK receiver TDA8051

## Suitability of surface mount IC packages for wave and reflow soldering methods

| PACKAGE                  | SOLDERING METHOD                  |                       |  |

|--------------------------|-----------------------------------|-----------------------|--|

| PACKAGE                  | WAVE                              | REFLOW <sup>(1)</sup> |  |

| HLQFP, HSQFP, HSOP, SMS  | not suitable <sup>(2)</sup>       | suitable              |  |

| PLCC <sup>(3)</sup> , SO | suitable                          | suitable              |  |

| LQFP, QFP, TQFP          | not recommended <sup>(3)(4)</sup> | suitable              |  |

| SQFP                     | not suitable                      | suitable              |  |

| SSOP, TSSOP, VSO         | not recommended <sup>(5)</sup>    | suitable              |  |

#### **Notes**

- 1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the "Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods".

- 2. These packages are not suitable for wave soldering as a solder joint between the printed-circuit board and heatsink (at bottom version) can not be achieved, and as solder may stick to the heatsink (on top version).

- 3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

- 5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

#### **DEFINITIONS**

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                       |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |  |  |

| Where application information is given, it is advisory and does not form part of the specification.                                                                                                                                                                                                                                                                                                                                                       |                                                                                       |  |  |

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.