**Digital Signal Processor for**

# **LR38269**

# Color CCD Cameras

#### **DESCRIPTION**

The LR38269 is a CMOS digital signal processor for color CCD camera system of 270 k/320 k-pixel CCD with complementary color filters. The camera system consists of CDS/AGC/ADC IC (IR3Y38M), DSP IC (LR38269), and V driver IC (LR36685) with CCD.

#### **FEATURES**

- Designed for 270 k/320 k color CCDs with Mg, G,

Cy, and Ye complementary color filters

- Switchable between NTSC and PAL modes

- External control interface input/output

- Variable GAMMA and KNEE response (Select one out of 4 kinds of GAMMA & KNEE response)

- 10-bit digital input

- Analog NTSC/PAL composite output by built-in 9bit 1 ch DA converter

- Built-in mirror image function

- Built-in timing generator to drive CCD

- Built-in 2 k-bit EEPROM controller to set the camera adjustment data

- Built-in auto exposure control

- Built-in auto white balance control

- Built-in auto carrier balance control

- Single + 3.3 V power supply

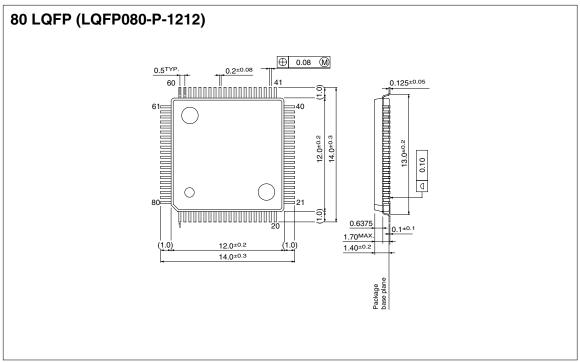

- Package:

80-pin LQFP (LQFP080-P-1212) 0.5 mm pin-pitch

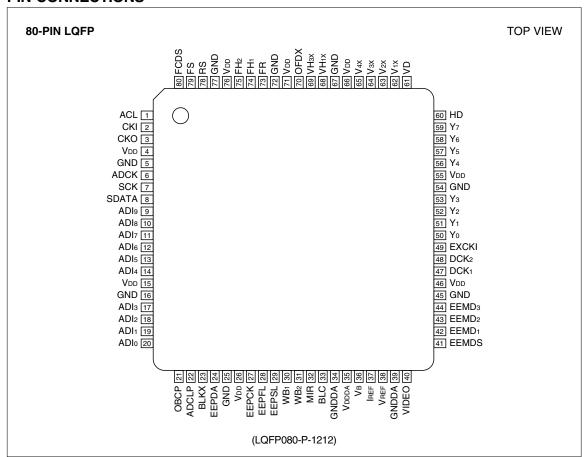

## **PIN CONNECTIONS**

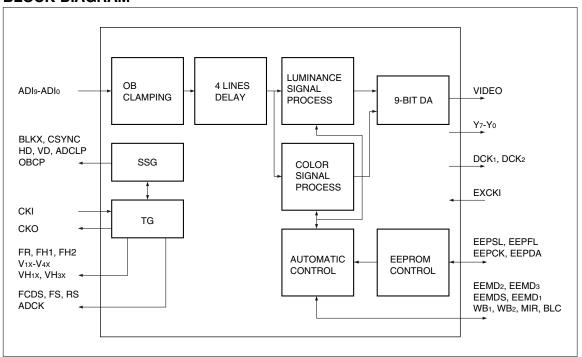

## **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| PIN NO. | SYMBOL           | I/O      | POLARITY     | DESCRIPTION                                                                        |  |  |  |  |

|---------|------------------|----------|--------------|------------------------------------------------------------------------------------|--|--|--|--|

| 1       | ACL              | IC       | Г            | nitializing input.                                                                 |  |  |  |  |

| 2       | CKI              | OSCI     |              | nput for reference clock oscillation. Connect to CKO (pin 3) with R.               |  |  |  |  |

| 3       | СКО              | osco     |              | Output for reference clock oscillation. The output is the inverse of CKI (pin 2).  |  |  |  |  |

| 4       | VDD              | _        |              | Supply of +3.3 V power.                                                            |  |  |  |  |

| 5       | GND              | _        |              | A grounding pin.                                                                   |  |  |  |  |

| 6       | ADCK             | OBF6M    |              | Clock output of AD converter, connected to pin 13 of IR3Y38M.                      |  |  |  |  |

| 7       | SCK              | OBF4M    |              | Clock output of serial data, connected to pin 16 of IR3Y38M.                       |  |  |  |  |

| 8       | SDATA            | OBF4M    | X            | Serial data output, connected to pin 19 of IR3Y38M.                                |  |  |  |  |

| 9       | ADI9             | IC       | X            | Digital signal input, fed from pin 12 of IR3Y38M (MSB).                            |  |  |  |  |

| 10      | ADI8             | IC       | X            | Digital signal input, fed from pin 11 of IR3Y38M.                                  |  |  |  |  |

| 11      | ADI7             | IC       | X            | Digital signal input, fed from pin 10 of IR3Y38M.                                  |  |  |  |  |

| 12      | ADI6             | IC       | X            | Digital signal input, fed from pin 9 of IR3Y38M.                                   |  |  |  |  |

| 13      | ADI <sub>5</sub> | IC       | X            | Digital signal input, fed from pin 8 of IR3Y38M.                                   |  |  |  |  |

| 14      | ADI4             | IC       | X            | Digital signal input, fed from pin 5 of IR3Y38M.                                   |  |  |  |  |

| 15      | VDD              | _        |              | Supply of +3.3 V power.                                                            |  |  |  |  |

| 16      | GND              | _        |              | A grounding pin.                                                                   |  |  |  |  |

| 17      | ADI3             | IC       | $  \times  $ | Digital signal input, fed from pin 4 of IR3Y38M.                                   |  |  |  |  |

| 18      | ADI <sub>2</sub> | IC       | $\times$     | Digital signal input, fed from pin 3 of IR3Y38M.                                   |  |  |  |  |

| 19      | ADI1             | IC       | $\times$     | Digital signal input, fed from pin 2 of IR3Y38M.                                   |  |  |  |  |

| 20      | ADI <sub>0</sub> | IC       | $\times$     | Digital signal input, fed from pin 1 of IR3Y38M (LSB).                             |  |  |  |  |

| 21      | OBCP             | OBF4M    |              | Optical clamp pulse output, connected to pin 32 of IR3Y38M.                        |  |  |  |  |

| 22      | ADCLP            | OBF4M    |              | Clamp pulse output, connected to pin 45 of IR3Y38M.                                |  |  |  |  |

| 23      | BLKX             | OBF4M    |              | Blanking pulse output, connected to pin 35 of IR3Y38M.                             |  |  |  |  |

| 24      | EEPDA            | IO4MU    | X            | Data input from EEPROM output pin.                                                 |  |  |  |  |

| 25      | GND              | _        |              | Supply of +3.3 V power.                                                            |  |  |  |  |

| 26      | VDD              | _        |              | A grounding pin.                                                                   |  |  |  |  |

| 27      | EEPCK            | IO4MU    |              | Clock output to EEPROM clock input pin.                                            |  |  |  |  |

| 21      | LLFOR            | 1041010  |              | This pin keeps high-impedance under high level of pin 29.                          |  |  |  |  |

| 28      | EEPFL            | IC       | $\times$     | Control pin of EEPROM. Connect to the pull-up resistor.                            |  |  |  |  |

| 29      | EEPSL            | IC       |              | Control pin of EEPROM. A pull-down resistor should be connected between pin        |  |  |  |  |

| 29      | EEFSL            | iC       |              | 29 and GND. High level of pin 29 can make data-setting from outside available.     |  |  |  |  |

|         |                  |          |              | White balance mode setting by both WB1 and WB2.                                    |  |  |  |  |

| 30      | WB <sub>1</sub>  | IO4M     |              | Pin 30 Pin 31 White balance mode                                                   |  |  |  |  |

| 30      | WDI              | 104101   |              | 0 0 AUTO                                                                           |  |  |  |  |

|         |                  |          |              | 0 1 PRESET WB1                                                                     |  |  |  |  |

|         |                  |          |              | 1 0 PRESET WB2                                                                     |  |  |  |  |

| 31      | WB2              | 10414    |              | 1 1 PRESET WB3                                                                     |  |  |  |  |

| 31      | VVD2             | NB2 IO4M |              | In digital output mode, pin 30 is assigned to bit 0 (LSB) of U/V signal and pin 31 |  |  |  |  |

|         |                  |          |              | is assigned to bit 1.                                                              |  |  |  |  |

| PIN NO. | SYMBOL            | I/O      | POLARITY | DESCRIPTION                                                                        |  |  |  |  |

|---------|-------------------|----------|----------|------------------------------------------------------------------------------------|--|--|--|--|

|         |                   |          |          | Video output mode setting.                                                         |  |  |  |  |

| 32      | MIR               | IO4M     |          | L : Normal H : Mirror                                                              |  |  |  |  |

|         |                   |          |          | In digital output mode, this pin is assigned to bit 2 of U/V signal.               |  |  |  |  |

|         |                   |          |          | Backlight compensation selection.                                                  |  |  |  |  |

| 33      | BLC               | IO4M     |          | L:OFF H:ON                                                                         |  |  |  |  |

|         |                   |          |          | In digital output mode, this pin is assigned to bit 3 of U/V signal.               |  |  |  |  |

| 34      | GNDDA             | _        |          | A grounding pin of built-in DA converter.                                          |  |  |  |  |

| 35      | VDDDA             | _        |          | Supply of +3.3 V power of built-in DA converter.                                   |  |  |  |  |

| 00      | \/n               | DAG      |          | Bias voltage output of built-in DA converter, connected to GND through a           |  |  |  |  |

| 36      | <b>V</b> в        | DAO      |          | capacitor.                                                                         |  |  |  |  |

| 37      | IREF              | DAO      |          | Bias current output of built-in DA converter, connected to GND through a resistor. |  |  |  |  |

| 38      | VREF              | DAI      |          | Bias voltage input of built-in DA converter, connected to +1.0 V power supply.     |  |  |  |  |

| 39      | GNDDA             | -        |          | A grounding pin of built-in DA converter.                                          |  |  |  |  |

| 40      | VIDEO             | DAO      |          | Analog video signal output.                                                        |  |  |  |  |

| 41      | EEMDS             | IO4MU    |          | Electronic exposure mode setting by EEMDS, EEMD1, EEMD2 and EEMD3.                 |  |  |  |  |

| 42      | EEMD <sub>1</sub> | IO4MU    |          | See "Electronic Shutter Speed Setting" in AUTOMATIC CAMERA FUNCTION                |  |  |  |  |

| 43      | EEMD2             | IO4MU    |          | CONTROL.                                                                           |  |  |  |  |

| 44      | EEMD3             | IO4MU    |          | In digital output mode, 41 to 44 pins are assigned to bits 7 to 4 of U/V signals.  |  |  |  |  |

| 45      | GND               | -        |          | A grounding pin                                                                    |  |  |  |  |

| 46      | VDD               | _        |          | Supply of +3.3 V power.                                                            |  |  |  |  |

| 47      | DCK1              | OBF4M    |          | Clock output for digital signal output.                                            |  |  |  |  |

| 47      | DON               | OBF4IVI  |          | Output mode setting switches to CSYNC output.                                      |  |  |  |  |

|         |                   |          |          | ID pulse output for U/V output signal. In digital output, this pin outputs KEI-    |  |  |  |  |

|         |                   |          |          | PULSE.                                                                             |  |  |  |  |

| 48      | DCK2              | OBF4M    |          |                                                                                    |  |  |  |  |

| 40      | DCK2              | ODI 4IVI |          | NOTE: KEI-PULSE                                                                    |  |  |  |  |

|         |                   |          |          | At power-on, it keeps low. Both 1/60 s (PAL 1/50 s) as shutter speed and AGC gain  |  |  |  |  |

|         |                   |          |          | more than data of address 78h sets it high.                                        |  |  |  |  |

|         |                   |          |          | Bit 3 of address 03h sets the function of this pin.                                |  |  |  |  |

| 49      | EXCKI             | IC       |          | 1 : Clock input of 13.5 MHz for digital output                                     |  |  |  |  |

|         |                   |          |          | 0 : VRI input for analog output                                                    |  |  |  |  |

| 50      | Y <sub>0</sub>    | OBF4M    | $\times$ | Bit 0 (LSB) of digital luminance signal output.                                    |  |  |  |  |

| 51      | Y1                | OBF4M    | $\times$ | Bit 1 of digital luminance signal output.                                          |  |  |  |  |

| 52      | <b>Y</b> 2        | OBF4M    | X        | Bit 2 of digital luminance signal output.                                          |  |  |  |  |

| 53      | <b>Y</b> 3        | OBF4M    | $\times$ | Bit 3 of digital luminance signal output.                                          |  |  |  |  |

| 54      | GND               | _        |          | A grounding pin.                                                                   |  |  |  |  |

| 55      | VDD               |          |          | Supply of +3.3 V power.                                                            |  |  |  |  |

| 56      | Y4                | OBF4M    | X        | Bit 4 of digital luminance signal output.                                          |  |  |  |  |

| 57      | <b>Y</b> 5        | OBF4M    | X        | Bit 5 of digital luminance signal output.                                          |  |  |  |  |

| 58      | Y <sub>6</sub>    | OBF4M    |          | Bit 6 of digital luminance signal output.                                          |  |  |  |  |

| PIN NO. | SYMBOL            | I/O    | POLARITY | DESCRIPTION                                                                      |

|---------|-------------------|--------|----------|----------------------------------------------------------------------------------|

| 59      | <b>Y</b> 7        | OBF4M  | X        | Bit 7 (MSB) of digital luminance signal output                                   |

|         |                   |        |          | Horizontal driving pulse output. Either CCD driving timing or BELL-PULSE is      |

|         |                   |        |          | selected by output mode setting.                                                 |

| 60      | HD                | OBF4M  | Л        |                                                                                  |

|         |                   |        |          | NOTE : BELL-PULSE                                                                |

|         |                   |        |          | Some period with high level every field.                                         |

|         |                   |        |          | Vertical driving pulse output.                                                   |

| 61      | VD                | OBF4M  | Л        | Either VD or CSYNC with either driving timing or video output timing is selected |

|         |                   |        |          | by output mode setting.                                                          |

| 62      | V <sub>1</sub> X  | OBF4M  | Л        | Vertical driving pulse output, connected to pin 20 of LR36685.                   |

| 63      | V <sub>2</sub> X  | OBF4M  | Л        | Vertical driving pulse output, connected to pin 21 of LR36685.                   |

| 64      | Vзх               | OBF4M  | $\prod$  | Vertical driving pulse output, connected to pin 18 of LR36685.                   |

| 65      | V <sub>4</sub> X  | OBF4M  | $\prod$  | Vertical driving pulse output, connected to pin 14 of LR36685.                   |

| 66      | VDD               | _      |          | Supply of +3.3 V power.                                                          |

| 67      | GND               | _      |          | A grounding pin.                                                                 |

| 68      | VH <sub>1</sub> X | OBF4M  | $\prod$  | Vertical driving pulse output, connected to pin 19 of LR36685.                   |

| 69      | VНзх              | OBF4M  | П        | Vertical driving pulse output, connected to pin 15 of LR36685.                   |

| 70      | OFDX              | OBF6M  | П        | OFD driving pulse output, connected to pin 22 of LR36685.                        |

| 71      | VDD               | _      |          | Supply of +3.3 V power.                                                          |

| 72      | GND               | _      |          | A grounding pin.                                                                 |

| 73      | FR                | OBF12M | П        | Reset pulse output, connected to CCD through a capacitor.                        |

| 74      | FH <sub>1</sub>   | OBF12M |          | Horizontal driving pulse output, connected to CCD.                               |

| 75      | FH <sub>2</sub>   | OBF12M |          | Horizontal driving pulse output, connected to CCD.                               |

| 76      | VDD               | _      |          | Supply of +3.3 V power.                                                          |

| 77      | GND               | _      |          | A grounding pin.                                                                 |

| 78      | RS                | OBF6M  |          | Sample-hold pulse output, connected to pin 31 of IR3Y38M.                        |

| 79      | FS                | OBF6M  |          | Sample-hold pulse output, connected to pin 30 of IR3Y38M.                        |

| 80      | FCDS              | OBF6M  |          | Sample-hold pulse output, connected to both pin 28 and pin 29 of IR3Y38M.        |

IC : Input pin IO4MU : Input/output pin with pull-up resistor

OBF4M

: Output pin

OSCI

: Input pin for oscillation

OBF6M

: Output pin

OSCO

: Output pin for oscillation

OBF12M

: Output pin

DAI

: Input pin for DA converter

IO4M

: Input/output pin

DAO

: Output pin for DA converter

# **INTERNAL COEFFICIENT TABLE**

| ADDRESS | NAME      | BIT | CONTENTS                                   |                |                         |  |  |

|---------|-----------|-----|--------------------------------------------|----------------|-------------------------|--|--|

| 00h     |           |     | Not used                                   |                |                         |  |  |

| 01h     |           | 7   | TV mode                                    | 0 : NTSC       | 1 : PAL                 |  |  |

|         |           | 6   | Input signal delay                         | 0 : No delay   | 1 : 1 clock cycle delay |  |  |

|         |           | 5   | Clock polarity to latch input signal       | 0 : Normal     | 1 : Inverted            |  |  |

|         | MODE 4    | 4   | YL killer                                  | 0 : Normal     | 1 : Killed              |  |  |

|         | MODE 1    | 3   | Pin mode selection (NOTE 1)                | 0 : Mode input | 1 : U/V output          |  |  |

|         |           | 2   | VD output timing selection (NOTE 1)        |                |                         |  |  |

|         |           | 1   | HD output timing selection                 | 0 : TG         | 1 : Video output        |  |  |

|         |           | 0   | DCK1 output selection (NOTE 1)             |                |                         |  |  |

| 02h     |           | 7-6 | Luminance gamma selection                  |                |                         |  |  |

|         |           | 5-4 | Color gamma selection                      |                |                         |  |  |

|         | MODE 2    | 3   | Vertical aperture enhancement              | 0 : ON         | 1 : OFF                 |  |  |

|         | MODE 2    | 2   | Horizontal aperture enhancement            | 0 : ON         | 1 : OFF                 |  |  |

|         |           | 1   | Color killer                               | 0 : ON         | 1 : OFF                 |  |  |

|         |           | 0   | Flicker reduction                          | 0 : ON         | 1 : OFF                 |  |  |

| 03h     |           | 7   | Polarity selection of SP1 and SP2          |                |                         |  |  |

|         |           | 6   | Polarity inverter of HG                    |                |                         |  |  |

|         |           | 5   | Video format selection                     | 0 : Interlace  | 1 : Non-interlace       |  |  |

|         |           | 4   | UV dot-sequence selection (output stage)   |                |                         |  |  |

|         | MODE 3    | 3   | UV dot-sequence selection                  |                |                         |  |  |

|         |           | 2   | Carrier balance tuning                     | 0 : ON         | 1 : OFF                 |  |  |

|         |           | 1   | AGC                                        | 0 : Auto       | 1 : Fixed (gain at      |  |  |

|         |           |     |                                            |                | address 1Bh)            |  |  |

|         |           | 0   | Digital output clock                       | 0:9.6 MHz      | 1 : Clock of EXCKI pin  |  |  |

| 04h     | REF_IRIS1 | 7-0 | Exposure reference level (target of exposu | ıre control)   |                         |  |  |

| 05h     | CTLD_01   | 7-0 | Higher level of exposure reference level   |                |                         |  |  |

| 06h     | CTLD_02   | 7-0 | Lower level of exposure reference level    |                |                         |  |  |

| 07h     | REF_IRIS2 | 7-0 | Exposure reference level with backlight co | mpensation     |                         |  |  |

| 08h     | UW_E1     | 7-0 | Exposure control weighting factor 1        |                |                         |  |  |

| 09h     | UW_E2     | 7-0 | Exposure control weighting factor 2        |                |                         |  |  |

| 0Ah     | UW_E3     | 7-0 | Exposure control weighting factor 3        |                |                         |  |  |

| 0Bh     | UW_E4     | 7-0 | Exposure control weighting factor 4        |                |                         |  |  |

| 0Ch     | UW_E5     | 7-0 | Exposure control weighting factor 5        |                |                         |  |  |

| 0Dh     | UW_E6     | 7-0 | Exposure control weighting factor 6        |                |                         |  |  |

| 0Eh     | UW_E7     | 7-0 | Exposure control weighting factor 7        |                |                         |  |  |

| 0Fh     | UW_E8     | 7-0 | Exposure control weighting factor 8        |                |                         |  |  |

| 10h     | CW_E      | 6-0 | Weighting factor of exposure window area   |                |                         |  |  |

| 11h     | CWP_E     | 6-0 | Top-left point of exposure window area     |                |                         |  |  |

| 12h     | CWA_E     | 6-0 | Bottom-right point of exposure window are  | a              |                         |  |  |

| ADDRESS | NAME         | BIT     | CONTENTS                                       |                    |                         |                                             |               |  |

|---------|--------------|---------|------------------------------------------------|--------------------|-------------------------|---------------------------------------------|---------------|--|

| 13h     | EE_DIV_STP   | 6-4     | Electronic shutter speed pitch                 | 111 : Quicker      |                         |                                             |               |  |

|         | LDEE E       | I DEE E | I DEE E                                        | LPFE_F             | 3-2                     | Exposure response speed selection with flic | ker reduction |  |

|         | LFFE_F       |         | 00 : Slower 01 : Normal 1                      | 0 or 11 : Quicker  |                         |                                             |               |  |

|         | LPFE_N       | 1-0     | Exposure response speed selection              |                    |                         |                                             |               |  |

|         | LFFE_IN      |         | 00 : Slower 01 : Normal 1                      | 0 or 11 : Quicker  |                         |                                             |               |  |

| 14h     | P_HEE_IRIS   | 7-0     | Maximum luminance level factor to control ex   | posure             |                         |                                             |               |  |

| 15h     | P_LEE_IRIS   | 7-0     | Minimum luminance level factor to control ex   | posure             |                         |                                             |               |  |

| 16h     | INT_PEAK     | 6       | Integrated pixels of peak signal               | 0:8 pixels         | 1:4 pixels              |                                             |               |  |

|         |              | 5       | Condition of exposure control under locking-in | n number of images | to control exposure.    |                                             |               |  |

|         | IRIS_DLY1    |         |                                                | 0 : 1 image        | 1 : Integrated 3 images |                                             |               |  |

|         | II II O_DLII | 4       | Valid image to control exposure                | 00 : Every image   |                         |                                             |               |  |

|         |              | 3       | 01 : Every 2 images 10 : Every 4 images        | 11 : Every 8 imag  | es                      |                                             |               |  |

|         |              | 2       | Condition of exposure control under free-runr  | ning               |                         |                                             |               |  |

|         | IRIS_DLY2    |         | Number of images                               | 0 : 1 image        | 1 : Integrated 3 images |                                             |               |  |

|         | II IIO_DE12  | 1       | Valid image to control exposure                | 00 : Every image   |                         |                                             |               |  |

|         |              | 0       | 01 : Every 2 images 10 : Every 4 images        | 11 : Every 8 imag  | es                      |                                             |               |  |

| 17h     | AG_DIV_STP   | 7-5     | AGC control data                               | 000 : Slower       | 111 : Quicker           |                                             |               |  |

|         | AG_GAIN      | 4-0     | Minimum pitch of AGC variable gain             |                    |                         |                                             |               |  |

|         | AG_GAIN      | 4-0     | DATA should be between 01h (finest pitch) a    | nd 1Fh.            |                         |                                             |               |  |

| 18h     |              |         | Not used                                       |                    |                         |                                             |               |  |

| 19h     | I_AGC_D8     | 7-0     | AGC gain at power-on                           |                    |                         |                                             |               |  |

| 1Ah     | REF_AGC_D8   | 7-0     | AGC reference gain (more than data of 19h)     |                    |                         |                                             |               |  |

| 1Bh     | S_38M_GA     | 7-0     | Fixed AGC gain                                 |                    |                         |                                             |               |  |

| 1Ch     | S_38M_MAX    | 2-0     | AGC maximum gain                               |                    |                         |                                             |               |  |

| 1Dh     | S_38M_OFS    | 6       | Offset control                                 | 0 : Auto           | 1 : Fixed               |                                             |               |  |

|         | 0_00111_01 0 | 5-0     | Offset data                                    |                    |                         |                                             |               |  |

| 1Eh     | CSEPR        | 7-0     | Coefficient to extract red color signal        |                    |                         |                                             |               |  |

| 1Fh     | CSEPB        | 7-0     | Coefficient to extract blue color signal       |                    |                         |                                             |               |  |

| 20h     | CB_R         | 7-0     | Red signal carrier balance                     |                    |                         |                                             |               |  |

| 21h     | CB_B         | 7-0     | Blue signal carrier balance                    |                    |                         |                                             |               |  |

| 22h     | K_T_R        | 7-0     | Basic red WB gain                              |                    |                         |                                             |               |  |

| 23h     | K_T_B        | 7-0     | Basic blue WB gain                             |                    |                         |                                             |               |  |

| 24h     | MAX_WBR      | 7-0     | Red WB gain at maximum color temperature       |                    |                         |                                             |               |  |

| 25h     | MIN_WBR      | 7-0     | Red WB gain at minimum color temperature       |                    |                         |                                             |               |  |

| 26h     | MAX_WBB      | 7-0     | Blue WB gain at minimum color temperature      |                    |                         |                                             |               |  |

| 27h     | MIN_WBB      | 7-0     | Blue WB gain red at maximum color tempera      | ature              |                         |                                             |               |  |

| 28h     | WBR1         | 7-0     | Red WB data (preset 1)                         |                    |                         |                                             |               |  |

| 29h     | WBB1         | 7-0     | Blue WB data (preset 1)                        |                    |                         |                                             |               |  |

| 2Ah     | WBR2         | 7-0     | Red WB data (preset 2)                         |                    |                         |                                             |               |  |

| 2Bh     | WBB2         | 7-0     | Blue WB data (preset 2)                        |                    |                         |                                             |               |  |

| 2Ch     | WBR3         | 7-0     | Red WB data (preset 3)                         |                    |                         |                                             |               |  |

| ADDRESS | NAME        | BIT      | CONTENTS                                                      |                                      |     |                                                 |  |  |

|---------|-------------|----------|---------------------------------------------------------------|--------------------------------------|-----|-------------------------------------------------|--|--|

| 2Dh     | WBB3        | 7-0      | Blue WB data (preset 3)                                       |                                      |     |                                                 |  |  |

| 2Eh     | K_GA_R      | 7-0      | Correction coefficient of R - Y gain                          | Correction coefficient of R - Y gain |     |                                                 |  |  |

| 2Fh     | K_GA_B      | 7-0      | Correction coefficient of B - Y gain                          |                                      |     |                                                 |  |  |

| 30h     | REF_GA_R    | 5-0      | Basic gain of R - Y signal                                    |                                      |     |                                                 |  |  |

| 31h     | REF_GA_B    | 5-0      | Basic gain of B - Y signal                                    |                                      |     |                                                 |  |  |

| 32h     | GA_R1       | 5-0      | R - Y gain data (preset 1)                                    |                                      |     |                                                 |  |  |

| 33h     | GA_B1       | 5-0      | B - Y gain data (preset 1)                                    |                                      |     |                                                 |  |  |

| 34h     | GA_R2       | 5-0      | R - Y gain data (preset 2)                                    |                                      |     |                                                 |  |  |

| 35h     | GA_B2       | 5-0      | B – Y gain data (preset 2)                                    |                                      |     |                                                 |  |  |

| 36h     | GA_R3       | 5-0      | R – Y gain data (preset 3)                                    |                                      |     |                                                 |  |  |

| 37h     | GA_B3       | 5-0      | B - Y gain data (preset 3)                                    |                                      |     |                                                 |  |  |

| 38h     | MAX_IQAREA  | 7        | AWB IQ area selection 0 : Set data                            | 1 : Widest                           |     |                                                 |  |  |

|         | L DEIO E    | I DEIO E | LDEIO E                                                       | L DEIO, E                            | 6-5 | Response speed selection with flicker reduction |  |  |

|         | LPFIQ_F     |          | 00 : Slower 01 : Normal 10 or 11 : Quicker                    |                                      |     |                                                 |  |  |

|         | LPFIQ_N     | 4-3      | Response speed                                                |                                      |     |                                                 |  |  |

|         | FINE        | 2        | Fine-tuning mode of auto white balance                        |                                      |     |                                                 |  |  |

|         | AWB_WAIT_C  | 1-0      | AWB time constant after lock-in (upper 2 bits)                |                                      |     |                                                 |  |  |

| 39h     | AWB_WAIT_C  | 7-0      | AWB time constant after lock-in (lower 8 bits)                |                                      |     |                                                 |  |  |

| 3Ah     | CMP_CT      | 7-0      | Valid data to control AWB (01h makes all AWB data valid.)     |                                      |     |                                                 |  |  |

| 3Bh     | AWB_HCL     | 7-0      | Highest luminance level to be available for AWB control       |                                      |     |                                                 |  |  |

| 3Ch     | AWB_LCL     | 7-0      | Lowest luminance level to be available for AWB control        |                                      |     |                                                 |  |  |

| 3Dh     | REF_WBPK    | 7-0      | Offset luminance level to control data of 3Bh and 3Ch         |                                      |     |                                                 |  |  |

| 3Eh     | K_CL        | 7-0      | Maximum luminance level factor to control data of 3Bh and 3Ch |                                      |     |                                                 |  |  |

| 3Fh     | K_WBCL      | 7-0      | Weighting factor for data of 3Dh and 3Eh                      |                                      |     |                                                 |  |  |

| 40h     | UW_IQ1      | 7-0      | AWB control weighting factor 1                                |                                      |     |                                                 |  |  |

| 41h     | UW_IQ2      | 7-0      | AWB control weighting factor 2                                |                                      |     |                                                 |  |  |

| 42h     | UW_IQ3      | 7-0      | AWB control weighting factor 3                                |                                      |     |                                                 |  |  |

| 43h     | UW_IQ4      | 7-0      | AWB control weighting factor 4                                |                                      |     |                                                 |  |  |

| 44h     | INT_I_R - Y | 7        | AWB control data 0 : I/Q 1 : R - Y/B - Y                      |                                      |     |                                                 |  |  |

|         | CW_IQ       | 6-0      | Weighting factor of AWB window area                           |                                      |     |                                                 |  |  |

| 45h     | CWPA_IQ     | 7-4      | Top-left point of AWB window area                             |                                      |     |                                                 |  |  |

|         | CWPA_IQ     | 3-0      | Bottom-right point of AWB window area                         |                                      |     |                                                 |  |  |

| 46h     | CTLD_AW0    | 7-0      | Exposure level to erase the area to detect white color        |                                      |     |                                                 |  |  |

| ADDRESS | NAME       | BIT | CONTENTS                                                       |                                                     |  |  |  |

|---------|------------|-----|----------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| 47h     | AWB_IP_L   | 7-0 | First AWB detector area I-PLUS NOTE:                           |                                                     |  |  |  |

| 48h     | AWB_IM_L   | 7-0 | First AWB detector area I-MINUS                                | Data to set first area should be larger than        |  |  |  |

| 49h     | AWB_QP_L   | 7-0 | First AWB detector area Q-PLUS                                 | data to set second area.                            |  |  |  |

| 4Ah     | AWB_QM_L   | 7-0 | First AWB detector area Q-MINUS                                |                                                     |  |  |  |

| 4Bh     | AWB_IP_S   | 7-0 | Second AWB detector area I-PLUS                                | Second area should be closer to the cross           |  |  |  |

| 4Ch     | AWB_IM_S   | 7-0 | Second AWB detector area I-MINUS                               | point of I-axis and Q-axis, compared to first area. |  |  |  |

| 4Dh     | AWB_QP_S   | 7-0 | Second AWB detector area Q-PLUS                                | alea.                                               |  |  |  |

| 4Eh     | AWB_QM_S   | 7-0 | Second AWB detector area Q-MINUS                               |                                                     |  |  |  |

| 4Fh     | AWB_I_WH_L | 6-0 | First AWB white zone I-PLUS                                    |                                                     |  |  |  |

| 50h     | AWB_Q_WH_L | 6-0 | First AWB white zone Q-PLUS                                    |                                                     |  |  |  |

| 51h     | AWB_I_WH_S | 6-0 | Second AWB white zone I-MINUS                                  |                                                     |  |  |  |

| 52h     | AWB_Q_WH_S | 6-0 | Second AWB white zone Q-MINUS                                  |                                                     |  |  |  |

| 53h     | K_MAT_R    | 7-0 | R - Y gain factor for color matrix correction                  | on                                                  |  |  |  |

| 54h     | K_MAT_B    | 7-0 | B - Y gain factor for color matrix correction                  | on                                                  |  |  |  |

| 55h     | REF_MAT_R  | 5-0 | Basic R - Y data of color matrix correction                    | n                                                   |  |  |  |

| 56h     | REF_MAT_B  | 5-0 | Basic B - Y data of color matrix correction                    | า                                                   |  |  |  |

| 57h     | MAT1       | 7-0 | Color matrix data (preset 1) R - Y 4 bits,                     | B – Y 4 bits                                        |  |  |  |

| 58h     | MAT2       | 7-0 | Color matrix data (preset 2) R - Y 4 bits,                     | B – Y 4 bits                                        |  |  |  |

| 59h     | MAT3       | 7-0 | Color matrix data (preset 3) R - Y 4 bits,                     | B – Y 4 bits                                        |  |  |  |

| 5Ah     | COL_S      | 7-0 | AGC gain to start suppressing color signal                     |                                                     |  |  |  |

| 5Bh     | COL_H      | 5-0 | Pitch of color signal suppressing by addre                     | ss 5Ah                                              |  |  |  |

| 5Ch     | CKI_HCL    | 7-0 | Higher luminance level to start suppressing                    | g color signal                                      |  |  |  |

| 5Dh     | CKI_LCL    | 7-0 | Lower luminance level to start suppressing                     | g color signal                                      |  |  |  |

| 5Eh     | CKI_HLGA   | 7-4 | Color signal suppression gain for higher lu                    | ıminance signal                                     |  |  |  |

|         | OIN_IILUA  | 3-0 | Color signal suppression gain for lower lur                    | minance signal                                      |  |  |  |

| 5Fh     | CKI_HLTI   | 7-4 | Highlight luminance signal position to suppress color -2 to +2 |                                                     |  |  |  |

|         | OKI_HEH    | 3-0 | Lowest luminance signal position to suppre                     | ess color -2 to +2                                  |  |  |  |

| 60h     | CKI_HECL   | 7-0 | Horizontal aperture level to start suppressi                   | ing color signal                                    |  |  |  |

| 61h     | CKI_EVCL   | 7-0 | Vertical aperture level to start suppressing                   | color signal                                        |  |  |  |

| 62h     | CKI_EGA    | 7-4 | Horizontal aperture gain to suppress color                     | signal by address 60h                               |  |  |  |

|         | ORI_LUA    | 3-0 | Vertical aperture gain to suppress color sign                  | gnal by address 61h                                 |  |  |  |

| 63h     | APT_S      | 7-0 | AGC gain to start suppressing aperture sign                    | gnal                                                |  |  |  |

| 64h     | APT_H      | 5-0 | Gain to suppress aperture signal by addre                      | ess 63h                                             |  |  |  |

| 65h     | NSUP_R     | 7-0 | R – Y signal coring level                                      |                                                     |  |  |  |

| 66h     | NSUP_B     | 7-0 | B - Y signal coring level                                      |                                                     |  |  |  |

| 67h     | CKI_IEL    | 7   | Color-killer level 0 : Unity gain 1 : 1/4 gain                 |                                                     |  |  |  |

|         | CKI_ETI    | 6-4 | Horizontal edge signal position to kill color                  | signal -2 to +2                                     |  |  |  |

|         | 5141_211   | 3-1 | Vertical edge signal position to kill color signal             |                                                     |  |  |  |

| 68h     | APT_HTIM   | 7-6 | Horizontal aperture signal position -1 to +                    | ·1                                                  |  |  |  |

|         | APT_HGA    | 5-1 | Horizontal aperture gain                                       |                                                     |  |  |  |

| ADDRESS | NAME     | BIT | CON                                                        | ITENTS                 |                     |  |  |  |

|---------|----------|-----|------------------------------------------------------------|------------------------|---------------------|--|--|--|

| 69h     | APT_HCL  | 6-0 | Horizontal aperture signal coring                          |                        |                     |  |  |  |

| 6Ah     | APT_VGA  | 4-0 | Vertical aperture gain                                     | /ertical aperture gain |                     |  |  |  |

| 6Bh     | APT_VCL  | 6-0 | Vertical aperture signal coring                            |                        |                     |  |  |  |

| 6Ch     | CBLK_LV  | 7   | CBLK level selection                                       | 0 : 00h                | 1 : 10h             |  |  |  |

|         | SETUP    | 6-1 | Set up level                                               |                        |                     |  |  |  |

| 6Dh     | VARI_Y   | 4-0 | luminance signal position                                  |                        |                     |  |  |  |

| 6Eh     | CW CTDI  | 7-0 | The following setting is available under be                | oth EEPSL = H and d    | ligital output mode |  |  |  |

|         | SW_CTRL  | 7-0 | WB1 (LSB), WB2, BACK, EEMDS, EEMD1 EEMD2, EEMD3, MIR (MSB) |                        |                     |  |  |  |

| 6Fh     | TO OFLA  | 7-5 | ADCK phase setting (6 steps per 60°)                       |                        |                     |  |  |  |

|         | TG_SEL1  | 4-2 | FS phase setting (±2 ns x 3)                               |                        |                     |  |  |  |

| 70h     | TO 0510  | 7-5 | CDS phase setting (±2 ns x 3)                              |                        |                     |  |  |  |

|         | TG_SEL2  | 4-2 | FR phase setting (±2 ns x 3)                               |                        |                     |  |  |  |

| 71h     | ENC_MUTE | 7   | Encoder muting                                             | 0 : OFF                | 1 : ON              |  |  |  |

|         | SYNC_SW  | 6   | SYNC adder                                                 | 0 : ON                 | 1 : OFF             |  |  |  |

|         | SEL_RB   | 5   | Serial digital data setting                                |                        |                     |  |  |  |

|         | OUT_GAIN | 4-0 | Gain of video output amplifier                             |                        |                     |  |  |  |

| 72h     | SYNC_LEV | 7-0 | SYNC level (80h = 40 IRE)                                  |                        |                     |  |  |  |

| 73h     | BAS_R    | 7-0 | BURST level of R - Y                                       |                        |                     |  |  |  |

| 74h     | BAS_B    | 7-0 | BURST level of B - Y                                       |                        |                     |  |  |  |

| 75h     | MUTE OUT | 7   | Muting at power-on                                         |                        |                     |  |  |  |

|         | MUTE_OUT | 6-0 | Muting period (data multiplied by 1 field p                | period)                |                     |  |  |  |

| 76h     | TEST     | 2-0 | Test data (EEPROM data must be 00h)                        |                        |                     |  |  |  |

| 77h     | VRI      | 2   | EXCKI pin function                                         | 1 : VRI function       | 0 : Clock input     |  |  |  |

|         | TEST     | 1   | Test data (EEPROM data must be 0)                          |                        |                     |  |  |  |

|         | TEST     | 0   | Test data (EEPROM data must be 0)                          |                        |                     |  |  |  |

| 78h     | KEI_AGC  | 8   | AGC gain to set KEI-PULSE high                             |                        |                     |  |  |  |

# (NOTE 1)

|         | ADDRESS |       | SIGNAL OUTPUT    |                    |             |  |

|---------|---------|-------|------------------|--------------------|-------------|--|

|         | 01      |       |                  |                    |             |  |

| Bit 3   | Bit 2   | Bit 0 | DCK1 (Pin 47)    | VD (Pin 61)        | HD (Pin 60) |  |

| DIGITAL | 1       | 0     | DCK <sub>1</sub> | VD for video out   | HD          |  |

| 1       | 0       | 0     | DCK <sub>1</sub> | VD for CCD driving | HD          |  |

|         | х       | 1     | DCK <sub>1</sub> | CSYNC              | HD          |  |

| ANALOG  | 1       | 0     | CSYNC            | VD for video out   | HD          |  |

| 0       | 0       | 0     | CSYNC            | VD for CCD driving | HD          |  |

|         | 1       | 1     | CSYNC            | VD for video out   | BELL        |  |

|         | 0       | 1     | CSYNC            | VD for CCD driving | BELL        |  |

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER            | SYMBOL | RATING                        | UNIT |

|----------------------|--------|-------------------------------|------|

| Power supply voltage | VDD    | -0.3 to +4.3                  | V    |

| Input voltage        | Vı     | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage       | Vo     | -0.3 to VDD + 0.3             | V    |

| Storage temperature  | Tstg   | -55 to +150                   | °C   |

### RECOMMENDED OPERATING CONDITIONS

| PARAMETER             | SYMBOL | MIN. | TYP. | MAX. | UNIT |

|-----------------------|--------|------|------|------|------|

| Power supply voltage  | VDD    | 3.0  | 3.3  | 3.6  | ٧    |

| Operating temperature | Topr   | -20  | +25  | +70  | ŷ    |

| Input clock frequency | fcĸ    |      | 28.6 |      | MHz  |

### **ELECTRICAL CHARACTERISTICS**

$(VDD = 3.0 \text{ to } 3.6 \text{ V}, TOPR = -20 \text{ to } +70 ^{\circ}\text{C})$

| ELLOTTIONE OTTATION    |              | (                           | (VDD = 3.0 to 3.0 V, TOPK = -20 to +70 °C) |      |         |      |      |  |

|------------------------|--------------|-----------------------------|--------------------------------------------|------|---------|------|------|--|

| PARAMETER              | SYMBOL       | CONDITIONS                  | MIN.                                       | TYP. | MAX.    | UNIT | NOTE |  |

| Input "Low" voltage    | VIL          |                             |                                            |      | 0.2 Vdd | ٧    | 4    |  |

| Input "High" voltage   | Vıн          |                             | 0.8 VDD                                    |      |         | V    |      |  |

| Input "Low" current    | lIL1         | VIN = 0 V                   |                                            | 100  |         | μΑ   | 2    |  |

| Output "Low" voltage   | VOL1         | IoL = 4 mA                  |                                            |      | 0.2 Vdd | V    | 3    |  |

| Output "High" voltage  | Voн1         | IOH = -4  mA                | 0.8 VDD                                    |      |         | V    | 3    |  |

| Output "Low" voltage   | VOL2         | IoL = 6  mA                 |                                            |      | 0.2 Vdd | V    | 4    |  |

| Output "High" voltage  | VOH2         | IOH = -6  mA                | 0.8 VDD                                    |      |         | V    | 4    |  |

| Output "Low" voltage   | VOL3         | IoL = 12 mA                 |                                            |      | 0.2 VDD | V    | 5    |  |

| Output "High" voltage  | Vонз         | IOH = −12 mA                | 0.8 VDD                                    |      |         | V    | 5    |  |

| Output "Low" voltage   | VOL4         | IoL = 3 mA                  |                                            |      | 0.2 Vdd | V    | 6    |  |

| Output "High" voltage  | <b>V</b> он4 | IOH = -2  mA                | 0.8 VDD                                    |      |         | V    | 0    |  |

| Resolution             | RES          |                             |                                            | 9    |         | bit  |      |  |

| Linearity error        | EL           | VREF = 1.0 V                |                                            |      | ±3.0    | LSB  | 7    |  |

| Differential error     | ED           | RREF= $4.8 \text{ k}\Omega$ |                                            |      | ±1.0    | LSB  | ′    |  |

| Full scale current     | IFS          | Rout = 75 $\Omega$          |                                            | 13   |         | mA   |      |  |

| Reference voltage      | VREF         |                             |                                            | 1.0  |         | V    | 8    |  |

| Reference resistance   | RREF         |                             |                                            | 4.8  |         | kΩ   | 9    |  |

| Output load resistance | Rout         |                             |                                            | 75   |         | Ω    | 7    |  |

#### NOTES:

- 1. Applied to inputs (IC, IO4M, IO4MU).

- 2. Applied to input (IO4MU).

- 3. Applied to outputs (OBF4M, IO4M, IO4MU).

- 4. Applied to output (OBF6M).

- 5. Applied to output (OBF12M).

- 6. Applied to output (OSCO).

- 7. Applied to output (VIDEO).

- 8. Applied to input (VREF).

- 9. Applied to output (IREF).

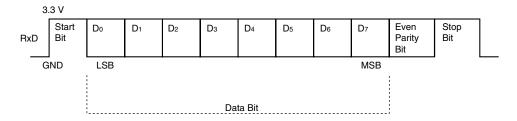

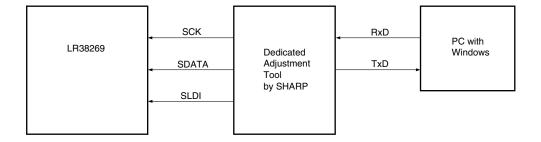

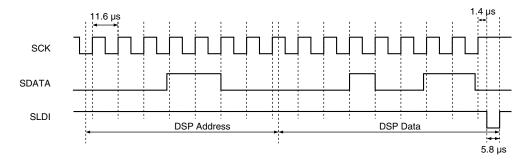

## **Data Interface**

### (1) Format of data transfers

• Format of transfers : Asynchronous (Based on

RS-232C standard)

Bit rate: 9 600 bpsData length: 8 bits

• Parity check: 1 even parity bit

Start bit : 1 bitStop bit : 1 bit

• Signal voltage level (CMOS)

## • System configuration

# AUTOMATIC CAMERA FUNCTION CONTROL

## **Automatic Electronic Exposure Control**

Electronic shutter speed is controlled so that the exposure control data approach to the data of address 04h.

Under BLC mode, the data of address 07h is available instead of address 04h.

After the exposure control data is less than the data of address 05h, an electronic shutter speed is hold. And then AGC gain is controlled so that the

exposure control data will be less than the data of address 06h.

In the case of coming more than the data of address 07h, exposure control starts again.

## **Electronic Shutter Speed Setting**

By either hardware or coefficient data, electronic shutter speed below is selectable.

| EEMDC  | EEMDS EEMD1 |       | EEMD3               | ELECTRONIC SHUTTER SPEED |                     |  |

|--------|-------------|-------|---------------------|--------------------------|---------------------|--|

| EEMIDS |             |       |                     | NTSC                     | PAL                 |  |

| 0      | 0           | 0     | 0                   | 1/60 s                   | 1/50 s              |  |

| 0      | 0           | 0     | 1                   | 1/100 s                  | 1/120 s             |  |

| 0      | 0           | 1     | 0                   | 1/250 s                  | 1/250 s             |  |

| 0      | 0           | 1     | 1                   | 1/500 s                  | 1/500 s             |  |

| 0      | 1           | 0     | 0                   | 1/1 000 s                | 1/1 000 s           |  |

| 0      | 1           | 0     | 1                   | 1/2 000 s                | 1/2 000 s           |  |

| 0      | 1           | 1     | 0                   | 1/5 000 s                | 1/5 000 s           |  |

| 0      | 1           | 1     | 1                   | 1/10 000 s               | 1/10 000 s          |  |

| 1      | 0           | 0     | 0                   | 1/20 000 s               | 1/20 000 s          |  |

| 1      | 0           | 0     | 1                   | 1/50 000 s               | 1/50 000 s          |  |

| 1      | 0           | 1     | 0                   | 1/100 000 s              | 1/100 000 s         |  |

| 1      | 0           | 1     | 1                   | 1/30 s                   | 1/25 s              |  |

| 1      | 1           | 0     | 0                   | 1/15 s                   | 1/12.5 s            |  |

| 1      | 1           | 0     | 1                   | 1/7.5 s                  | 1/6.25 s            |  |

| 4      | 4           |       | 0                   | AUTO                     | AUTO                |  |

| 1      | 1           | 1     |                     | 1/60 to 1/100 000 s      | 1/50 to 1/100 000 s |  |

|        | 1           | 1 1 1 | 4                   | AUTO                     | AUTO                |  |

| 1      |             |       | 1/60 to 1/100 000 s | 1/50 to 1/100 000 s      |                     |  |

Slower shutter speed less than 1/60 s (1/50 s of PAL) can make images whose interval is every two fields, every four fields, etc..

VD pulse is also converted to the same frequency as the output image rate.

Electronic exposure control data comes from below equation using averaged luminance levels of 64 areas in one image, made by DSP.

Electronic exposure control data =

[{Weighted data 1 ① x (64 – address 10h)

- + weighted data 2 ② x address 10h} ÷ 64

- x (256 address 14h address 15h)

- + top level 3 x address 14h

- + bottom level 4 x address 15h] ÷ 256

| Y11 | Y12 | Y13 | Y14 | <b>Y</b> 15 | Y16         | Y17         | Y18         |

|-----|-----|-----|-----|-------------|-------------|-------------|-------------|

| Y21 | Y22 | Y23 | Y24 | Y25         | Y26         | Y27         | Y28         |

| Y31 | Y32 | Y33 | Y34 | Y35         | Y36         | <b>Y</b> 37 | Y38         |

| Y41 | Y42 | Y43 | Y44 | Y45         | Y46         | Y47         | Y48         |

| Y51 | Y52 | Y53 | Y54 | Y55         | Y56         | <b>Y</b> 57 | Y58         |

| Y61 | Y62 | Y63 | Y64 | Y65         | Y66         | Y67         | Y68         |

| Y71 | Y72 | Y73 | Y74 | <b>Y</b> 75 | <b>Y</b> 76 | <b>Y</b> 77 | <b>Y</b> 78 |

| Y81 | Y82 | Y83 | Y84 | Y85         | Y86         | Y87         | Y88         |

#### 1 Weighted data 1

This comes from the following equation weighting in horizontal.

Weighting factors are the data from address 08h to address 0Fh.

$$\{(Y_{11} + Y_{12} \cdots + Y_{18}) \div 8 \text{ x address } 08h + (Y_{21} + Y_{22} \cdots + Y_{28}) \div 8 \text{ x address } 09h : + (Y_{81} + Y_{82} \cdots + Y_{88}) \div 8 \text{ x address } 0Fh\} \div 256 = Weighted data 1$$

The sum from address 08h to address 0Fh shall be 256.

## ② Weighted data 2

Weighting area can be set by the data of address 11h and address 12h. (see "NOTES" in Gamma Characteristic Option)

This comes from the following equation weighting in selected areas.

(Y<sub>33</sub> + Y<sub>34</sub> ··· + Y<sub>66</sub>)/number of areas to be selected = Weighted data 2

- ③ Top level: The highest luminance data in one image by averaging either 4 pixels or 8 pixels in horizontal.

- 4 Bottom level : The lowest luminance data in one image by averaging either 4 pixels or 8 pixels in horizontal.

#### **Auto White Balance Control**

White balance control data less than the data of address 51h and address 52h stops AWB.

White balance control data less than the data of address 4Fh and address 50h makes AWB active so that white balance control data is less than the data of address 51h and address 52h.

In the case of larger than the data of address 4Fh and address 50h, AWB will be active again.

White balance data comes from the following equation using averaged I and Q data of 16 areas in one image.

| l11         | l12         | l13 | l14         |

|-------------|-------------|-----|-------------|

| <b>l</b> 21 | l22         | l23 | l24         |

| <b>I</b> 31 | l32         | l33 | <b>l</b> 34 |

| <b>l</b> 41 | <b>l</b> 42 | l43 | <b>I</b> 44 |

| Q11 | Q12 | Q13         | Q14         |

|-----|-----|-------------|-------------|

| Q21 | Q22 | <b>Q</b> 23 | Q24         |

| Q31 | Q32 | <b>Q</b> 33 | <b>Q</b> 34 |

| Q41 | Q42 | Q43         | Q44         |

White balance data =

{Weighted data 3 ① x (64 – address 44h)

+ weighted data 4 ② x address 44h} ÷ 64

SHARP LR38269

### ① Weighted data 3

I (or Q) data comes from the following equation using the weighting data from address 40h to address 43h.

The sum from the data of address 40h to the data of address 43h shall be 256.

#### Weighted data 4

Weighting area can be selected by address 45h. (see "NOTES" in Gamma Characteristic Option.) Weighted data comes from averaged data in selected area.

#### 3 White balance area setting

The sum of I and Q can be regulated by the luminance level and the color level.

Setting target zone: address 47h to address 4Ah White balance data less than the data of address 51h and address 52h changes the target zone of auto white balance to the zone by the data from address 4Bh to 4Eh.

Above regulation comes from the following equation along the luminance level.

Setting available luminance level range :

Highest luminance level limiter =

address 3Bh + [{address 3Eh x H peak level +

(256 - address 3Eh) x exposure control data} ÷

256 - address 3Dh] x address 3Fh

Lowest luminance level limiter = address 3Ch + [{address 3Eh x H peak level + (256 - address 3Eh) x exposure control data} ÷ 256 - address 3Dh] x address 3Fh

## **Auto Color Matrix Compensation**

Color matrix compensation can be done by  $R - Y = R - Y \pm (Data \ 1 \ x \ B - Y)$   $B - Y = B - Y \pm (Data \ 2 \ x \ R - Y)$

Above data comes from below equation along the variation of color temperature.

#### Data 2 =

address 55h + {(working R white balance data – address 25h + (address 26h – working B white balance data)}  $\div$  32 x address 53h  $\div$  8

#### Data 2 =

address 56h + {(working R white balance data – address 25h) + (address 26h – working B white balance data)}  $\div$  32 x address 54h  $\div$  8

## **Auto Color Level Compensation**

Color level can be auto-controlled by the following equation along the variation of color temperature.

#### B - Y level =

address 30h + {(working R white balance data – address 25h) x address 22h + (address 26h – working B white balance data) x address 23h}  $\div$  32 x address 2Eh  $\div$  8

#### R - Y level =

address 31h + {(working R white balance data – address 25h) x address 22h + (address 26h – working B white balance data) x address 23h}  $\div$  32 x address 2Fh  $\div$  8

# Color Level Suppression Under Lower Illuminance

Working AGC gain can control both R – Y level and B – Y level by the following equation.

```

R − Y level = address 31h x {16 − (working AGC gain − address 5Ah) x address 5Bh \div 16} \div 16 B − Y level = address 30h x {16 − (working AGC gain − address 5Ah) x address 5Bh \div 16} \div 16 {16 − (working AGC gain − address 5Ah) x address 5Bh \div 16} \le 16

```

When (working AGC gain – address 5Ah)  $\leq$  0, ( ) = 0.

# Aperture Level Suppression Under Illuminance

Working AGC gain can control both the horizontal aperture level and the vertical aperture level by the following equation.

```

Horizontal aperture level = address 68h x {16 - (working AGC gain - address 63h) x address 64h ÷ 16} ÷ 16

Vertical aperture level = address 6Ah x {16 - (working AGC gain - address

```

{16 - (working AGC gain - address 63h) x address  $64h \div 16$ }  $\leq 16$

63h) x address  $64h \div 16$ } ÷ 16

When (working AGC gain – address 63h)  $\leq$  0, ( ) = 0.

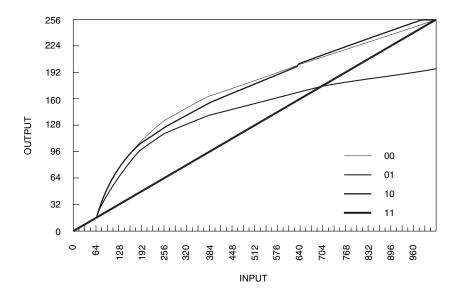

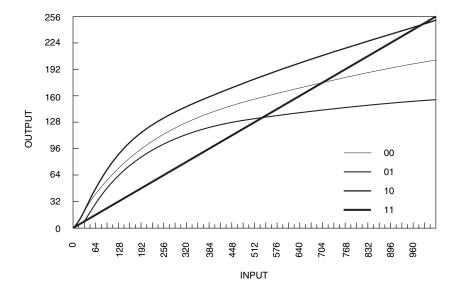

## **Gamma Characteristic Option**

(1) Luminance Signal Gamma Option

Bit 7 and bit 6 of address 02h can select one out of 4 responses below.

(2) Color Signal Gamma Option Bit 5 and bit 4 of address 02h can select one out of 4 responses below.

#### **NOTES:**

• Weighting position of auto electronic exposure control (address 11h)

| 00h | 08h | • | 30h | 38h |

|-----|-----|---|-----|-----|

| 01h | 09h | • | 31h | 39h |

|     | •   | • | •   | •   |

| 06h | 0Eh | • | 36h | 3Eh |

| 07h | 0Fh | • | 37h | 3Fh |

• Weighting area of auto electronic exposure control (address 12h)

| 00h | 08h | • | 30h | 38h |

|-----|-----|---|-----|-----|

| 01h | 09h | • | 31h | 39h |

|     | •   | • | •   | •   |

| 06h | 0Eh | • | 36h | 3Eh |

| 07h | 0Fh | • | 37h | 3Fh |

• Weighting position of auto white balance control (address 45h)

| 00h | 04h | 08h | 0Ch |

|-----|-----|-----|-----|

| 01h | 05h | 09h | 0Dh |

| 02h | 06h | 0Ah | 0Eh |

| 03h | 07h | 0Bh | 0Fh |

• Weighting area of auto white balance control (address 45h)

| 00h | 04h | 08h | 0Ch |

|-----|-----|-----|-----|

| 01h | 05h | 09h | 0Dh |

| 02h | 06h | 0Ah | 0Eh |

| 03h | 07h | 0Bh | 0Fh |

PACKAGE (Unit: mm)