No. **※ 4251**

LC78865M

16-bit A/D Converter

**Preliminary**

## **OVERVIEW**

The LC78865M is a 16-bit single-channel CMOS A/D converter designed for digital audio applications. It uses the charge re-distribution successive approximation conversion technique.

#### **FEATURES**

- Single-channel 16-bit A/D converter with microcontroller interface

- Uses the charge re-distribution successive approximation conversion technique

- · LSB-first, offset-binary output data format

- · On-chip sample-and-hold

- Single +5 V supply

- · CMOS process

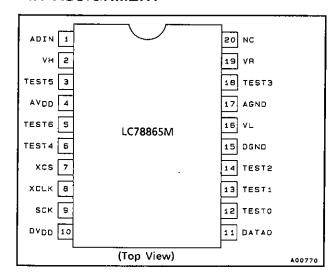

# PIN ASSIGNMENT

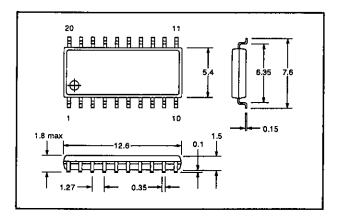

### PACKAGE DIMENSIONS

Unit: mm

# 3036B-MFP20

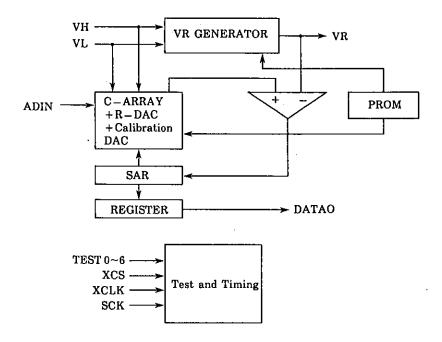

# **BLOCK DIAGRAM**

# PIN DESCRIPTION

| Name | Number           | Description                                                                                                                                  |

|------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | ADIN             | Analog input                                                                                                                                 |

| 2    | VH               | HIGH-level reference voltage                                                                                                                 |

| 3    | TEST5            | Test pin. This pin has internal pull-up. Leave open for normal operation.                                                                    |

| 4    | AV <sub>DD</sub> | Analog supply voltage                                                                                                                        |

| 5    | TEST6            | Test pin. Connect to digital ground for normal operation.                                                                                    |

| 6    | TEST4            | Test pin. Connect to digital ground for normal operation.                                                                                    |

| 7    | XCS              | Data control pin. When XCS is LOW, the last-converted data is output on the DATAO pin. This pin is normally controlled by a microcontroller. |

| 8    | XCLK             | Data transfer clock input                                                                                                                    |

| 9    | SCK              | System clock input                                                                                                                           |

| 10   | DV <sub>DD</sub> | Digital supply                                                                                                                               |

| 11   | DATAO            | Digital output data. This pin is high-impedance when XCS is HIGH.                                                                            |

| 12   | TEST0            | Test pin. Connect to digital ground for normal operation.                                                                                    |

| 13   | TEST1            | Test pin. Connect to digital ground for normal operation.                                                                                    |

| 14   | TEST2            | Test pin. Connect to digital ground for normal operation.                                                                                    |

| 15   | DGND             | Digital ground                                                                                                                               |

| 16   | VL               | LOW-level reference voltage                                                                                                                  |

| 17   | AGND             | Analog ground                                                                                                                                |

| 18   | TEST3            | Test pin. Leave open for normal operation.                                                                                                   |

| 19   | VR               | Reference voltage output. The voltage on this pin is equal to $(V_H + V_L)/2$ . Leave it open for normal operation.                          |

| 20   | NC               | No connection                                                                                                                                |

### **SPECIFICATIONS**

# **Absolute Maximum Ratings**

$T_{\bullet} = 25$  °C,  $V_{SS} = 0$  V

| Parameter             | Symbol           | Rating                   | Unit |  |

|-----------------------|------------------|--------------------------|------|--|

| Supply voltage        | V <sub>DD</sub>  | -0.3 to 7.0              | V    |  |

| Input voltage         | V <sub>IN</sub>  | $-0.3$ to $V_{DO}$ + 0.3 | V    |  |

| Output voltage        | V <sub>out</sub> | $-0.3$ to $V_{DD}$ + 0.3 | ٧    |  |

| Operating temperature | Торг             | -20 to 75                | °C   |  |

| Storage temperature   | T <sub>stg</sub> | -40 to 125               | °C   |  |

# Recommended DC Operating Conditions

$T_a = 25$  °C,  $V_{SS} = 0$  V

| Parameter                    | Symbol           | Rating         |       |                 | Unit |

|------------------------------|------------------|----------------|-------|-----------------|------|

| roidiletti                   |                  | min            | typ _ | max             | Onit |

| Supply voltage               | V <sub>DD</sub>  | 4.5            | 5.0   | 5.5             | ٧    |

| HIGH-level reference voltage | V <sub>H</sub>   | 3.3            | _     | V <sub>DD</sub> | ٧    |

| LOW-level reference voltage  | V <sub>L</sub>   | 0              | -     | 1.2             | V    |

| Analog input voltage         | V <sub>AIN</sub> | V <sub>L</sub> | -     | V <sub>H</sub>  | ٧    |

# **DC Electrical Characteristics**

$T_a$  = -20 to 75 °C,  $V_{DD}$  = 4.5 to 5.5 V,  $V_{SS}$  = 0 V

| Parameter                 | Symbol          | Condition                     | Rating                 |     |                         | 1324            |

|---------------------------|-----------------|-------------------------------|------------------------|-----|-------------------------|-----------------|

|                           |                 |                               | min -                  | typ | max                     | Unit            |

| HIGH-level input voltage  | VIH             | All digital inputs except SCK | 2.2                    | _   | -                       | ٧               |

| LOW-level input voltage   | V <sub>IL</sub> | All digital inputs except SCK | -                      | -   | 0.8                     | ٧               |

| HIGH-level output voltage | Voh             | l <sub>OH</sub> = -1 μA       | V <sub>DD</sub> - 0.05 | -   | -                       | V               |

| LOW-level output voltage  | Vol             | loL = 1 μA                    | -                      | =   | V <sub>SS.</sub> + 0.05 | ٧               |

| Clock input pulsewidth    | tsck            | SCK pin                       | 0.5                    | _   | -                       | V <sub>PP</sub> |

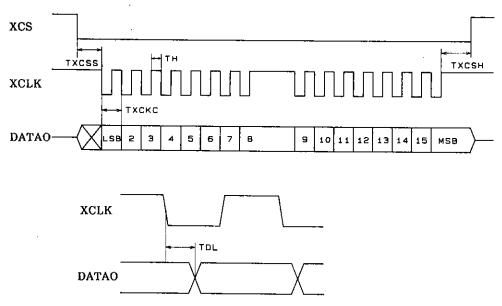

### **AC** Characteristics

$T_{a}$  = -20 to 75 °C,  $V_{\text{DD}}$  = 4.5 to 5.5 V,  $V_{\text{SS}}$  = 0 V

| Parameter           | Symbol Symbol | Conditions |     | 11-14 |     |      |

|---------------------|---------------|------------|-----|-------|-----|------|

|                     |               |            | min | typ   | max | Unit |

| XCS setup time      | Txcss         |            | 1.5 |       | _   | μs   |

| XCS hold time       | Txcsh         | -          | 1.5 | -     | -   | μs   |

| XCLK cycle time     | Тхскс         |            | 1.0 | -     | -   | μs   |

| XCLK pulsewidth     | ТН            |            | 300 | -     | -   | ns   |

| DATAO delay time    | TDL           | - "        | 0   | -     | 150 | ns   |

| SCK clock frequency | FSCK          |            | 5   | 14.32 | 16  | MHz  |

# **Analog Characteristics**

$T_{\text{\tiny 4}}$  = 25 °C,  $AV_{DD}$  =  $DV_{DD}$  = 5.0 V,  $V_{H}$  = 5.0 V,  $V_{L}$  = 0 V

| Parameter                | Symbol | Condition | Rating |      |       | IIula |

|--------------------------|--------|-----------|--------|------|-------|-------|

|                          |        |           | mln    | typ  | max   | Unit  |

| A/D conversion frequency | fs     | See note. | 17.4   | 49.7 | 55.6  | kHz   |

| Linearity                | LE     |           | -      | -    | 0.025 | %     |

| Power consumption        | PD     |           | -      | 70   | 130   | mW    |

#### Note

One conversion takes 288 SCK cycles. After conversion, the whole output word is loaded into the output register. Thus, while XCS is HIGH, the output register is updated every 288 SCK cycles. When XCS goes LOW, output register update is inhibited and preparation for output takes place.

#### Input Impedance

$$AV_{DD} = DV_{DD} = 5.0 \text{ V}, V_{H} = 5.0 \text{ V}, V_{L} = 0 \text{ V}$$

| Parameter       | Symbol | Condition                                | Rating |     |     | Unit |

|-----------------|--------|------------------------------------------|--------|-----|-----|------|

|                 |        |                                          | mln    | typ | max | Unit |

| Input impedance | ADIN   | DC input,<br>Sampling rate = 49.7 kHz    | 5      | _   | _   | ΜΩ   |

| - inpoduto      |        | 1 kHz AC input, Sampling rate = 49.7 kHz | 250    | _   | -   | kΩ   |

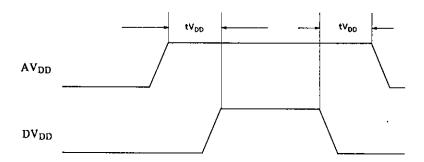

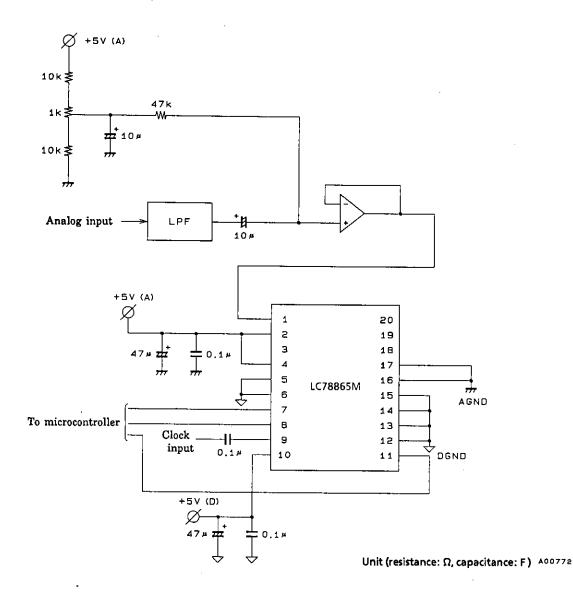

#### SUPPLY TIMING

The analog and digital supply lines,  $AV_{DD}$  and  $DV_{DD}$ , are completely independent. The ground lines, AGND and DGND, should be connected together on the circuit board. The two supply lines should power-up and

power-down at exactly the same time. At worst, the digital supply line can come up two or three milliseconds behind the analog line, but never before it. The reverse applies on power-down.

A00768

#### TIMING DIAGRAM

A00769

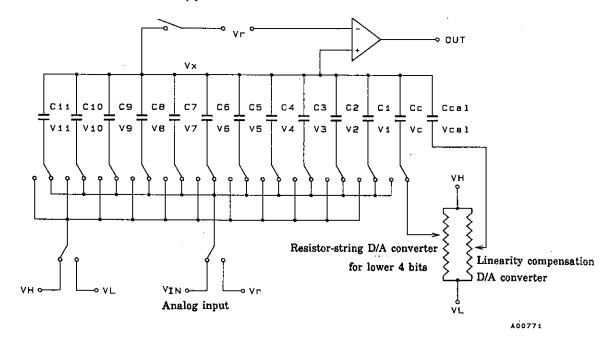

# THE CONVERSION TECHNIQUE

The LC78865M uses the charge re-distribution successive approximation technique. It includes a capacitive charge accumulator for the upper 12 bits, a resistor string DAC for the lower four bits, and a linearity compensation resistor string DAC.

The converter works by accumulating a charge proportional to the input voltage in the accumulation capacitors. The voltage produced is compared with the reference voltages. Each bit of the output word is determined sequentially, from most-significant to least-significant. The charge accumulation capacitors also function as a sample-and-hold circuit. The device

operates from a single supply voltage using a virtual earth voltage, Vr, halfway between the two reference voltages. The successive approximation comparisons use a signed-magnitude comparision with Vr as the reference

The resolution of the successive approximation technique described above is limited by the accuracy of the internal reference, Vr, and the accumulation capacitors. Errors caused by these effects are measured at the factory for each device, and the error characteristic stored in internal PROM. The data from the PROM is used to drive the linearity compensation D/A converter.

# Charge Accumulation Successive Approximation Converter

# **APPLICATION CIRCUIT**

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.