# TBA920 · TBA920S

# TELEVISION HORIZONTAL OSCILLATORS

FAIRCHILD LINEAR INTEGRATED CIRCUIT

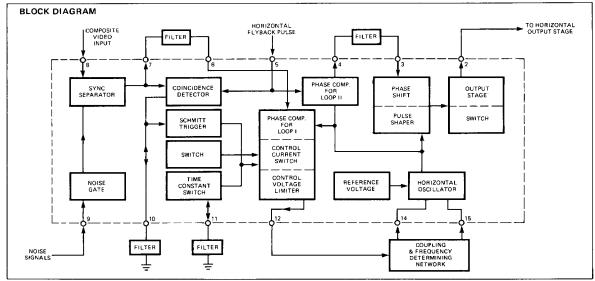

GENERAL DESCRIPTION - The TBA920s are monolithic integrated circuits designed for TV receiver applications. They are constructed on a single silicon chip using the Fairchild Planar\* process. They accept the composite video signal, separate sync pulses (with the added safeguard of noise gating) and provide a sync output for the vertical integrator. Also incorporated is the horizontal oscillator along with two phase comparators, one to compare flyback pulses to the oscillator and the other for sync phase comparison. The devices will interface with both SCR and transistor deflection systems.

- SYNC SEPARATOR

- NOISE GATE

- HORIZONTAL OSCILLATOR

- **DUAL PHASE COMPARATOR**

### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage 13.2 V 600 mW Total Power Dissipation (Note 1) Storage Temperature -55°C to +125°C -20°C ta +60°C Operating Temperature Pin Temperature (Soldering, 10 s) Voltages

$V_{1} - 16$  $V_{3} - 16$  $V_8 - 16$  $V_{10} - 16$

Currents I<sub>2</sub> (Average Value) 12 (Peak Value) I5 (Peak Value) 17 (Peak Value) Ig (Peak Value) Io (Peak Value)

260° C 13.2 V 0 to 13.2 V -12 V -0.5 to 5.0 V

-20 mA -200 mA 10 mA 10 mA 10 mA 10 mA

# FAIRCHILD • TBA920 • TBA920S

ELECTRICAL CHARACTERISTICS: T<sub>A</sub> = 25°C, V<sub>1 - 16</sub> = 12V, See Applications Circuit (CCIR Standard), unless otherwise specified. \* Note: TBA920S is identical to the TBA920 except as indicated, CHARACTERISTICS CONDITIONS MIN TYP MAX UNITS Current Consumption 12 = 0 11 36 mΑ Video Signal Input Voltage (Positive Going Sync) VIN (p-p) 1.0 3.0 7 N V Peak-to-Peak Value Input Current During Sync Pulse (Peak Value) lg 100 пΔ Noise Gating (Lead 9) Input Voltage (Peak Value) Vg -- 16 0.7 V Input Current (Peak Value) Ιg 0.03 10 mΔ Input Resistance R9 - 16 200 Ω Flyback Pulse (Lead 5) Input Voltage (Peak Value) V5 - 16 ± 1.0 V Input Current (Peak Value) 15 0.05 1.0 mΑ Input Resistance  $R_{5} - 16$ 400 Ω Pulse Duration f = 15625 Hz t5 10 μs Composite Sync Pulses (Positive, Lead 7) Output Voltage (Peak-to-Peak Value) V7 = 16 (p-p)10 V Output Resistance at Leading Edge of Pulse (Emitter Follower)  $R_7 - 16$ 50 O at Trailing Edge R7 - 16 2.2 kΩ Additional External Load Resistance  $R_7 = 16$  (ext.) 20  $k\Omega$ Driver Pulse (Lead 2) Output Voltage (Peak-to-Peak Value) V2 - 16 (p-p) 10 Average Output Current 12 (AVG) 20 mΑ Peak Output Current 200 mΑ Output Resistance (Low Ohmic)  $R_{2} - 16$ Note 2 2.5 or 15 Ω Output Pulse Duration Note 3 to 12 to 32 шs Permissible Delay Between Leading Edge <sup>t</sup>d (tot)  $t_5 = 12 \,\mu s$ 0 to 15 us of Output Pulse and Flyback Pulse Supply Voltage at Which Output  $V_{1} - 16$ 4.0 V Pulses are Obtained Oscillator Frequency, Free Running  $f_o$  $R_{15} = 16 = 3.3 \text{ k}\Omega \text{ (Note 4)}$ 15625 Ηz Spread of Frequency at Nominal Values  $\Delta f_{\underline{o}}$ ±5.0 % of Peripheral Components (TBA920) &  $f_{o}$ \*Spread of Frequency at Nominal Values  $\Delta f_0$ of Peripheral Components (TBA920S) ± 1.5  $f_{o}$ Frequency Change When Decreasing Δf<u>o</u> 10 the Supply Down to Minimum 4.0 V f<sub>o</sub> Δf<sub>o</sub> Frequency Control Sensitivity 16.5 Hz/μA  $\overline{\Delta I}_{15}$ Adjustment Range of Network in Circuit  $\Delta f_Q$ ±10 on Application Information (TBA920)  $f_{o}$  $\Delta f_{O}$ \*Adjustment Range of Network in ±5.0 Figure 1 (TBA920S) % fo Influence of Supply Voltage on Frequency δfo/δV  $V_1 = 12 V$ 5.0 % fo/Vnom Control Loop I (Between Sync Pulse and Oscillator) Control Voltage Range  $V_{12} - 16$ 0.8 to 5.5 v Control Current (Peak Values) 112  $V_{10} - 16 > 4.5 V$ ; ±2.0 mΑ  $V_{6-16} > 1.5 V$ 112  $V_{10-16} > 2.0 V;$ ±6.0 mΑ  $V_{6-16} > 1.5 V$ Loopgain of APC System a. Time Coincidence Between Sync Pulse 1.0 kHz/µs and Flyback Pulse or  $V_{10-16} > 4.5 \text{ V}$ Δt b. No Time Coincidence  $\Delta \mathsf{f}$ 3.0 kHz/μs or  $V_{10} - 16 \le 2.0 \text{ V}$  $\Delta t$ Capture and Holding Range Δf Note 6 ±1.0 kHz Pull In Time for  $\Delta f/f_0 = \pm 3\%$  $\Delta f = 470 \text{ Hz (Note 7)}$ 20 ms Switch Over From Large Control Sensitivity Note 7 20 ms to Small Control Sensitivity After Capture

# FAIRCHILD • TBA920 • TBA920S

| CHARACTERISTICS                                                                     |                                      | CONDITIONS                                                                       | MIN | TYP     | MAX | UNITS |

|-------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------|-----|---------|-----|-------|

| Control Loop II (Between Flyback Pulse and Oscillator)                              |                                      |                                                                                  |     |         |     |       |

| Permissible Delay Between Leading Edge of<br>Output Pulse (Lead 2) and Leading Edge | <sup>t</sup> d (tot)                 |                                                                                  |     | 0 to 15 |     | μs    |

| of Flyback Pulse<br>Static Control Error                                            | $\frac{\Delta t}{\Delta t_{cl}}$     | Note 8                                                                           |     |         | 0.5 | %     |

| Output Current During Flyback Pulse (Peak Value)                                    | 14                                   |                                                                                  |     | ±0.7    |     | mA    |

| Overall Phase Relation                                                              |                                      |                                                                                  |     |         |     |       |

| Phase Relation Between Leading Edge of<br>Sync Pulse and Middle of Flyback Pulse    | t                                    | Note 9                                                                           |     | 4.9     |     | μs    |

| Tolerance of Phase Relation (TBA920)                                                | Δt                                   | Note 10                                                                          |     |         | 1.0 | μς    |

| Tolerance of Phase Relation (TBA920S)                                               | lΔtl                                 |                                                                                  |     |         | 0.4 | μs    |

| Voltage for t <sub>2</sub> = 12 to 32 μs                                            | V3 – 16                              |                                                                                  |     | 6 to 8  |     | V.    |

| Adjustment Sensitivity                                                              | $\frac{\Delta t_2}{\Delta V_3 - 16}$ |                                                                                  |     | 10      |     | μs/V  |

| Input Current                                                                       | 13                                   |                                                                                  |     |         | 2.0 | μΑ    |

| External Switch Over of Parameters                                                  |                                      |                                                                                  |     |         |     |       |

| (Loop Filter and Loop Gain) of Control Loop I                                       |                                      |                                                                                  |     |         |     |       |

| (e.g. for Video Recorder Application) See Note                                      |                                      | 5 450.0                                                                          | 4.5 |         |     | V     |

| Required Switch Over Voltage                                                        | V10 – 16                             | $R_{11} - 16 = 150 \Omega$                                                       | 4.5 |         | 2.0 | V     |

|                                                                                     | V10 – 16                             | $R_{11} = 16 = 2.0 \text{ k}\Omega$<br>$R_{11} = 16 = 150 \Omega$                |     | 80      | 2.0 | μА    |

| Required Switch Over Current                                                        | 110                                  | V <sub>10</sub> - 16 = 4.5 V (Note 11)                                           |     | 00      | 1   | "     |

|                                                                                     | 110                                  | $R_{11} = 16 = 2.0 \text{ k}\Omega$ ,<br>$V_{10} = 16 = 2.0 \text{ V (Note 11)}$ |     | 120     |     | μΑ    |

#### NOTES:

- 1. 800 mW permissible while tubes are heating up.

- 2. Depends on switch position and polarity output current.  $R_2 = 16 = 2.5 \Omega$  is valid for  $V_2 = 16 = +10.5 \text{ V}$  and a load between leads 2 and 16 (e.g. an external resistor).

- 3. The output pulse duration is adjusted by shifting the leading edge (V<sub>3 16</sub> from 6.0 V to 8.0 V). The pulse duration is a result of delay in the line output device and the action of the second control loop in the TBA920.

For a line output stage with BU108 high voltage transistor the resulting duration is about 22  $\mu$ s, and in such a way that the line output transistor is switched on again about 8.0  $\mu$ s after the middle of the line flyback pulse. This pulse duration must be taken into account when designing the driver stage and driver transformer as this way of driving the line output device differs from the usual, i.e. a driver duty cycle of about 50%.

- 4. The oscillator frequency can be changed for other TV standards by an appropriate value of  $C_{14}=16$ .

- 5. Exclusive external components tolerances.

- 6. Adjustable with R<sub>12</sub> 15

- 7. See application information circuit.

- 8. The control error is the remaining error in reference to the nominal phase position between leading edge of the sync pulse and the middle of the flyback pulse caused by a variation in delay of the line output stage.

- This phase relation assumes a luminance delay line with a delay of 500 ns between the input of the sync separator and the drive to the

picture tube. If the sync separator is inserted after the luminance delay line or if there is no delay line at all (black and white sets), then

the phase relation is achieved at C<sub>5</sub> = 16 = 560 pF.

- 10. The adjustment of the overall phase relation and consequently the leading edge of the output pulse at lead 2 occurs automatically by the control loop II or by applying a dc voltage to lead 3.

- 11. With sync pulses at lead 7 and 8; without RC network at lead 10.

## TEST CIRCUITS

## TBA920S

(See application circuit for balance of circuitry)

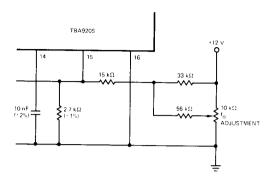

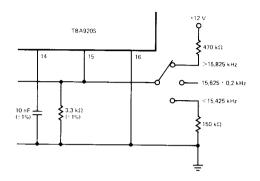

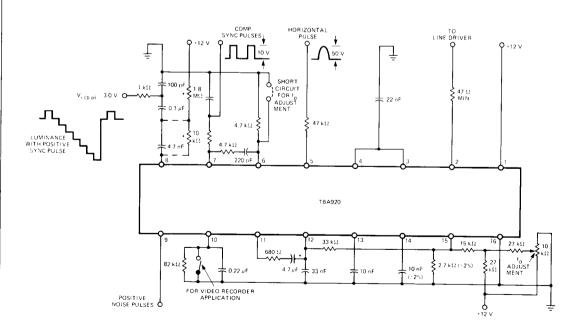

Frequency adjustment range. Test circuit for TBA 920S.

Other circuit possibilities for oscillator frequency adjustment,

Fig. 1

Fig. 2

## APPLICATION

(See Fig. 1 for TBA920S network)

\*To bias input direct to base.