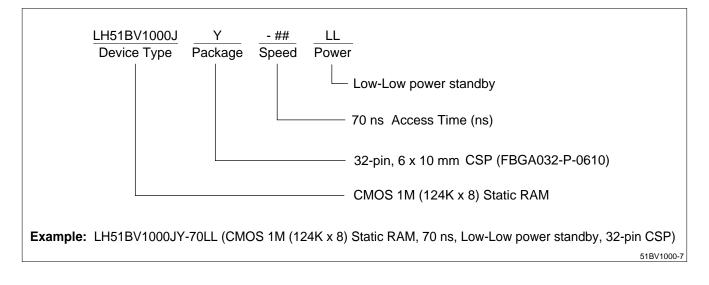

# LH51BV1000J

### FEATURES

- Access time: 70 ns (MAX.)

- Current consumption: Operating: 30 mA (MAX.)

5 mA (MAX.) (t<sub>RC</sub>, t<sub>WC</sub> = 1 μs) Standby: 60 μA (MAX.)

- Data Retention: 1.0  $\mu$ A (MAX.) (V<sub>CCDR</sub> = 3 V, T<sub>A</sub> = 25°C)

- Single power supply: 2.7 V to 3.6 V

- Operating temperature: -25°C to +85°C

- Fully-static operation

- Three-state output

- Not designed or rated as radiation hardened

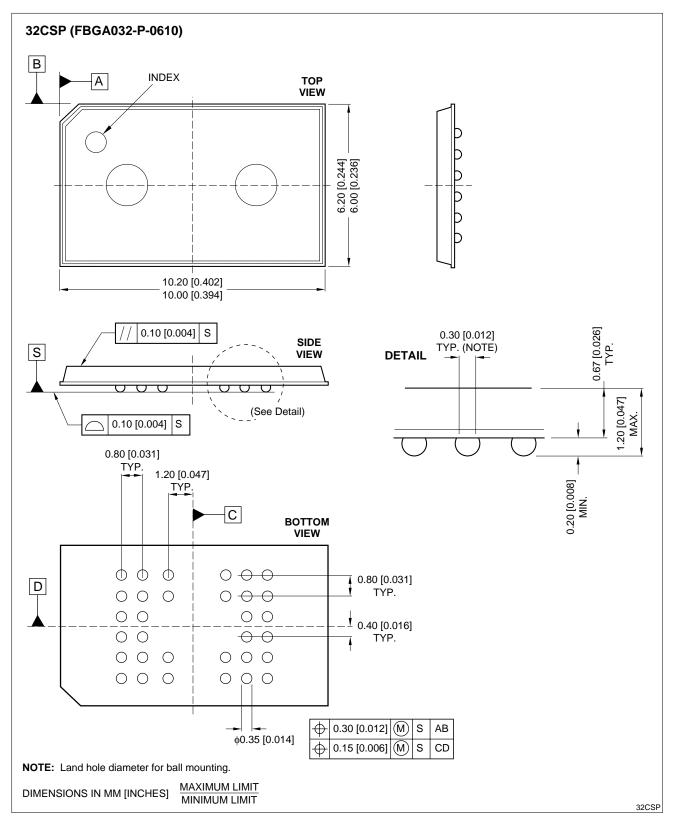

- Package: 32-pin 6 × 10 mm CSP

- N-type bulk silicon

#### DESCRIPTION

The LH51BV1000JY is a static RAM organized as 131,072  $\times$  8 bits which provides low power standby mode. It is fabricated using silicon-gate CMOS process technology.

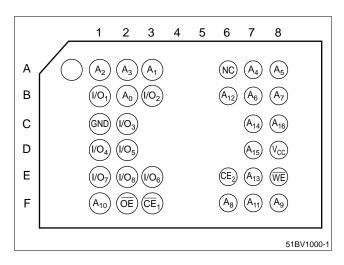

#### **PIN CONNECTIONS**

Figure 1. Pin Connections for CSP Package

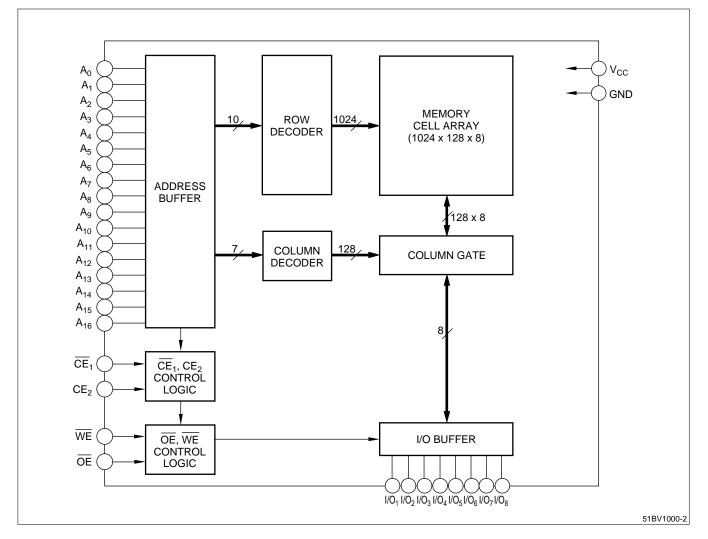

Figure 2. LH51BV1000JY Block Diagram

#### **PIN DESCRIPTION**

| SIGNAL          | PIN NAME       |

|-----------------|----------------|

| $A_0 - A_{16}$  | Address inputs |

| CE1             | Chip enable 1  |

| CE <sub>2</sub> | Chip enable 2  |

| WE              | Write enable   |

| OE              | Output enable  |

| SIGNAL                              | PIN NAME                |

|-------------------------------------|-------------------------|

| I/O <sub>1</sub> - I/O <sub>8</sub> | Data inputs and outputs |

| V <sub>CC</sub>                     | Power supply            |

| GND                                 | Ground                  |

| NC                                  | No connection           |

## **TRUTH TABLE**

| CE1 | CE2 | WE | OE | MODE           | I/O1 – I/O8    | SUPPLY CURRENT              |

|-----|-----|----|----|----------------|----------------|-----------------------------|

| Н   |     |    |    | Standby        | High impedance | Standby (I <sub>SB</sub> )  |

|     | L   |    |    | Standby        | High impedance | Standyby (I <sub>SB</sub> ) |

| L   | Н   | L  |    | Write          | Data input     | Active (Icc)                |

| L   | Н   | Н  | L  | Read           | Data output    | Active (I <sub>CC</sub> )   |

| L   | Н   | Н  | Н  | Output disable | High impedance | Active (I <sub>CC</sub> )   |

NOTE:

1. — = Don't care, L = Low, H = High

### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL           | SYMBOL RATING                 |    | NOTE |

|-----------------------|------------------|-------------------------------|----|------|

| Supply voltage        | Vcc              | -0.5 to +4.6                  | V  | 1    |

| Input voltage         | V <sub>IN</sub>  | -0.5 to V <sub>CC</sub> + 0.3 | V  | 1, 2 |

| Operating temperature | T <sub>OPR</sub> | -25 to +85                    | °C | _    |

| Storage temperature   | T <sub>STG</sub> | -65 to +150                   | °C | _    |

#### NOTE:

1. The maximum applicable voltage on any pin with respect to GND.

2. Undershoot of -3.0 V is allowed width of pulse below 50 ns.

## **RECOMMENDED OPERATING CONDITIONS (T<sub>A</sub> = -25^{\circ}C to +85^{\circ}C)**

| PARAMETER      | SYMBOL | MIN. | TYP. | MAX.                  | UNIT | NOTE |

|----------------|--------|------|------|-----------------------|------|------|

| Supply voltage | Vcc    | 2.7  | 3.0  | 3.6                   | V    |      |

| Input voltage  | VIH    | 2.2  |      | V <sub>CC</sub> + 0.3 | V    |      |

| input voitage  | VIL    | -0.3 |      | 0.4                   | V    | 1    |

#### NOTE:

1. Undershoot of -3.0 V is allowed width of pulse below 50 ns.

## DC ELECTRICALCHARACTERISTICS ( $T_A = -25^{\circ}C$ to $+85^{\circ}C$ , $V_{CC} = 2.7$ V to 3.6 V)

| PARAMETER                | SYMBOL           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                | MIN.                  | TYP. <sup>1</sup> | MAX. | UNIT |  |  |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|-------------------|------|------|--|--|

| Input leakage<br>current | ILI              | $V_{IN} = 0 V \text{ to } V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                | -1.0                  |                   | 1.0  | μΑ   |  |  |

| Output leakage current   | ILO              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -1.0                           |                       | 1.0               | μA   |      |  |  |

| Operating supply         |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | tcycle =<br>MIN.               |                       |                   | 30   | ~^^  |  |  |

| current                  | tandby current   | $\label{eq:cell} \begin{array}{l} \overline{CE}_1 = V_{IL},  V_{IN} = V_{IL} \text{ or } V_{IH} \\ CE_2 = V_{IH},  I_{I/O} = 0 \mbox{ mA} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>CYCLE</sub> =<br>1.0 μs |                       |                   | 5    | mA   |  |  |

| Standby current          | I <sub>SB</sub>  | $CE_1$ , $CE_2 \ge V_{CC} - 0.2$ V or $CE$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2≤0.2 V                        |                       | 0.6               | 60   | μA   |  |  |

| Standby current          | I <sub>SB1</sub> | $\begin{array}{c c} \hline CE_1 = V_{IH} \text{ or } CE_2 = V_{IL} \text{ or } \\ \hline CE_1 = V_{IH} \text{ or } WE = V_{IL} \\ V_{I/O} = 0 \text{ V to } V_{CC} \end{array}$ $\begin{array}{c c} \hline CE_1 = V_{IL}, V_{IN} = V_{IL} \text{ or } V_{IH} \\ \hline CE_2 = V_{IH}, I_{I/O} = 0 \text{ mA} \end{array} \qquad \begin{array}{c c} t_{CYCLE} = \\ MIN. \end{array}$ $\begin{array}{c c} \hline CE_1 = V_{IL}, V_{IN} = V_{IL} \text{ or } V_{IH} \\ CE_2 = V_{IH}, I_{I/O} = 0 \text{ mA} \end{array} \qquad \begin{array}{c c} t_{CYCLE} = \\ 1.0 \ \mu\text{s} \end{array}$ $\begin{array}{c c} \hline CE_1, CE_2 \ge V_{CC} - 0.2 \text{ V or } CE_2 \le 0.2 \text{ V} \end{array}$ $\begin{array}{c c} \hline CE_1 = V_{IH} \text{ or } CE_2 = V_{IL} \\ \hline I_{OL} = 2.0 \text{ mA}, V_{CC} \ge 3 \text{ V} \end{array}$ |                                |                       | 1.0               | mA   |      |  |  |

|                          | Vol              | $I_{OL}$ = 2.0 mA, $V_{CC} \ge 3 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |                       |                   | 0.4  |      |  |  |

| Output voltage           | VOL              | $I_{OL} = -0.1 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                |                       |                   | 0.2  | V    |  |  |

|                          | V <sub>OH</sub>  | $I_{OH} = -2.0 \text{ mA}, V_{CC} \ge 3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3 V                            | 2.4                   |                   |      |      |  |  |

|                          | VOH              | I <sub>OH</sub> = -0.1 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                | V <sub>CC</sub> – 0.2 |                   | _    |      |  |  |

#### NOTE:

1 Typical values at V\_{CC} = 5.0 V, T\_A = 25 ^{\circ}C

#### AC ELECTRICAL CHARACTERISTICS AC Test Conditions

| PARAMETER                          | MODE                | NOTE |

|------------------------------------|---------------------|------|

| Input pulse level                  | 0.4 V to 2.4 V      |      |

| Input rise and fall time           | 5 ns                | _    |

| Input and output timing ref. level | 1.5 V               | _    |

| Output load                        | 1 TTL + CL (100 pF) | 1    |

NOTE:

1. Including scope and jig capacitance.

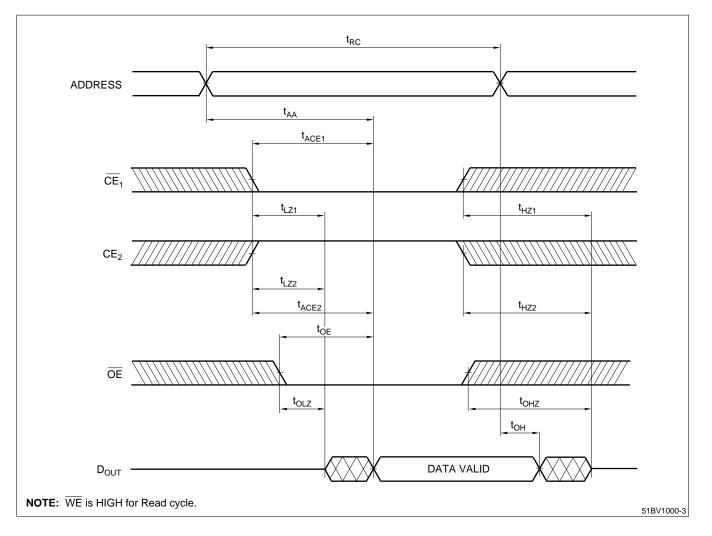

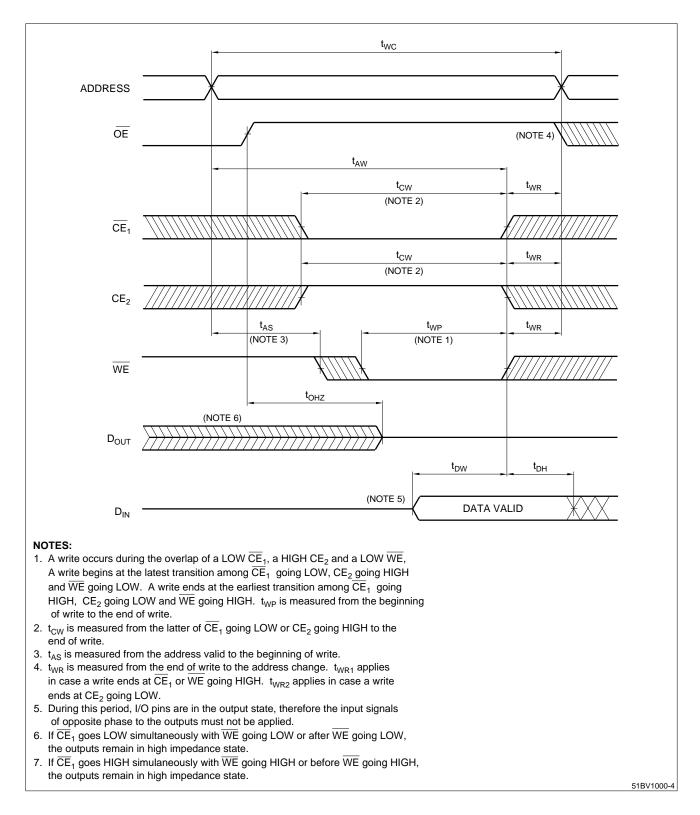

## READ CYCLE (T<sub>A</sub> = -25°C to +85°C, V<sub>CC</sub> = 2.7 V to 3.6 V)

| PARAMETER                                        | SYMBOL            | MIN. | MAX. | UNIT | NOTE |

|--------------------------------------------------|-------------------|------|------|------|------|

| Read cycle time                                  | t <sub>RC</sub>   | 70   |      | ns   |      |

| Address access time                              | t <sub>AA</sub>   |      | 70   | ns   |      |

| CE <sub>1</sub> access time                      | t <sub>ACE1</sub> |      | 70   | ns   |      |

| CE <sub>2</sub> access time                      | t <sub>ACE2</sub> |      | 70   | ns   |      |

| Output enable to output valid                    | t <sub>OE</sub>   |      | 40   | ns   |      |

| Output hold from address change                  | t <sub>OH</sub>   | 10   |      | ns   |      |

| CE <sub>1</sub> Low to output active             | t <sub>LZ1</sub>  | 5    |      | ns   | 1    |

| CE <sub>2</sub> High to output active            | t <sub>LZ2</sub>  | 5    | _    | ns   | 1    |

| OE Low to output active                          | toLZ              | 0    |      | ns   | 1    |

| CE <sub>1</sub> High to output in High impedance | t <sub>HZ1</sub>  |      | 30   | ns   | 1    |

| CE <sub>2</sub> Low to output in High impedance  | t <sub>HZ2</sub>  |      | 30   | ns   | 1    |

| OE High to output in High impedance              | t <sub>OHZ</sub>  |      | 30   | ns   | 1    |

#### NOTE:

1. Active output to High impedance to output active tests specified for a  $\pm 200 \text{ mV}$  transition from steady state levels into the test load.

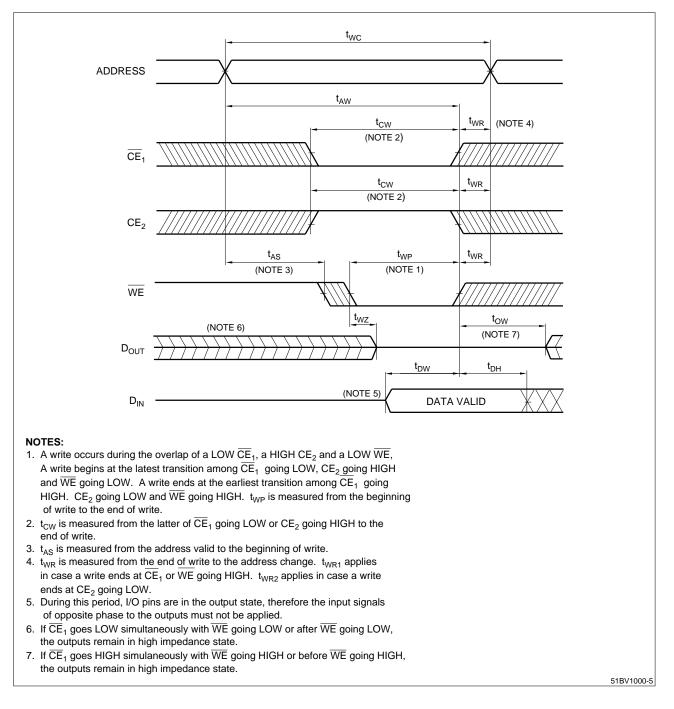

# WRITE CYCLE (T<sub>A</sub> = -25°C to +85°C, V<sub>CC</sub> = 2.7 V to 3.6 V)

| PARAMETER                           | SYMBOL          | MIN. | MAX. | UNIT | NOTE |

|-------------------------------------|-----------------|------|------|------|------|

| Write cycle time                    | t <sub>WC</sub> | 70   |      | ns   |      |

| Chip enable to end of write         | t <sub>CW</sub> | 60   | _    | ns   |      |

| Address valid to end of write       | t <sub>AW</sub> | 60   | _    | ns   |      |

| Address setup time                  | t <sub>AS</sub> | 0    | _    | ns   |      |

| Write pulse width                   | t <sub>WP</sub> | 55   | _    | ns   |      |

| Write recovery time                 | t <sub>WR</sub> | 0    | _    | ns   |      |

| Input data setup time               | t <sub>DW</sub> | 30   |      | ns   |      |

| Input data hold time                | t <sub>DH</sub> | 0    | _    | ns   |      |

| WE High to output active            | tow             | 5    | _    | ns   | 1    |

| WE Low to output in High impedance  | twz             |      | 30   | ns   | 1    |

| OE High to output in High impedance | tонz            |      | 30   | ns   | 1    |

#### NOTE:

1. Active output to High impedance to output active tests specified for a  $\pm 200 \text{ mV}$  transition from steady state levels into the test load.

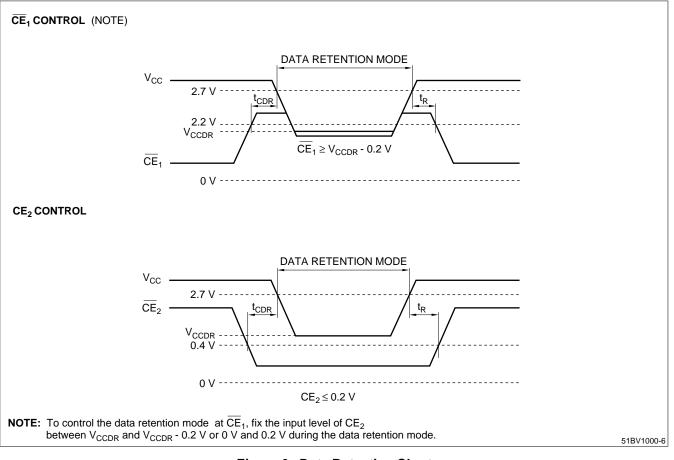

## DATA RETENTION CHARACTERISTICS (T<sub>A</sub> = -25°C to +850°C)

| PARAMETER                        | SYMBOL              | CONDITIONS                                                                                          |     | MIN.                | TYP. <sup>1</sup> | MAX. | UNIT | NOTES |  |

|----------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|-----|---------------------|-------------------|------|------|-------|--|

| Data retention supply voltage    | V <sub>CCDR</sub>   | $\begin{array}{c} CE_2 \leq 0.2 \ V \ or \\ \overline{CE}_1 \geq V_{CCDR} \  \ 0.2 \ V \end{array}$ |     | 2.0                 |                   | 3.6  | V    | 2     |  |

| V <sub>CCDR</sub> = 3 V          | $T_A = 25^{\circ}C$ | _                                                                                                   | 0.5 | 1.0                 | μΑ                |      |      |       |  |

| Data retention<br>supply current | ICCDR               | $CE_2 \le 0.2 \text{ V or}$ $CE_1 \ge V_{CCDR} - 0.2 \text{ V}$                                     |     | $T_A = 40^{\circ}C$ |                   |      | 3.0  |       |  |

|                                  |                     |                                                                                                     |     |                     |                   | 50   | μΑ   | 2     |  |

| Chip enable<br>setup time        | tCDR                | _                                                                                                   |     | 0                   |                   |      | ms   |       |  |

| Chip enable<br>hold time         | t <sub>R</sub>      | _                                                                                                   |     | 5                   |                   |      | ms   |       |  |

#### NOTES:

1. Typical value at  $T_A = 25^{\circ}C$

2.  $CE_2 \geq V_{CCDR}$  - 0.2 V or  $CE_2 \leq 0.2$  V

## PIN CAPACITANCE ( $T_A = 25^{\circ}C$ , f = 1 MHz)

| PARAMETER         | SYMBOL           | CONDITIONS            | MIN. | TYP. | MAX. | UNIT | NOTE |

|-------------------|------------------|-----------------------|------|------|------|------|------|

| Input capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0 V |      |      | 8    | pF   | 1    |

| I/O capacitance   | C <sub>I/O</sub> | $V_{I/O} = 0 V$       |      |      | 10   | pF   | 1    |

NOTE:

1. This parameter is sampled and not production tested.

Figure 3. Read Cycle

Figure 4. Write Cycle (OE Controlled)

Figure 5. Write Cycle (OE Low Fixed)

Figure 6. Data Retention Chart (CE<sub>1</sub> Controlled)

### PACKAGE DIAGRAM

#### **ORDERING INFORMATION**