# LC78684E

# **MP3 Decoder for Compact Disc Players**

### Overview

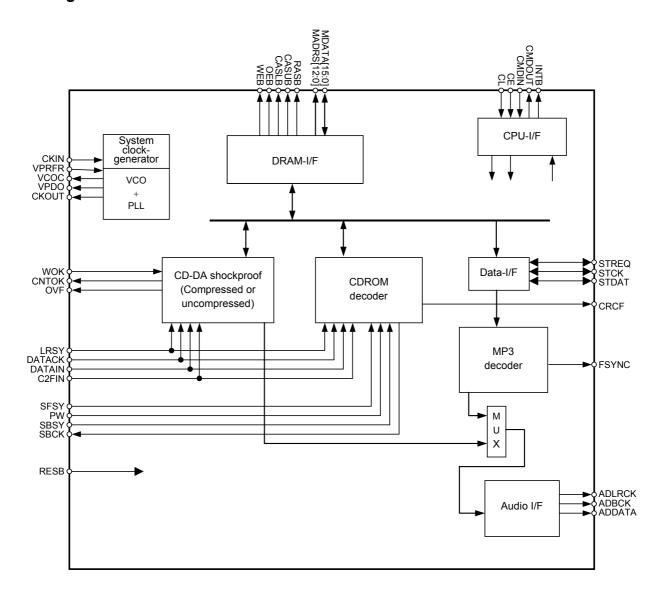

The LC78684E integrates, on a single chip, CD-ROM signal-processing functions, MP3 signal-processing functions, and CD-DA shockproof signal-processing functions. The LC78684E achieves significant power savings by implementing signal-processing functions using hard-wired structures.

A CD player that supports playback of MPEG audio (MP3) recorded on CD media as well as CD-DA shockproof playback can be implemented by combining this IC with a CD DSP, DRAM, and audio D/A converter, and other circuits.

### **Features**

- MP3 Decoding Functions (MPEG audio standard [ISO/IEC 11172-3] layer 3)

- Decodes to a digital audio signal MP3 data decoded by the CD-ROM decoder and outputs that audio signal.

- Supports all bit rates, including variable bit rate operation.

- Supports the following sampling rates.

MPEG1 (Fs = 32 K, 44.1 K, 48 K) MPEG2 (Fs = 16 K, 22.05 K, 24 K) MPEG2.5 (Fs = 8 K, 11.025 K, 12 K)

- Can read out the MPEG header and ancillary data.

- Automatically mutes the signal on CRC errors using an MP3 CRC check function.

- External MPEG serial data input function supports memory card playback.

- CD-ROM Decoding Functions

- Supports CD-ROM modes 1 and 2 (forms 1 and 2)

- Faithfully reproduces data stored on CD-ROM discs using CD-ROM error correction functions.

- Header and sector management

- Supports playback speeds up to 4×.

- In addition to data buffering also supports C2 error flag buffering.

- Provides external serial output of decoded CD-ROM data

- CD-DA Playback Functions (Shockproof support)

- Shockproof operation for about 180 seconds (compressed mode) when 64M DRAM is used.

- Shockproof function supports compressed, uncompressed, and data through modes.

- VCEC (variable speed) supports up to 4×-speed playback.

- Audio Signal Processing

- Serial audio signal output using LRCK, BCK, and DATA signals.

- (I<sup>2</sup>S format, either 16-bit or 20-bit precision PCM output, data-slot supports 16-bit, 24-bit, and 32-bit modes)

- Digital bass boost function (4 modes), attenuator function, and muting ( $-\infty$ , -12 dB)

- Provides a base clock (384 fs) output pin for use with external digital filters and D/A converters.

- DRAM Interface

- Supports the use of from 1M to 64M of external DRAM (EDO, 2CAS, 16-bit data bus memory)

- Supports allocation of a user area in DRAM during CD-ROM (MP3) playback.

Continued on next page.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein

Continued from preceding page.

- Package and Power Supply Voltage Specifications

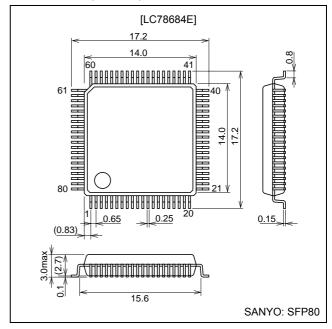

- Package: Sanyo QFP80 (14 × 14) (unit: mm)

- Supply voltage

Internal power supply: 1.8 V (typical) I/O power supply: 3.3 V (typical)

Analog system power supply: 3.3 V (typical)

## MPEG Layer3 audio coding technology licensed from Fraunhofer IIS and THOMSON multimedia

## **Package Dimensions**

Unit: mm

3255-QFP80 (14 × 14)

# **Block Diagram**

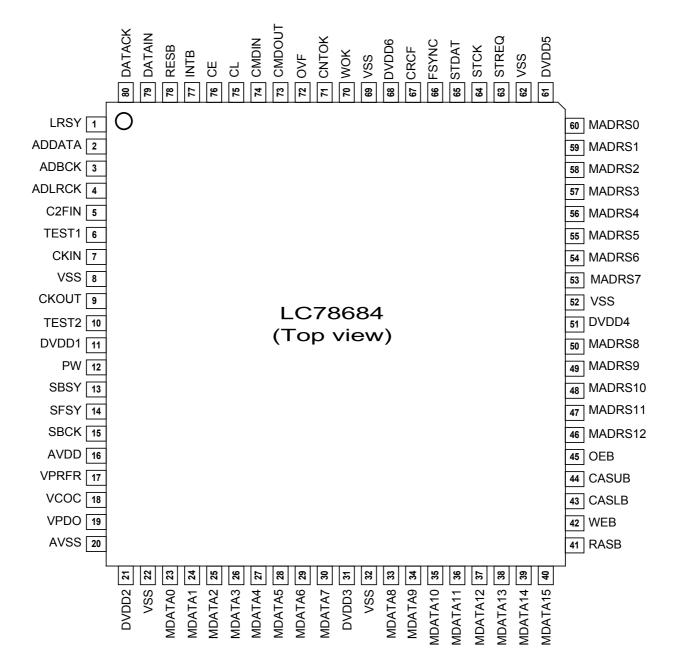

### **Pin Assignment**

# **Pin Functions**

# Absolute Maximum Ratings at $V_{SS}$ = 0 V, $AV_{SS}$ = 0 V

| Parameter                   | Symbol              | Conditions | Ratings                   | Unit |

|-----------------------------|---------------------|------------|---------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |            | $-0.3$ to $V_{SS} + 4.0$  | V    |

| Input voltage               | $V_{IN}$            |            | $-0.3$ to $V_{DD}1 + 0.3$ | V    |

| Output voltage              | V <sub>out</sub>    |            | $-0.3$ to $V_{DD}1 + 0.3$ | V    |

| Allowable power dissipation | Pdmax               |            | 400                       | mW   |

| Operating temperature       | Topr                |            | −30 to +75                | °C   |

| Storage temperature         | Tstg                |            | -40 to +125               | °C   |

# Allowable Operating Ranges at $Ta=-30\ to\ +75^{\circ}C,\ V_{SS}=0\ V,\ AV_{SS}=0V$

| Parameter                 | Symbol            | Pin name                                                                                                                                            | Conditions |                       | Ratings |                       | Unit  |

|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------|---------|-----------------------|-------|

| Farameter                 | Syllibol          | Finname                                                                                                                                             | Conditions | min                   | typ     | max                   | Offic |

| Supply voltage            | V <sub>DD</sub> 1 | DV <sub>DD</sub> 1, DV <sub>DD</sub> 3,<br>DV <sub>DD</sub> 4, DV <sub>DD</sub> 6, AV <sub>DD</sub>                                                 |            | 3.0                   | 3.3     | 3.6                   | V     |

|                           | $V_{DD}2$         | DV <sub>DD</sub> 2, DV <sub>DD</sub> 5                                                                                                              |            | 1.62                  | 1.8     | 1.98                  | V     |

| High-level input voltage  | V <sub>IH</sub>   | MDATA0 to 15,<br>LRSY, DATAIN,<br>DATACK, C2FIN,<br>PW, SBSY, SFSY,<br>STREQ, STCK,<br>STDAT, WOK,<br>CKIN, CE, CL,<br>CMDIN, RESB                  |            | 0.8 V <sub>DD</sub> 1 |         | V <sub>DD</sub> 1     | V     |

| Low-level input voltage   | V <sub>IL</sub>   | MDATA0 to 15,<br>LRSY, DATAIN,<br>DATACK, C2FIN,<br>PW, SBSY, SFSY,<br>STREQ, STCK,<br>STDAT, WOK,<br>CKIN, CE, CL,<br>CMDIN, RESB,<br>TEST1, TEST2 |            | 0                     |         | 0.2 V <sub>DD</sub> 1 | V     |

| Operating frequency range | Fop               | CKIN                                                                                                                                                |            |                       | 16.9344 |                       | MHz   |

# LC78684E

# Electrical Characteristics at Ta = -30 to + 75 °C, $V_{DD}1$ = 3.0V to 3.6 V, $V_{DD}2$ = 1.62 V to 1.98 V, $V_{SS}$ = 0 V, $AV_{SS}$ = 0 V

| Parameter                  | Symbol               | Pin name                                                                                                                                                           | Conditions                               |                        | Ratings |      | Unit  |

|----------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------|---------|------|-------|

| Faranietei                 | Symbol               |                                                                                                                                                                    |                                          | min                    | typ     | max  | Offic |

|                            | I <sub>DD</sub> (1)  | $DV_{DD}1$ , $DV_{DD}3$ , $DV_{DD}4$ , $DV_{DD}6$ , $AV_{DD}$                                                                                                      | V <sub>DD</sub> 1 = 3.0 to 3.6 V         |                        | 10.0    | 20.0 | mA    |

| Current drain              | I <sub>DD</sub> (2)  | DV <sub>DD</sub> 2, DV <sub>DD</sub> 5                                                                                                                             | V <sub>DD</sub> 2 =<br>1.62 to<br>1.98 V |                        | 4.5     | 10.0 | mA    |

| High-level input current   | I <sub>IH</sub>      | MDATA0 to 15,<br>LRSY, DATAIN,<br>DATACK, C2FIN,<br>PW, SBSY, SFSY,<br>STREQ, STCK,<br>STDAT, WOK,<br>CKIN, CE, CL,<br>CMDIN, RESB                                 | $V_{\text{IN}} = V_{\text{DD}} 1$        |                        |         | 10   | μΑ    |

| Low-level input current    | I <sub>IL</sub>      | MDATA0 to 15,<br>LRSY, DATAIN,<br>DATACK, C2FIN,<br>PW, SBSY, SFSY,<br>STREQ, STCK,<br>STDAT, WOK,<br>CKIN, CE, CL,<br>CMDIN, RESB,<br>TEST1, TES2                 | $V_{IN} = 0 V$                           | -10                    |         |      | μА    |

| High-level output voltage  | V <sub>он</sub> (1)  | MDATA0 to 15,<br>STREQ, STCK,<br>STDAT, MADRS0 to<br>12, RASB, CASUB,<br>CASLB, OEB, WEB<br>SBCK, ADDATA,<br>ADLRCK, ADBCK,<br>INTB, FSYNC,<br>CRCF, CNTOK,<br>OVF | I <sub>OH</sub> = -2 mA                  | V <sub>DD</sub> 1 -0.6 |         |      | V     |

|                            | V <sub>OH</sub> (2)  | CKOUT                                                                                                                                                              | $I_{OH} = -4 \text{ mA}$                 | V <sub>DD</sub> 1-0.6  |         |      | V     |

|                            | V <sub>OH</sub> (3)  | VPDO                                                                                                                                                               | I <sub>OH</sub> =<br>-0.2 mA             | V <sub>DD</sub> 1–0.6  |         |      | •     |

| Low-level output voltage   | V <sub>OL</sub> (1)  | MDATA0 to 15 STREQ, STCK, STDAT, MADRS0 to 12, RASB, CASUB, CASLB, OEB, WEB SBCK, ADDATA, ADLRCK, ADBCK, INTB, FSYNC, CRCF, CNTOK, OVF, CMDOUT                     | I <sub>OL</sub> = 2 mA                   |                        |         | 0.4  | V     |

|                            | V <sub>OL</sub> (2)  | CKOUT                                                                                                                                                              | $I_{OL} = 4 \text{ mA}$                  |                        |         | 0.4  | V     |

|                            | V <sub>OL</sub> (3)  | VPDO                                                                                                                                                               | I <sub>OL</sub> = 0.2 mA                 |                        |         | 0.4  | •     |

| Output off leakage current | I <sub>OFF</sub> (1) | MDATA0 to 15,<br>STREQ,<br>STCK, STDAT,<br>CMDOUT                                                                                                                  | $V_{OUT} = V_{DD}1$                      |                        |         | 10   | μА    |

|                            | I <sub>OFF</sub> (2) | MDATA0 to 15,<br>STREQ, STCK,<br>STDAT, CMDOUT                                                                                                                     | V <sub>OUT</sub> = 0 V                   | -10                    |         |      | μА    |

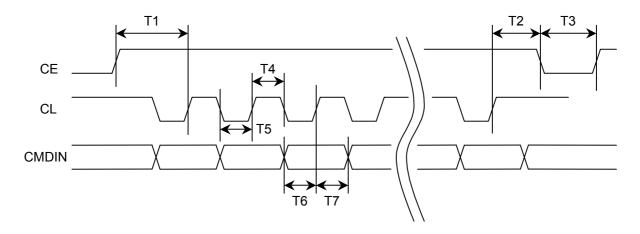

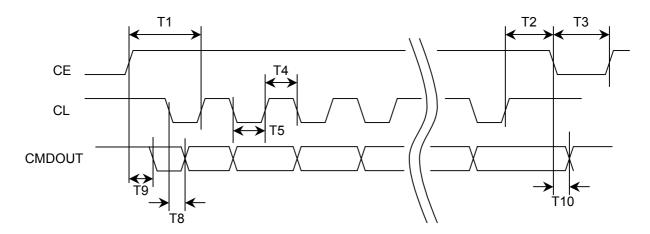

# Microcontroller Interface Microcontroller Interface Timing

# Write Cycle

# **Read Cycle**

| Deventer                  | Comple el |      | Ratings |     |      |

|---------------------------|-----------|------|---------|-----|------|

| Parameter                 | Symbol    | min  | typ     | max | Unit |

| CE/CL setup time          | T1        | 500  |         |     | ns   |

| CE/CL hold time           | T2        | 250  |         |     | ns   |

| Command wait time         | T3        | 1000 |         |     | ns   |

| CL H-level pulse width    | T4        | 250  |         |     | ns   |

| CL L-level pulse width    | T5        | 250  |         |     | ns   |

| Data/CL setup time        | T6        | 150  |         |     | ns   |

| Data/CL hold time         | T7        | 150  |         |     | ns   |

| Data-read access time *   | Т8        | 0    |         | 240 | ns   |

| Data-read turn-on time *  | T9        | 0    |         | 150 | ns   |

| Data-read turn-off time * | T10       | 0    |         | 240 | ns   |

<sup>\*:</sup> Pull-up resistor = 1 K $\Omega$ , Output load = 30 pF

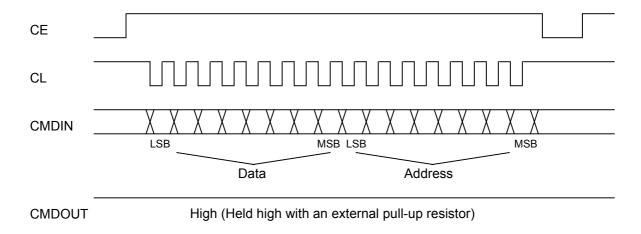

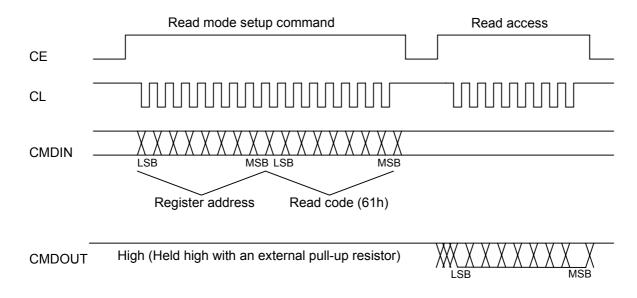

### **Command Input/Data Output Interface**

Input commands (i.e. write data to the LC78684E) in the order data first and then address. The data and address are LSB first. Output data is output (i.e. read data from the LC78684E) by first issuing a read mode setup command and then performing read access operations.

#### **Data write**

#### Data read

Data is read by first writing the register address to be read to location \$61h and then setting up read mode by setting CE low temporarily. When CE is set high again, and the CL signal is issued, the contents of the specified register are output from CMDOUT, LSB first.

The microcontroller must perform a read access if it sets up read mode.

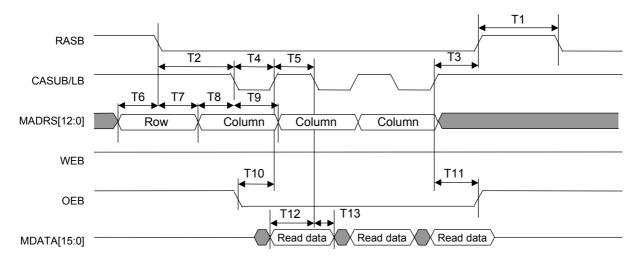

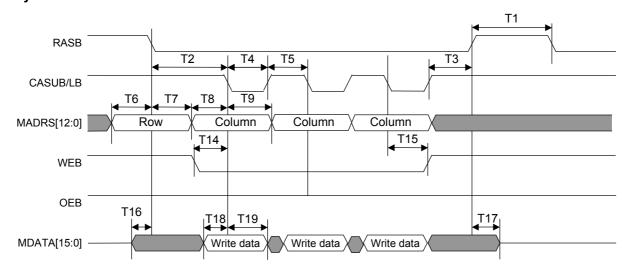

# **Memory Interface Memory Interface Timing**

## **Read Cycle**

## **Write Cycle**

# Refresh Cycle (CAS before RAS)

| December                  | Complete al |     | Ratings |     | Unit |

|---------------------------|-------------|-----|---------|-----|------|

| Parameter                 | Symbol      | min | typ     | max | Unit |

| RASB width high           | T1          | 100 |         |     | ns   |

| RASB CASB delay           | T2          | 80  |         |     | ns   |

| CASB RASB delay           | T3          | 40  |         |     | ns   |

| CASB width low            | T4          | 40  |         |     | ns   |

| CASB width high           | T5          | 40  |         |     | ns   |

| Row address setup time    | T6          | 15  |         |     | ns   |

| Row address hold time     | T7          | 40  |         |     | ns   |

| Column address setup time | T8          | 15  |         |     | ns   |

| Column address hold time  | T9          | 40  |         |     | ns   |

| OEB ready time            | T10         | 30  |         |     | ns   |

| OEB hold time             | T11         | 10  |         |     | ns   |

| Read data setup time      | T12         | 30  |         |     | ns   |

| Read data hold time       | T13         | 0   |         |     | ns   |

| WEB ready time            | T14         | 30  |         |     | ns   |

| WEB hold time             | T15         | 40  |         |     | ns   |

| Write data turn on time   | T16         |     |         | 60  | ns   |

| Write data turn off time  | T17         |     |         | 80  | ns   |

| Write data setup time     | T18         | 15  |         |     | ns   |

| Write data hold time      | T19         | 40  |         |     | ns   |

| Refresh cycle             | T20         | 300 |         |     | ns   |

| RASB low width (refresh)  | T21         | 200 |         |     | ns   |

| RASB CASB delay (refresh) | T22         | 50  | _       |     | ns   |

| CASB setup time (refresh) | T23         | 40  | _       |     | ns   |

| CASB hold time (refresh)  | T24         | 100 |         |     | ns   |

<sup>\*</sup>: These values apply when the frequency of the clock input to the CKIN pin is 16.9344 MHz.

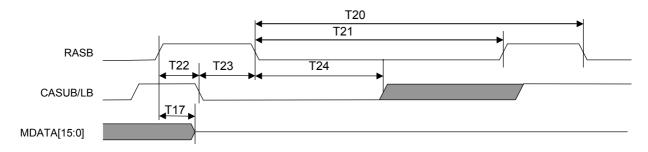

# CD DSP Interface CD DSP Interface Timing

| Parameter                  | Symbol |     | Unit |      |       |

|----------------------------|--------|-----|------|------|-------|

|                            | Symbol | min | typ  | max  | Offic |

| DATACK frequency           | Fbck   |     |      | 14.5 | MHz   |

| DATACK H-level pulse width | T1h    | 30  |      |      | ns    |

| DATACK L-level pulse width | T1I    | 30  |      |      | ns    |

| LRSY setup time            | T2     | 30  |      |      | ns    |

| LRSY hold time             | Т3     | 30  |      |      | ns    |

| DATA, C2FIN setup time     | T4     | 30  |      |      | ns    |

| DATA, C2FIN hold time      | T5     | 25  |      |      | ns    |

<sup>\*:</sup> The figure above shows the timings when DATACK rising edge latch is used.

If DATACLK falling edge latch is used, the timings are the same as those for the corresponding setup and hold signal.

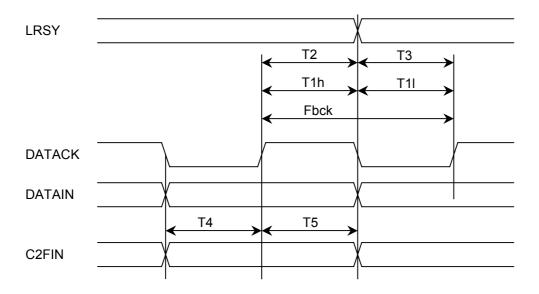

## **Subcode Interface Timing**

| Parameter                | Cymhal |     | Unit   |      |       |

|--------------------------|--------|-----|--------|------|-------|

| Parameter                | Symbol | min | typ    | max  | Offic |

| SFSY – SBCK delay time   | Tssd   | 235 |        | 7150 | ns    |

| SBCK frequency           | Fsbck  |     | 1.0584 |      | MHz   |

| SBCK H-level pulse width | T1h    | 450 |        |      | ns    |

| SBCK L-level pulse width | T1I    | 450 |        |      | ns    |

| PW setup time            | T2     | 50  |        |      | ns    |

| PW hold time             | Т3     | 0   |        |      | ns    |

<sup>\*:</sup> These values apply when the frequency of the clock input to the CKIN pin is 16.9344 MHz.

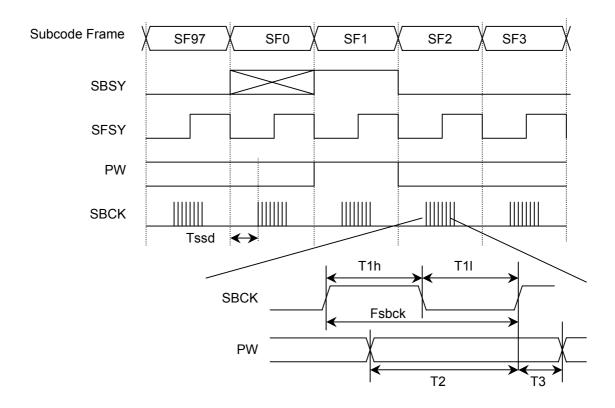

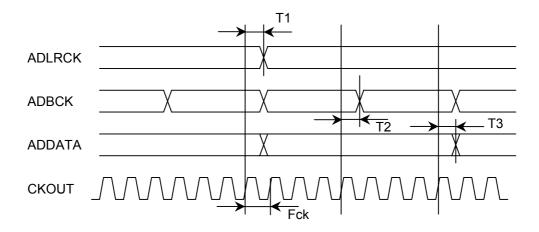

# Audio Output Interface Audio Output Interface Timing

The figure above applies when the 48-bit slot is used for the audio data output slot.

| Parameter                 | Symbol |     | Unit    |     |     |  |

|---------------------------|--------|-----|---------|-----|-----|--|

| Falanietei                | Symbol | min | typ     | max | L   |  |

| CKOUT → ADLRCK delay time | T1     | 0   |         | 35  | ns  |  |

| CKOUT → ADBCK delay time  | T2     | 0   |         | 35  | ns  |  |

| CKOUT → ADDATA delay time | T3     | 0   |         | 35  | ns  |  |

| CKOUT frequency *         | Fck    |     | 16.9344 |     | MHz |  |

<sup>\*:</sup> These values apply during MPEG1 data playback (fs = 44.1 kHz) when the PLL circuit is locked normally. These values depend on the playback sampling frequency (fs). (CKOUT frequency = fs × 384)

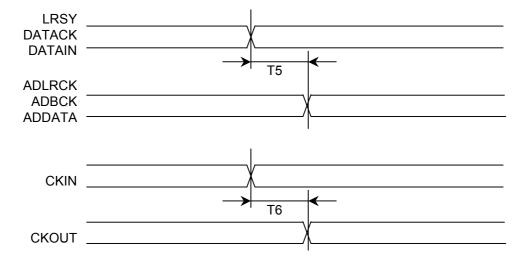

### **Supplement: Output Timing for Full Through Mode Playback**

\*: Full through mode is the state where the THROUGH bit (60h: bit 6) is set to 1.

| Parameter                     | Symbol |     | Unit |     |      |

|-------------------------------|--------|-----|------|-----|------|

| Falanietei                    |        | min | typ  | max | Unit |

| INPUT → OUTPUT delay time     | T5     | 0   |      | 35  | ns   |

| $CKIN \to CKOUT$ delay time * | T6     | 0   |      | 35  | ns   |

<sup>\*:</sup> These values apply when the signal input to the CKIN pin is directly output from the CKOUT pin.

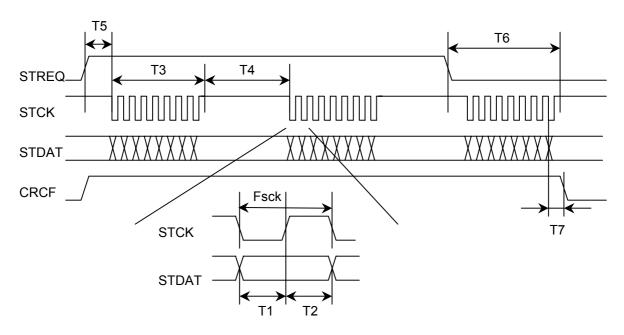

# Serial Data I/O Interface DRAM Serial Data Output Timing

\*: Performing a serial data output operation requires that a command to transfer data from DRAM be issued.

If this command has not been issued, the STCK and STDAT pins will not output the clock and data signals, even if the STREQ goes high.

| Parameter                  | Cumbal |      | Unit   |      |      |

|----------------------------|--------|------|--------|------|------|

|                            | Symbol | min  | typ    | max  | Unit |

| Transfer clock frequency   | Fsck   |      | 4.2336 |      | MHz  |

| STDAT/STCK setup time      | T1     | 30   |        |      | ns   |

| STDAT/STCK hold time       | T2     | 30   |        |      | ns   |

| Data (1byte) transfer time | Т3     |      | 1.89   |      | μs   |

| Data transfer wait time    | T4     |      | 1.89   |      | μS   |

| Data transfer start time   | T5     | 1.89 |        | 15.2 | μS   |

| Data transfer stop time    | T6     | 0    |        | 15.2 | μS   |

| Enable flag turn off time  | T7     | 210  | 236.2  | 270  | ns   |

Notes: The typical values shown apply when the frequency of the clock input to the CKIN pin is 16.9344 MHz.

- The fsck clock frequency can also be set to 2.1168 or 1.0584 MHz (typical). The values of T3 to T7 will be, in that case, 2 or 4 times the values shown.

- When the STREQ pin is in input mode, the WOK, OVF, and CNTOK pins can be used instead of the STREQ, STCK, and SDAT pins. The timing specifications in this case are the same as those shown above.

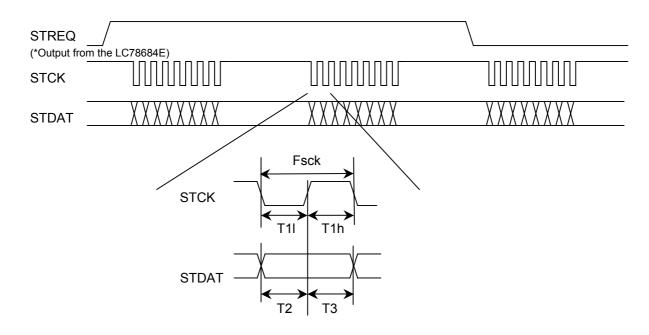

### **MP3 Serial Data Input Timing**

Performing a serial data input operation requires that a serial input command be issued.

If this command has not been issued, the MP3 decoder will not operate, even if clock and data signals are applied to the STCK and STDAT pins.

| Parameter                  | Cymbal |     | Linit |       |      |

|----------------------------|--------|-----|-------|-------|------|

|                            | Symbol | min | typ   | max   | Unit |

| Transfer clock frequency * | Fsck   |     |       | 9.216 | MHz  |

| STCK H-level pulse width   | T1h    | 45  |       |       | ns   |

| STCK L-level pulse width   | T1I    | 45  |       |       | ns   |

| STDAT/STCK setup time      | T2     | 30  |       |       | ns   |

| STDAT/STCK hold time       | Т3     | 30  |       |       | ns   |

\*: The table below lists the maximum frequencies for the transfer clock during serial input operations.

| MODE      | Fs (KHz)       | Maximum serial transfer clock frequency (MHz) * |

|-----------|----------------|-------------------------------------------------|

| MPEG1     | 48             | 9.216                                           |

|           | 44.1           | 8.4672                                          |

|           | 32             | 6.144                                           |

| MPEG2     | 24 (12)        | 4.608                                           |

| (MPEG2.5) | 22.05 (11.025) | 4.2336                                          |

|           | 16 (8)         | 3.072                                           |

The transfer clock rate must be set to a speed less than or equal to the speed shown in the table so that the MP3 decoding processing will complete in time.

Note that the table above applies when MP3DSET (register 41h, bit 0) is set to 1 (high-speed transfer mode). The timings shown below apply when MP3DSET is set to 0 (low-speed transfer mode).

| Parameter                | Cumbal |     | Ratings | Linit |      |

|--------------------------|--------|-----|---------|-------|------|

| Parameter                | Symbol | min | typ     | max   | Unit |

| Transfer clock frequency | Fsck   |     |         | 3.072 | MHz  |

| STCK H-level pulse width | T1h    | 150 |         |       | ns   |

| STCK L-level pulse width | T1I    | 150 |         |       | ns   |

| STDAT / STCK setup time  | T2     | 125 |         |       | ns   |

| STDAT / STCK hold time   | T3     | 125 |         |       | ns   |

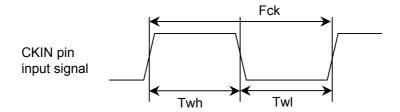

## **System Clock Input**

| Decemeter                | Cymphol |     | Ratings |      |      |  |

|--------------------------|---------|-----|---------|------|------|--|

| Parameter                | Symbol  | min | typ     | max  | Unit |  |

| CKIN Input frequency     | Fck     |     | 16.9344 | 18.0 | MHz  |  |

| CKIN H-Level pulse width | Twh     | 20  |         |      | ns   |  |

| CKIN L-Level pulse width | Twl     | 20  |         |      | ns   |  |

## **System Reset Input**

| Dorometer                | Cumbal | Ratings |     |     | Linit |

|--------------------------|--------|---------|-----|-----|-------|

| Parameter                | Symbol | min     | typ | max | Unit  |

| System reset pulse width | Trst   | 1       |     |     | μS    |

<sup>\*:</sup> A system reset must be performed immediately after power is first applied. Design the system so that no noise appears on the reset line.

# **Pin Functions**

| Pin No.                                          | Pin Name           | I/O        | Block             | Function                                                                     |

|--------------------------------------------------|--------------------|------------|-------------------|------------------------------------------------------------------------------|

| 1                                                | LRSY               | ı          | CD IF             | CD left/right clock input                                                    |

| 2                                                | ADDATA             | 0          | -                 | Audio data output                                                            |

| 3                                                | ADBCK              | 0          | Audio interface   | Audio bit clock output                                                       |

| 4                                                | ADLRCK             | 0          |                   | Audio left/right clock output                                                |

| 5                                                | C2FIN              | ī          | CD IF             | CD C2 error flag input                                                       |

| 6                                                | TEST1              | l ı        | Test              | Test input 1 (This pin must be connected to ground during normal operation.) |

| 7                                                | CKIN               | li         | CLOCK             | System clock input (16.9344 MHz)                                             |

| 8                                                | VSS                | _          | Power supply      | Ground                                                                       |

| 9                                                | CKOUT              | 0          | CLOCK             | External digital filter and D/A converter clock (384 fs) output              |

| 10                                               | TEST2              | i          | Test              | Test input 2 (This pin must be connected to ground during normal operation.) |

| 11                                               | DV <sub>DD</sub> 1 |            | Power supply      | Digital I/O system power supply                                              |

| 12                                               | PW                 | ı          | . one. supp.y     | CD subcode data serial input                                                 |

| 13                                               | SBSY               | i          |                   | CD subcode block sync signal input                                           |

| 14                                               | SFSY               | i          | Subcode interface | CD subcode frame sync signal input                                           |

| 15                                               | SBCK               | 0          |                   | CD subcode transfer serial clock output                                      |

| 16                                               | AV <sub>DD</sub>   | _          | Power supply      | Analog system (PLL) power supply                                             |

| 17                                               | VPRFR              | _          | 1 ower cuppiy     | VCO oscillator range setting                                                 |

| 18                                               | VCOC               | 1          | PLL               | VCO control voltage input                                                    |

| 19                                               | VPDO               | 0          |                   | VCO charge pump output                                                       |

| 20                                               | AVSS               | _          |                   | Analog system ground                                                         |

| 21                                               | DV <sub>DD</sub> 2 | _          | Power supply      | Internal logic system power supply                                           |

| 22                                               | VSS                | _          | T Ower Supply     | GND                                                                          |

| 23                                               | MDATA0             | I/O        |                   | DRAM data bus 0                                                              |

| 24                                               | MDATA0             | 1/0        |                   | DRAM data bus 1                                                              |

| 25                                               | MDATA1             | 1/0        |                   | DRAM data bus 1                                                              |

| 26                                               | MDATA2<br>MDATA3   | 1/0        |                   | DRAM data bus 3                                                              |

| 27                                               | MDATA4             | 1/0        | Memory interface  | DRAM data bus 3  DRAM data bus 4                                             |

| 28                                               | MDATA4<br>MDATA5   | 1/0        |                   | DRAM data bus 5                                                              |

| 29                                               | MDATA6             | 1/0        |                   | DRAM data bus 6                                                              |

| 30                                               | MDATA6             | 1/0        |                   |                                                                              |

| 31                                               | DV <sub>DD</sub> 3 |            |                   | DRAM data bus 7                                                              |

| 32                                               | VSS                | _          | Power supply      | Digital I/O system power supply GND                                          |

| 33                                               | MDATA8             | I/O        |                   | DRAM data bus 8                                                              |

|                                                  |                    |            |                   |                                                                              |

| 34                                               | MDATA10            | 1/0        |                   | DRAM data bus 9                                                              |

| 35<br>36                                         | MDATA10            | 1/0        |                   | DRAM data bus 10                                                             |

| <del>                                     </del> | MDATA11            | 1/0        |                   | DRAM data bus 11                                                             |

| 37<br>38                                         | MDATA12<br>MDATA13 | I/O<br>I/O |                   | DRAM data bus 12 DRAM data bus 13                                            |

| 1                                                |                    | +          |                   |                                                                              |

| 39                                               | MDATA14            | 1/0        |                   | DRAM data bus 14                                                             |

| 40                                               | MDATA15            | 1/0        |                   | DRAM data bus 15                                                             |

| 41                                               | RASB               | 0          | Memory interface  | RAS output (active low)                                                      |

| 42                                               | WEB                | 0          |                   | WE output (active low)                                                       |

| 43                                               | CASLB              | 0          |                   | CAS output (lower byte, active low)                                          |

| 44                                               | CASUB              | 0          |                   | CAS output (upper byte, active low)                                          |

| 45                                               | OEB                | 0          |                   | OE output (active low)                                                       |

| 46                                               | MADRS12            | 0          |                   | DRAM address output 12                                                       |

| 47                                               | MADRS11            | 0          |                   | DRAM address output 11                                                       |

| 48                                               | MADRS10            | 0          |                   | DRAM address output 10                                                       |

| 49                                               | MADRS9             | 0          |                   | DRAM address output 9                                                        |

| 50                                               | MADRS8             | 0          |                   | DRAM address output 8                                                        |

Continued on next page.

### Continued from preceding page.

| Pin No. | Pin Name           | I/O      | Block                     | Function                                                                                  |

|---------|--------------------|----------|---------------------------|-------------------------------------------------------------------------------------------|

| 51      | DV <sub>DD</sub> 4 | _        | Danisa                    | Digital I/O system power supply                                                           |

| 52      | V <sub>SS</sub>    | _        | Power supply              | Ground                                                                                    |

| 53      | MADRS7             | 0        |                           | DRAM address output 7                                                                     |

| 54      | MADRS6             | 0        |                           | DRAM address output 6                                                                     |

| 55      | MADRS5             | 0        |                           | DRAM address output 5                                                                     |

| 56      | MADRS4             | 0        | Manager to the desired    | DRAM address output 4                                                                     |

| 57      | MADRS3             | 0        | Memory interface          | DRAM address output 3                                                                     |

| 58      | MADRS2             | 0        |                           | DRAM address output 2                                                                     |

| 59      | MADRS1             | 0        |                           | DRAM address output 1                                                                     |

| 60      | MADRS0             | 0        |                           | DRAM address output 0                                                                     |

| 61      | DV <sub>DD</sub> 5 | _        | Dower ounnly              | Internal logic system power supply                                                        |

| 62      | $V_{SS}$           | _        | Power supply              | GND                                                                                       |

| 63      | STREQ              | I/O      |                           | MP3 data request flag output (active high)                                                |

| 03      | SIREQ              | 1/0      | MP3 stream I/O            | /DRAM data request flag input (CD-ROM mode, active high)                                  |

| 64      | STCK               | I/O      |                           | MP3 data transfer clock input                                                             |

| 04      | SICK               | 1/0      | WIPS Stream I/O           | /DRAM data transfer clock output                                                          |

| 65      | STDAT              | I/O      |                           | MP3 serial data input                                                                     |

| 00      | SIDAI              | 1/0      |                           | /DRAM serial data output                                                                  |

| 66      | FSYNC              | NC O     | MP3-dec                   | MP3 frame sync signal (active high)                                                       |

| 00      | 101110             |          |                           | /Data continuity point detection complete flag (CD-DA mode, active high)                  |

| 67      | CRCF               | 0        | CD monitor                | CRC check result output (CD-ROM data/CD-DA subcode data)                                  |

| 0.      |                    |          |                           | /DRAM data output enable signal output (active high)                                      |

| 68      | DV <sub>DD</sub> 6 | _        | Power supply              | Digital I/O system power supply                                                           |

| 69      | V <sub>SS</sub>    | _        | 1 oner cuppiy             | GND                                                                                       |

| 70      | wok                | 1        |                           | DRAM write enable input (CD-DA mode, active high)                                         |

|         | · · · · ·          |          |                           | /DRAM data request flag input                                                             |

| 71      | CNTOK              | 0        | CD-DA shockproof          | Data continuity point detection complete flag (CD-DA mode, active high)                   |

|         | 0                  | TOIL 0   | and MP3 I/O               | /SYNC error monitor flag (MP3 mode, active high)/DRAM serial data output                  |

|         |                    | F O      |                           | DRAM write interrupt flag (CD-DA mode, active high)                                       |

| 72      | OVF                |          |                           | /Emphasis output flag (CD-DA and MP3 modes, active high)                                  |

|         |                    |          |                           | /DRAM data transfer clock output                                                          |

| 73      | CMDOUT             | 0        |                           | Serial command data output (n-channel open-drain output)                                  |

| 74      | CMDIN              | 1        | Microcontroller interface | Serial command data input                                                                 |

| 75      | CL                 | <u> </u> |                           | Serial command clock input                                                                |

| 76      | CE                 | I        |                           | Command enable input (active high)                                                        |

| 77      | INTB               | 0        |                           | Interrupt signal output (active low) /DRAM write interrupt flag (CD-DA mode, active high) |

| 78      | RESB               | -        |                           | System reset (active low)                                                                 |

| 79      | DATAIN             | i        |                           | System reset (active low) Serial CD data input                                            |

| 80      | DATAIN             | <u> </u> | CD IF                     | ·                                                                                         |

| 00      | DATACK             | ı        |                           | CD bit clock input                                                                        |

Notes: 1. Notes on unused pins.

Unused input pins must be connected to the ground level (0 V).

Unused output pins must be left open. Do not connect anything to these pins.

Unused I/O pins may either be connected to the ground level (0 V) or set to output mode and left open.

- 2. The corresponding power supply levels must be provided to all of the DV<sub>DD</sub>1, DV<sub>DD</sub>3, DV<sub>DD</sub>4, DV<sub>DD</sub>6, and AV<sub>DD</sub> pins. The corresponding power supply level must also be provided to DV<sub>DD</sub>2 and DV<sub>DD</sub>5. (See the Allowable Operating Ranges specifications for the supply levels.)

- 3. The TEST1 and TEST2 input pins must be connected to ground (0 V).

- 4. The I/O pins (MDAT0:15, STREQ, STCK, and STDAT) go to input mode after a reset.

- 5. After first applying the power supply levels, the RESB pin must be held low for at least 1  $\mu s$ .

- 6. A 16.9344 MHz clock signal must be supplied to the CKIN pin by the CD DSP.

The LC78684E does not support the implementation of an oscillator circuit using an oscillator element.

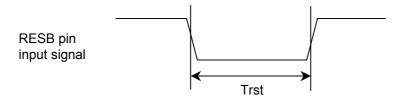

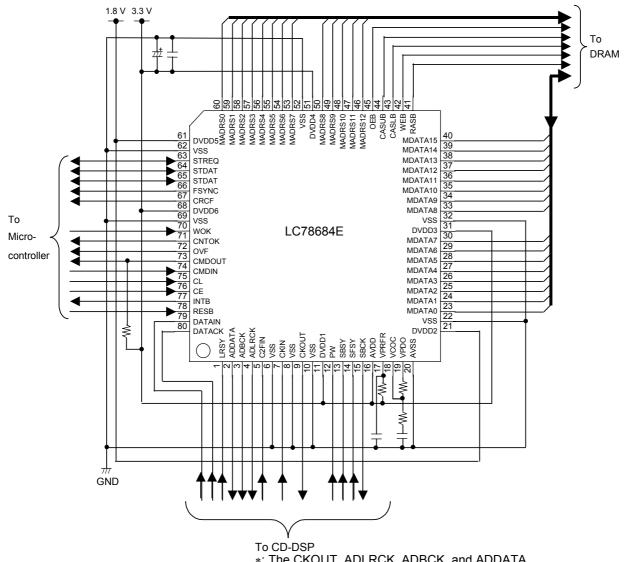

## **Sample Application Circuit**

\*: The CKOUT, ADLRCK, ADBCK, and ADDATA pins must be connected to a CD DSP that supports external D/A converter input.

An external D/A converter is required if the CD DSP does not provide that functionality.

### **Application Design Notes**

While it goes without saying that strictly observing the absolute maximum ratings and allowable operating ranges (recommended operation conditions) stipulated for this IC is necessary to achieve reliability of the overall system, it is also necessary to take adequate care with respect to the mounting conditions and the operating environment, including the ambient temperature and the possibility of electrostatic discharges (ESD). This section presents notes on aspects of design and mounting that require special attention.

### **Handling Unused Pins**

If this IC is operated with unused input pins left open, certain internal circuit operations may become unstable. Unused pins that are mentioned in the IC documentation must be handled as specified. Also, do not allow output pins to come in contact with any circuit lines, including power supply lines, ground lines, or other outputs.

### **Latchup Prevention**

- The voltages stipulated in the IC specifications must be provided to the corresponding power supply pins. When the same voltage is stipulated for multiple pins, those pins all must be connected to the same potential.

- Do not set I/O voltage levels to be either higher than the peripheral 3 V system block voltage, or lower than the ground level. This relationship must also be maintained during the power-on sequence.

- Do not apply overvoltages or abnormal noise to this IC.

- While in general, latchup is prevented by holding unused input pins at either the VDD or VSS potential, input pins to this IC must be handled as described in the pin descriptions.

- Do not short the outputs.

#### Interface

Incorrect operation may result when different devices are connected if the input VIL/VIH and the output VOH and VOH levels do not match. Level shifters must be inserted between devices with differing supply voltages, such as those often used in dual power supply systems, to prevent destruction of the devices.

### **Load Capacitance and Output Current**

- If a large load capacitance is connected, the resulting effective short of the outputs may continue for an extended period and lead to fusing of lines. Also, larger charge and discharge currents can cause noise, degrade device performance, and cause incorrect operation. The recommended load capacitance ratings must be observed.

- Excessive output sink or source currents can lead to the same problems described in the preceding item. Once the allowable power dissipation rating has been met, the recommended current values must be observed as well.

### **Notes on Power Application and Reset**

- There are several aspects that require care when power is first applied, during a reset, and when the reset state is cleared. Refer to the device specifications and design applications to match the product specifications.

- In this IC, the register contents, pin output states, and pin I/O settings are not guaranteed after power is first applied. Items that are defined by the reset operation or mode setting operations are guaranteed after these operations are performed. After power is first applied to this IC, the application must first perform a reset operation. Pin states and register values that are not defined are subject to change, both due to sample-to-sample variations in the product over the long term, and due to changes in device design from the initial design states.

### **Thermal Design**

• Semiconductor device failure rates are greatly accelerated by inappropriate ambient temperature and power consumption conditions. To assure the highest possible reliability, the thermal design should provide ample margins considering all possible changes in the ambient conditions.

### **Notes on PWB Pattern Design**

- In an ideal design, power supply and ground lines will be provided separately for each system to minimize the influence of shared impedances.

- Power supply and ground lines must be made as wide and as short as possible, and the impedance to high frequencies must be made as low as possible. Decoupling capacitors (consisting of two capacitors: one about 0.01 to 1.0 μF and another about 100 to 220 μF) should be inserted between each power supply pin and ground. Note, however, that if this capacitance is too large, it may result in latchup problems.

#### **Other Notes**

If you have any questions or if anything is even slightly unclear, please contact your SANYO sales or technical representative during the design phase. This IC is a special-purpose device for use in CD players, and its specifications differ from those of standard logic ICs and other general-purpose products. Also note that, depending on the application, failsafe measures and/or system level debugging of the total system may be required as well.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of February, 2003. Specifications and information herein are subject to change without notice.