# LC7985NA, LC7985ND

# LCD Controller/Driver

#### Overview

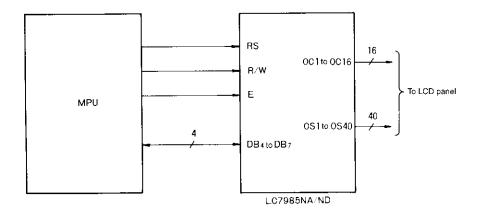

The LC7985 series devices are low-power CMOS ICs that incorporate dot-matrix character generator, display controller and driver functions in a single device, making them ideal for use in portable equipment containing LCD displays.

The LC7985 series feature  $5 \times 7$ -pixel and  $5 \times 10$ -pixel character fonts including either eight or four user-defined characters, single-line and two-line display modes, built-in drivers for displays up to eight characters in size, and easy expansion to control displays of up to 80 characters by adding LC7930N display drivers.

The LC7985 series interface directly to both 4-bit and 8-bit microcontrollers. The instruction set includes display clear, cursor home, display ON/OFF, character blink, and cursor and display shift instructions. The built-in reset circuit automatically initializes the devices at power-ON.

The LC7985 series operate from a 5V supply and are available in 80-pin QIPs.

### **Features**

- · Controller and driver for dot-matrix LCD displays

- $5 \times 7$ -pixel and  $5 \times 10$ -pixel character fonts

- 160, 5 × 7-pixel characters and 32, 5 × 10-pixel characters in character generator ROM

- Eight,  $5 \times 7$ -pixel characters or four,  $5 \times 10$ -pixel characters in character generator RAM

- 80-character display data RAM

- Built-in drivers for 1-line × 8-character and 2-line × 8-character displays

- Easy expansion to 1-line × 80-character or 2-line × 40character displays

- 4-bit or 8-bit microcontroller interface

- 11 microcontroller instructions

- · Built-in reset circuit

- · Built-in oscillator

- 5V supply

- 80-pin QIP

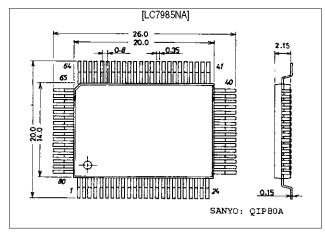

# Package Dimensions

unit: mm

#### 3044B - QFP80A

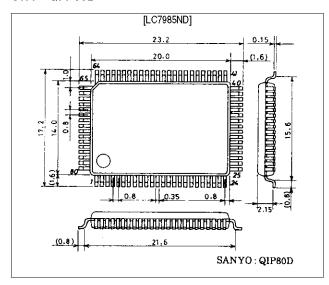

unit: mm

#### 3177 - QFP80D

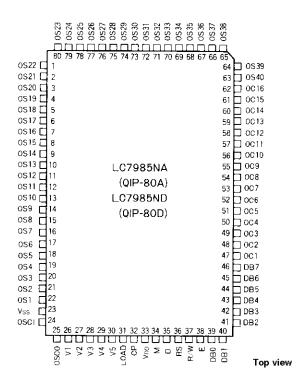

# Pin Assignment

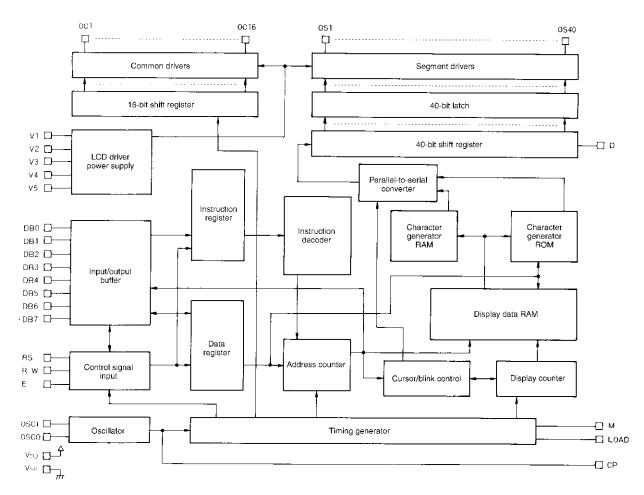

# **Block Diagram**

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25 \pm 2$ °C, $V_{SS} = 0$ V

| Parameter                        | Symbol                           | Ratings                                         | Unit |

|----------------------------------|----------------------------------|-------------------------------------------------|------|

| Supply voltage range             | V <sub>DD</sub>                  | -0.3 to +7.0                                    | ٧    |

| LCD drive supply voltage range*1 | V <sub>1</sub> to V <sub>5</sub> | V <sub>DD</sub> - 13.5 to V <sub>DD</sub> + 0.3 | ٧    |

| Input voltage range              | V <sub>I</sub>                   | -0.3 to V <sub>DD</sub> + 0.3                   | ٧    |

| Operating temperature range      | Topr                             | -20 to +75                                      | °C   |

| Storage temperature range        | Tstg                             | -55 to +125                                     | °C   |

Note: \*1.  $V_{DD}$  must obey the relationship :  $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5$

# Allowable Operating Ranges at $Ta = -20 \text{ to } +75^{\circ}\text{C}$

| Parameter                 | Symbol           | Conditions              | Ratings               |     |                        | Unit |

|---------------------------|------------------|-------------------------|-----------------------|-----|------------------------|------|

| raiaileiei                | Symbol           | Conditions              | min                   | typ | max                    | Olik |

| Supply voltage range      | V <sub>DD</sub>  |                         | 4.5                   |     | 5.5                    | ٧    |

| Supply voltage*1          | V <sub>D5</sub>  | $V_{D5} = V_{DD} - V_5$ | 1.5                   |     |                        | ٧    |

| Supply vollage            | V <sub>D1</sub>  | $V_{D1} = V_{DD} - V_1$ |                       |     | V <sub>D5</sub> x 0.25 | ٧    |

| Input high level voltage  | V <sub>IH1</sub> | except OSCI             | 2.2                   |     | V <sub>DD</sub>        | ٧    |

| input fight level voltage | V <sub>IH2</sub> | OSCI only               | V <sub>DD</sub> - 1.0 |     | V <sub>DD</sub>        | ٧    |

| Input low level voltage   | V <sub>IH1</sub> | except OSCI             |                       |     | 0.6                    | ٧    |

| Input low level voltage   | V <sub>IH2</sub> | OSCI only               |                       |     | 1.0                    | ٧    |

Note: \*1. These voltages guarantee correct operation of the LC7985NA and LC7985ND. They do not guarantee correct operation of the LCD panel. V<sub>LCD</sub> must also be observed.

# **Electrical Characteristics** at Ta = -20 to +75°C, $V_{SS} = 0$ V, $V_{DD} = 5$ V $\pm 10$ %, unless otherwise noted

| Parameter                  | Symbol           | Conditions                                                                                          |                    | Ratings |                    | Unit  |  |

|----------------------------|------------------|-----------------------------------------------------------------------------------------------------|--------------------|---------|--------------------|-------|--|

| raidilletei                | Зупірої          | Conditions                                                                                          | min                | typ     | max                | Olik  |  |

| Output high-level voltage  | V <sub>OH1</sub> | I <sub>OH</sub> = -0.205mA<br>Input / Output pins                                                   | 2.4                | _       | _                  | ٧     |  |

|                            | V <sub>OH2</sub> | I <sub>OH</sub> = -0.04mA Output pins                                                               | 0.9V <sub>DD</sub> | -       | -                  | ٧     |  |

| Output low-level voltage   | V <sub>OL1</sub> | I <sub>OL</sub> = 1.2mA<br>Input / Output pins                                                      | _                  | _       | 0.4                | ٧     |  |

|                            | V <sub>OL2</sub> | I <sub>OL</sub> = 0.04mA Output pins                                                                | -                  | -       | 0.1V <sub>DD</sub> | ٧     |  |

| Driver fall voltage*1      | V <sub>COM</sub> | I <sub>d</sub> = 0.05mA<br>All common pins                                                          | _                  | _       | 2.9                | ٧     |  |

| Driver rail voltage        | V <sub>SEG</sub> | I <sub>d</sub> = 0.05mA<br>All segment pins                                                         | _                  | _       | 3.8                | ٧     |  |

| Leakage current            | I <sub>L</sub>   | $V_I = V_{SS}$ to $V_{DD}$                                                                          | -                  | -       | 1                  | μA    |  |

| Pull-up current*2          | I <sub>P</sub>   | V <sub>DD</sub> = 5V                                                                                | 50                 | 125     | 250                | μA    |  |

| Current drain              | I <sub>DD1</sub> | Ceramic resonator oscillator, $V_{DD}$ = 5V, $f_{OSC}$ = 250kHz, no output load                     | _                  | 0.55    | 0.8                | - mA  |  |

| Current crain              | I <sub>DD2</sub> | Feedback resistor oscillator,<br>V <sub>DD</sub> = 5V, f <sub>OSC</sub> = 270kHz,<br>no output load | -                  | 0.35    | 0.6                | 111/4 |  |

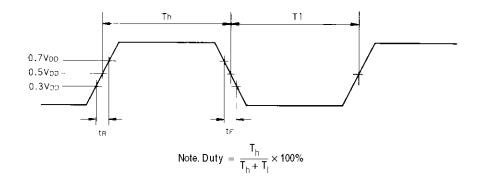

| External clock*3 Frequency | f <sub>CP</sub>  |                                                                                                     | 125                | 250     | 350                | kHz   |  |

| Duty cycle                 | DUTY             |                                                                                                     | 45                 | 50      | 55                 | %     |  |

| Rise time                  | t <sub>R</sub>   |                                                                                                     | -                  | -       | 0.2                | μs    |  |

| Fall time                  | t <sub>F</sub>   |                                                                                                     | 0.2                |         |                    |       |  |

## LC7985NA, LC7985ND

| Parameter                     | Symbol            | Conditions                                                      | Ratings |     |     | Unit |  |

|-------------------------------|-------------------|-----------------------------------------------------------------|---------|-----|-----|------|--|

| raidilletei                   | Symbol            | Conditions                                                      | min     | typ | max | Oilk |  |

|                               | f <sub>OSC1</sub> | Ceramic filter oscillator                                       | 245     | 250 | 255 |      |  |

| Internal oscillator frequency | f <sub>OSC2</sub> | Feedback resistor oscillator,<br>$R_{\rm f}$ = 91k $\Omega$ ±3% | 190     | 270 | 350 | kHz  |  |

| LCD display voltage           | V <sub>LCD1</sub> | 1/5 bias, V <sub>LCD</sub> = V <sub>DD</sub> - V <sub>5</sub>   | 4.6     | -   | 11  | V    |  |

| LCD display voltage           | V <sub>LCD2</sub> | 1/4 bias, $V_{LCD} = V_{DD} - V_5$                              | 3.0     | _   | 11  | 7 4  |  |

Note: \*1. V<sub>COM</sub> is the voltage from VDD, V1, V4 and V5 to the LCD common drive pins OC1 to OC16. V<sub>SEG</sub> is the voltage from VDD, V2, V3 and V5 to the LCD segment drive pins OC1 to OC40. Note: \*2. Applied pins are RS, R/W, and DB0 to DB7.

Note: \*3. External clock

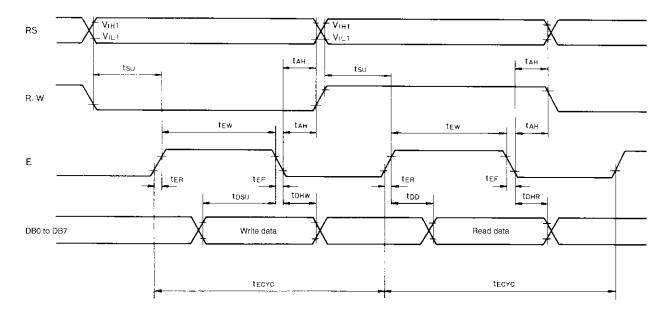

# Switching Characteristics at Ta = -20 to +75°C, VDD = $5V \pm 10\%$ , VSS = 0V

| Parameter                                  | Symbol            | Conditions               |       | Ratings |      | Unit |

|--------------------------------------------|-------------------|--------------------------|-------|---------|------|------|

| raidiletei                                 | Symbol            | Conditions               | min   | typ     | max  | Oill |

| E cycle time                               | t <sub>ECYC</sub> |                          | 1000  | _       | _    | ns   |

| E high-level pulsewidth                    | t <sub>EW</sub>   |                          | 450   | _       | _    | ns   |

| E rise time                                | t <sub>ER</sub>   |                          | -     | _       | 25   | ns   |

| E fall time                                | t <sub>EF</sub>   |                          | -     | _       | 25   | ns   |

| RS and R/W to E setup time                 | t <sub>SU</sub>   |                          | 140   | _       | _    | ns   |

| E to RS and R/W address hold time          | t <sub>AH</sub>   |                          | 10    | _       | _    | ns   |

| DB0 to DB7 to E data setup time            | t <sub>DSU</sub>  |                          | 195   | -       | _    | ns   |

| Write cycle E to DB0 to DB7 data hold time | t <sub>DHW</sub>  |                          | 10    | -       | -    | ns   |

| Read cycle E to data valid delay time      | t <sub>DD</sub>   | See measurement circuit. | -     | _       | 320  | ns   |

| Read cycle E to DB0 to DB7 data hold time  | t <sub>DHR</sub>  |                          | 20    | -       | _    | ns   |

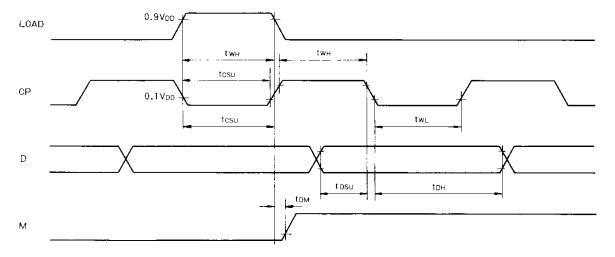

| CP low-level pulsewidth                    | t <sub>WL</sub>   |                          | 800   | _       | _    | ns   |

| CP high-level pulsewidth                   | t <sub>WH</sub>   |                          | 800   | _       | -    | ns   |

| CP to LOAD setup time                      | t <sub>CSU</sub>  |                          | 500   | _       | _    | ns   |

| D to CP data setup time                    | t <sub>DSU</sub>  |                          | 300   | _       | _    | ns   |

| CP to D data hold time                     | t <sub>DH</sub>   |                          | 300   | _       | -    | ns   |

| LOAD to M delay time                       | t <sub>DM</sub>   |                          | -1000 | _       | 1000 | ns   |

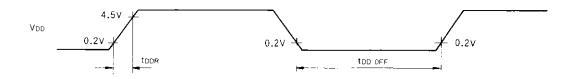

## Reset characteristics at $Ta = -20 \text{ to } +75^{\circ}\text{C}$

| Parameter                 | Symbol             | Conditions |     |     | Unit |       |

|---------------------------|--------------------|------------|-----|-----|------|-------|

| raidilietei               | Symbol             | Conditions | min | typ | max  | O III |

| V <sub>DD</sub> rise time | t <sub>DDR</sub>   |            | 0.1 | -   | 10   | μs    |

| V <sub>DD</sub> off time  | t <sub>DDOFF</sub> |            | 1   | -   | -    | ms    |

# **Clock Generator**

The internal oscillator that generates the clock for the internal circuit requires an external filter, a feedback resistor or an external clock input as shown in the following sections.

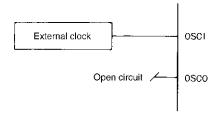

## **External clock**

The input duty cycle should be between 45 and 55% as shown in the following figure.

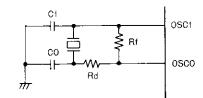

# **Ceramic filter**

Note. Rf  $\,$  = 1M  $\Omega$   $\pm$  10%, Cl = CO = 680pF  $\pm$  10%, Rd = 3.3k  $\Omega$   $\pm$  5%

## Feedback resistor

Note. The resistor should be mounted as close as possible to OSCI and OSCO.

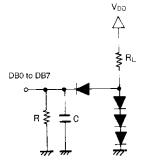

# **Measurement Circuit**

Note,  $R_L$  = 2.4k $\Omega,$  C = 130pF, R = 11k $\Omega$

# Read/write cycle timing

# LC7930N interface timing

# **Power supply**

# LC7985NA, LC7985ND

# Pin Description

| Name                                | Num | I/O | Connect to | Functions                                                                                                                                                                            |

|-------------------------------------|-----|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS                                  | 1   | I   | MPU        | Data register or instruction register select input. Data register when "1" and instruction register when "0".                                                                        |

| RW                                  | 1   | I   | MPU        | Read or write select input "0" indicates write, "1"; read                                                                                                                            |

| E                                   | 1   | I   | MPU        | Execution start input to write or read                                                                                                                                               |

| DB <sub>4</sub> to DB <sub>7</sub>  | 4   | I/O | MPU        | 4-bit microcontroller interface data bus and 8-bit microcontroller interface high-order four bits data bus connections. Three-state bidirectional DB $_7$ can be used as a busyflag. |

| DB <sub>0</sub> to DB <sub>3</sub>  | 4   | 1/0 | MPU        | 8-bit microcontroller interface low-order four bits data bus connections. No connection when 4-bit interface size is selected. Three-state bidirectional.                            |

| LOAD                                | 1   | 0   | LC7930N    | Clock to latch the D serial data output to LC 7930N                                                                                                                                  |

| CP                                  | 1   | 0   | LC7930N    | Clock to shift the D serial data                                                                                                                                                     |

| М                                   | 1   | 0   | LC7930N    | Output to shift the LCD drive signal to alternating current signal                                                                                                                   |

| D                                   | 1   | 0   | LC7930N    | Display expansion serial data output "0" indicates unselected, "1"; selected                                                                                                         |

| OC <sub>1</sub> to OC <sub>16</sub> | 16  | 0   | LCD        | LCD common driver outputs. All common signals unused are unselected wave forms.                                                                                                      |

| OS <sub>1</sub> to OS <sub>40</sub> | 40  | 0   | LCD        | LCD segment driver outputs                                                                                                                                                           |

| V <sub>1</sub> to V <sub>5</sub>    | 5   |     | source     | Supply voltage for LCD display drive                                                                                                                                                 |

| V <sub>DD</sub> , V <sub>SS</sub>   | 2   |     | source     | V <sub>DD</sub> :+5V, V <sub>SS</sub> : 0V                                                                                                                                           |

| OSCI, OSCO                          | 2   |     |            | Oscillator feedback resistor and ceramic filter connection, and external clock input                                                                                                 |

# **Functional Description**

### Registers

The LC7985 has two 8-bit registers—instruction register (IR) and data register (DR)—that are selected as shown in the following table.

| RS | R/W | Operation                                               |

|----|-----|---------------------------------------------------------|

| 0  | 0   | IR write, instruction execution                         |

| 0  | 1   | Busy flag (DB7) and address counter (DB0 to DB6) output |

| 1  | 0   | DR write, internal DR to DD RAM or CG RAM data transfer |

| 1  | 1   | DR read, internal DD RAM or CG RAM to DR data transfer  |

The instruction register is write-only. It contains instruction codes or DD RAM and CG RAM addresses written by the microcontroller.

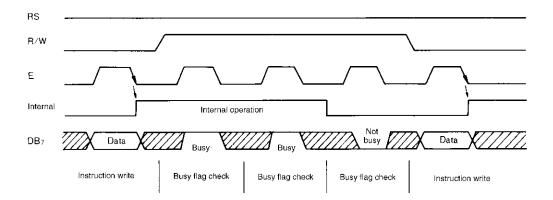

# **Busy Flag**

When busy flag is 1, the previous instruction is executing, and when 0, the instruction has completed. The next instruction cannot be received until BF is 0. The microcontroller should, therefore, confirm that BF is 0 before writing the next instruction.

## Display Data RAM (DD RAM)

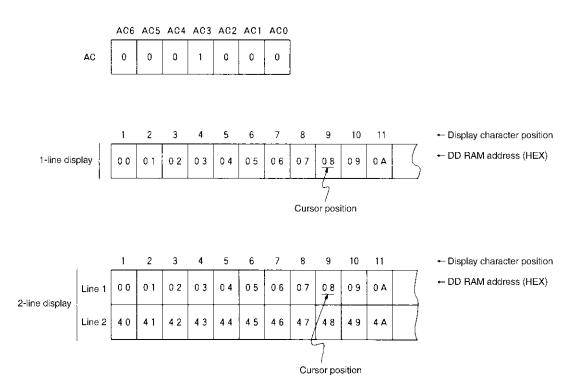

The display data RAM stores 80, 8-bit character codes, and the LC7985 can display a maximum of 80 characters. The address counter contains the location for the next display memory read or write operation as shown in the following figure.

The data register holds data read from or written to either DD RAM or CG RAM. Data written to the data register by the microcontroller is automatically transferred to the current DD RAM or CG RAM address. Data read from DD RAM or CG RAM is buffered in the data register.

When the microcontroller writes a DD RAM or CG RAM address to the instruction register, the data at that address is copied into the data register. The microcontroller then reads the data in the data register to complete the transfer. Once that data is read, the data from the next DD RAM or CG RAM address is copied into the data register in preparation for the next data read.

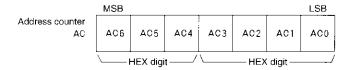

#### **Address Counter**

The address counter is used for both the DD RAM and the CG RAM. The address output on DB0 to DB7 is the counter value before the currently executing instruction began.

Display data addresses are in hexadecimal. For example, the address counter contents for location 4E are shown in the following figure.

To prevent undesirable effects such as display flicker during DD RAM accesses, the internal memory and the microprocessor interface have separate timing signals.

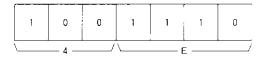

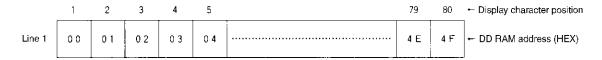

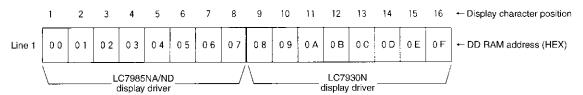

### Single-line display mode (N = 0)

The DD RAM addresses and their corresponding display positions for an 80-character display are shown in the following figure.

A single LC7985, however, can drive up to eight characters. The display positions and DD RAM addresses for an unshifted 8-character display are shown in the following figure.

|        | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | ← Display character position |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|------------------------------|

| Line 1 | 0.0 | 0 1 | 0 2 | 0 3 | 0 4 | 0 5 | 0 6 | 0.7 | ← DD RAM address (HEX)       |

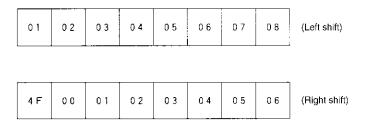

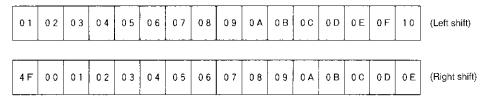

The DD RAM addresses following left and right display shifts are shown in the following figure. Note that the displayed characters wrap around from addresses  $4F_H$  to  $00_H$ .

An LC7985 and a single LC7930N can drive a 16-character display. The display positions and DD RAM addresses for an unshifted display are shown in the following figure.

The DD RAM addresses following left and right display shifts are shown in the following figure.

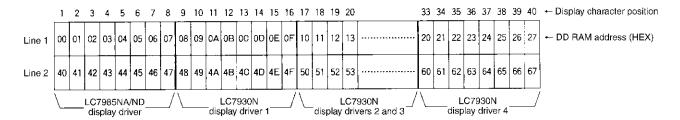

The number of displayed characters can be increased by adding more LC7930Ns. An LC7985 and nine LC7930Ns can drive an 80-character display as shown in the following figure.

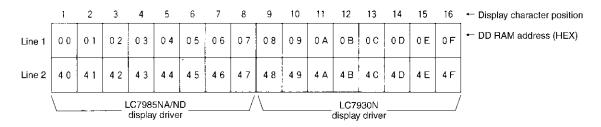

## Two-line display mode (N = 1)

The DD RAM addresses and their corresponding display positions for a 2-line  $\times$  40-character display are shown in the following figure. Note that the address counter automatically increments from  $27_{\rm H}$  to  $40_{\rm H}$ .

|        | 1   | 2  | 3   | 4  | 5   | 39     | 40        | ← Display character position |

|--------|-----|----|-----|----|-----|--------|-----------|------------------------------|

| Line 1 | 00  | 01 | 02  | 03 | 0 4 | <br>26 | l<br>  27 | ← DD RAM address (HEX)       |

| Line 2 | 4 0 | 41 | 4 2 | 43 | 4 4 | 66     | 67        |                              |

A single LC7985, however, can drive up to eight characters per line. The display positions and DD RAM addresses for an unshifted, 2-line  $\times$  8-character display are shown in the following figure.

|        | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | - Display character position |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|------------------------------|

| Line 1 | 00  | 01  | 0 2 | 03  | 0 4 | 05  | 06  | 07  | ← DD RAM address (HEX)       |

| Line 2 | 4 0 | 4 1 | 4 2 | 4 3 | 4 4 | 4.5 | 4 6 | 4 7 |                              |

The display positions following a left or right display shift are shown in the following figure. Note that the display shift is simultaneous for both lines, regardless of which line the cursor is in.

| (Left shift)  | 0.8 | 07  | 0 6 | 0 5 | 0 4 | 0 3 | 0 2 | 0 1 |  |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--|

|               | 4 8 | 47  | 46  | 4 5 | 4 4 | 43  | 4 2 | 4 1 |  |

|               |     |     |     |     |     |     |     |     |  |

| (Right shift) | 06  | 0 5 | 04  | 0.3 | 0 2 | 01  | 00  | 2 7 |  |

|               | 46  | 4 5 | 4 4 | 4 3 | 4 2 | 4 1 | 40  | 6 7 |  |

An LC7985 and a single LC7930N can drive a 2-line × 16-character display. The display positions and DD RAM addresses for an unshifted, 2-line × 16-character display are shown in the following figure.

The DD RAM addresses following left and right display shifts are shown in the following figure.

| 0 1 | 0 2 | 0 3 | 0 4 | 0 5 | 06  | 0 7 | 08  | 0 9 | 0 A | 0 B | 0 C | 0 D | 0 E | 0F  | 10 | (Left shift)  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|---------------|

| 4 1 | 42  | 43  | 4 4 | 4 5 | 46  | 4 7 | 48  | 49  | 4 A | 4B  | 4 C | 4 D | 4 E | 4 F | 50 | (Left Sillit) |

|     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |    |               |

| 2 7 | 00  | 01  | 02  | 0 3 | 04  | 05  | 0.6 | 07  | 0.8 | 09  | 0 A | 0 B | 0 C | 0 D | 0E | (Right shift) |

| 6 7 | 40  | 41  | 4 2 | 4 3 | 4 4 | 45  | 4 6 | 4 7 | 48  | 49  | 4 A | 4 B | 4 C | 4 D | 4E | (rugin siin)  |

## LC7985NA, LC7985ND

The number of displayed characters can be increased by adding more LC7930Ns. An LC7985 and four LC7930Ns can drive a 2-line × 40-character display as shown in the following figure.

## Character Generator ROM (CG ROM)

The character generator ROM contains 160,  $5 \times 7$ -pixel bitmaps and 32,  $5 \times 10$ -pixel bitmaps as shown in the following figure. The characters are selected by their 8-bit character code.

## Character Generator RAM (CG RAM)

The character generator RAM stores user-defined bitmaps for either eight,  $5 \times 7$ -pixel characters or four,  $5 \times 10$ -pixel characters. To display character patterns stored in CG RAM, write the character codes, shown in the leftmost column of the following figure, on DD RAM.

# Character cord and the character bitmap

| Upper      |                  |      |       |      |          |          | ·           |       | -     |          |                  |              |                                                                                                                        |

|------------|------------------|------|-------|------|----------|----------|-------------|-------|-------|----------|------------------|--------------|------------------------------------------------------------------------------------------------------------------------|

| Lower 4bit | ប្រក្រប          | 0010 | 0011  | 0100 | 0101     | 0110     | 0111        | 1010  | 1011  | 1100     | 1101             | 1110         | 1111                                                                                                                   |

| ××××0000   | CG<br>RAM<br>(1) |      |       |      |          | *••      | ****        |       |       |          | ••••             |              |                                                                                                                        |

| ××××0001   | (2)              | i    | ***   |      |          |          | -:::        |       |       |          | ·:               | •            |                                                                                                                        |

| ××××0010   | (3)              | 11   | •     | •••• |          |          | <b>!.".</b> |       | •••   | <u> </u> | .:: <sup>1</sup> |              |                                                                                                                        |

| ××××0011   | (4)              |      |       |      |          | :        | -::-        |       |       |          |                  | :::.         | :::7                                                                                                                   |

| ××××0100   | (5)              | :::- |       |      | *****    |          |             | •••   |       |          | -                |              | :::                                                                                                                    |

| ××××0101   | (6)              |      |       |      |          |          | 1           | **    |       |          |                  |              | ii                                                                                                                     |

| ××××0110   | (7)              |      | ::::  |      | <b>.</b> |          | i.,!        | ***** |       | ****     |                  |              |                                                                                                                        |

| xxxx0111   | (8)              | :    |       |      |          |          | 1,,1        |       |       | ;::;     |                  |              | .11.                                                                                                                   |

| ××××1000   | (1)              |      |       |      |          |          |             | .:    |       |          | į.               |              |                                                                                                                        |

| ****!##!   | (2)              |      |       |      | ::       | <u>:</u> | ••          |       |       | ,        |                  | :            |                                                                                                                        |

| ××××1010   | (3)              | :#:  | ::    |      |          |          | •••••       | ••••  | ***** |          |                  |              |                                                                                                                        |

| ××××1011   | (4)              |      | ;;    |      |          |          |             | ::    |       |          |                  | <b>::</b>    | :::                                                                                                                    |

| ××××1100   | (5)              | ;;   |       |      |          | 930      |             |       | ***   |          |                  | :::-         |                                                                                                                        |

| ××××1101   | (6)              |      | 04041 |      | ***      |          |             |       |       | ••••     |                  |              | -                                                                                                                      |

| ××××1110   | (7)              |      |       |      |          |          | -:          | ****  |       |          | •••              | 1."          |                                                                                                                        |

| ××××1111   | (8)              |      |       |      | *****    |          | -;          | : 1;  | •     |          |                  | : <u>"</u> : | 944 P4<br>94 9 19<br>14 5 2 49<br>95 2 91<br>95 2 91<br>95 2 91<br>19 2 19<br>19 2 19<br>19 2 19<br>19 2 19<br>19 2 19 |

#### $5 \times 7$ -pixel characters

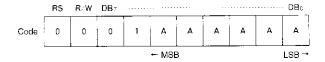

The layout and addressing for  $5 \times 7$ -pixel characters is shown in the following figure. Each character occupies eight bytes, where bits 3 to 5 of the CG RAM address correspond to bits 0 to 2 of the character code. Note that bit 3 of the character code is not significant so, for example, codes  $00_{\rm H}$  and  $08_{\rm H}$  select the same character.

Bits 0 to 2 of the CG RAM address are the bitmap row address, where row 000 is the topmost displayed row.

The cursor, when displayed, is formed by ORing the bottom row with all 1s. If the cursor is used, row 111 should contain all 0s so the cursor does not obscure the bottom row of the character.

Bits 0 to 4 of the CG RAM data contain the character bitmaps. When a bit is 1, the corresponding pixel is ON, and when 0, the pixel is OFF.

Bits 5 to 7 of the CG RAM data are present in memory, but are not used by the display circuit. These bits can be used as general-purpose RAM.

| Character code<br>(DD RAM data) | CG RAM address                              | Character bitmap<br>(CG RAM data)                                                                               |                    |

|---------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|

| 7 6 5 4 3 2 1 0<br>←MSB LSB→    | 5 4 3 2 1 0<br>MSB LSB                      | 7 6 5 4 3 2 1 0<br>-MSB LSB-                                                                                    |                    |

| 0 0 0 0 * 0 0 0                 | 0 0 0<br>0 0 1<br>0 1 0<br>0 0 1 1<br>1 0 0 | * * * 1 1 1 1 0<br>1 0 0 0 1<br>1 0 0 0 1<br>1 1 1 1 0<br>1 0 1 0                                               | Character bitmap 1 |

|                                 | 1 1 0                                       | * * * 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                         | ← Cursor position  |

| 0 0 0 0 * 0 0 1                 | 0 0 0 0 0 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1     | * * * 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 0 1 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | Character bitmap 2 |

|                                 | 0 0 0 0 0 0 0 1                             | * * *                                                                                                           |                    |

| 0 0 0 0 * 1 1 1 * Don't care    | 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 1 1 1 1     | * * *                                                                                                           |                    |

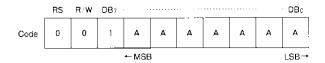

#### $5 \times 10$ -pixel characters

The layout and addressing for  $5\times 10$ -pixel characters is shown in the following figure. Each character occupies eleven bytes, where bits 4 and 5 of the CG RAM address correspond to bits 1 and 2 of the character code. Note that bits 0 and 3 of the character code are not significant so, for example, codes  $00_{\rm H},\,01_{\rm H},\,08_{\rm H}$  and  $09_{\rm H}$  all select the same character.

Bits 0 to 3 of the CG RAM address are the bitmap row address where row 000 is the topmost displayed row.

The cursor, when displayed, is formed by ORing the bottom row with all 1s. If the cursor is used, row 1010 should

contain all 0s so the cursor does not obscure the bottom row of the character.

Bits 0 to 4 of the CG RAM data contain the character bitmaps. When a bit is 1, the corresponding pixel is ON, and when 0, the pixel is OFF.

Bits 5 to 7 of the CG RAM data are present in memory, but are not used by the display circuit. These bits and the CG RAM bytes, rows 1011 to 1111 that are not used by the display circuit, can be used as general-purpose RAM.

|   |          |   |   | raci<br>RA |    |   |   |         |           |         |                 | CG I      | RAM | 1 add | dress    | 3               |   |                 | (         | Chai<br>(CG | racte<br>i RA | r bit<br>M da | mar<br>ata) | )       |         |                   |

|---|----------|---|---|------------|----|---|---|---------|-----------|---------|-----------------|-----------|-----|-------|----------|-----------------|---|-----------------|-----------|-------------|---------------|---------------|-------------|---------|---------|-------------------|

| 7 | 6<br>MSB |   | 5 | 4          |    | 3 | 2 | 1<br>LS | 0<br>•B → |         | 5<br><b>←</b> N | 4<br>JISB | 3   | 2     | 1<br>LSI | 0<br>3 <b>→</b> |   | 7<br><b>←</b> N | 6<br>//SB | 5           | 4             | 3             | 2           | 1<br>LS | 0<br>в→ |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | : 0 | 0     | 0        | 0               |   | *               | *         | *           | 0             | 0             | 0           | 0       | 0       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 0   | 0     | 0        | 1               |   |                 | ŧ         |             | 0             | 0             | 0           | 0       | 0       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 0   | 0     | 1        | 0               |   |                 |           |             | 1             | 0             | 1           | 1       | 0       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 0   | 0     | 1        | 1               |   |                 |           |             | 1             | 1             | 0           | 0       | 1       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 0   | 1     | 0        | Ô               |   |                 |           |             | 1             | 0             | 0           | 0       | 1       | Character bitmap  |

| 0 | 0        | ( | ) | 0          | *  | k | 0 | 0       | *         |         | 0               | 0         | 0   | 1     | 0        | 1               |   |                 |           |             | : 1           | 0             | 0           | 0       | 1       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 0   | 1     | 1        | 0               |   |                 |           |             | 1             | 1             | 1           | . 1     | 0       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 0   | 1     | 1        | 1               |   |                 |           |             | 1             | 0             | 0           | 0       | Ð       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 0     | 0        | 0               |   |                 | i         |             | 1             | 0             | 0           | 0       | 0       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 0     | G        | 1               |   |                 | į         |             | 1             | 0             | 0           | 0       | 0       |                   |

|   |          |   |   |            |    |   |   |         |           | ļ       |                 |           | 1   | 0     | .1.      | 0.              |   | *               | *         | *           | 0             | 0             | 0           | 0       | 0       | ← Cursor position |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 0     | 1        | 1               |   | *               | *         | *           | *             | *             | *           | *       | *       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 1     | С        | 0               |   |                 | 1         |             |               |               | İ           |         |         |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 1     | С        | 1               |   |                 | !         |             |               |               |             |         |         |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 1     | 1        | 0               |   |                 | į         |             |               |               | +           |         |         |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 1     | 1        | 1               |   | *               | *         | *           | *             | *             | *           | *       | *       |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 0   | 0     | O        | 0               |   | *               | *         | *           |               |               |             |         |         |                   |

|   |          |   |   |            | _  | _ |   | _       |           |         |                 |           | 0   | 0     | 0        | 1               |   |                 |           |             |               |               |             |         |         | ]<br>             |

| ر |          | - | ` | 2          | -1 |   | 4 | 1       |           |         | 4               | •         |     |       |          | <u> </u>        |   |                 |           |             |               |               |             |         |         |                   |

| 0 | 0        | ( | J | Û          | k  | , | 1 | 1       | *         |         | 1               | 1         | 1   | 0     | 0        | 1               |   |                 |           | .1.         |               |               |             |         |         |                   |

|   |          |   |   |            |    |   |   |         |           | <i></i> |                 |           | 1   | 0     |          | 0               |   | *               | ·*        | *           |               |               |             |         |         |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 0     | 1        | 1               |   | *               | *         | *           | *             | *             | *           | *       | *       |                   |

|   |          |   |   |            |    |   |   |         |           | i<br>I  |                 |           | 1   | 1     | 0        | 0               |   |                 | i         |             |               |               |             |         |         |                   |

|   |          |   |   |            |    |   |   |         |           |         |                 |           | 1   | 1     | 0        | 1               | : | :               |           |             |               |               |             |         |         |                   |

|   |          |   |   |            |    |   |   |         |           |         | !               |           | 1   | 1     | 1        | 0               |   |                 |           |             |               |               | 1           |         |         |                   |

|   |          |   |   |            |    |   |   |         |           | :       | <u> </u>        |           | : 1 | 1     | 1        | 1               |   | *               | *         | *           | *             | *             | *           | *       | *       |                   |

\* Don't care

## **Timing Generator**

This circuit generates timing signals both for internal circuit operation and for driving external LC7930Ns. The timing signals for the DD RAM, CG ROM and CG RAM are independent of the microcontroller interface so that memory accesses by the microcontroller do not cause interference with the display drive signals.

## **Display Drivers**

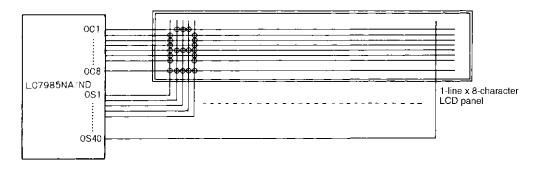

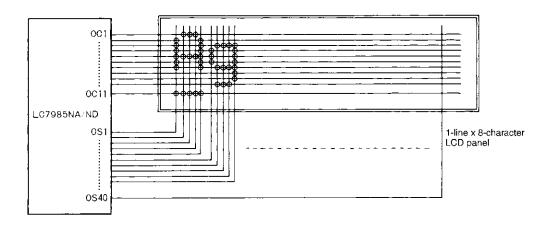

The LC7985 incorporates 16 LCD common driver outputs and 40 LCD segment driver outputs. The character font and the number of display lines determine the number of active common outputs.

The segment drivers function identically to the LC7930N display drivers. The character bitmap data to be displayed is latched in the internal 40-bit shift register before being output on the segment drivers.

The display bitmap data for each pixel-row is generated starting with the right-most character position. The data shifts through the shift register and is output on the shift register serial data output. The shift register latches the last 40 bits in the row so the LC7985 displays the left-most eight characters. External LC7930Ns connect in series to the serial data output and each one latches and displays bitmap data for eight additional characters.

## **Cursor Display and Blinking**

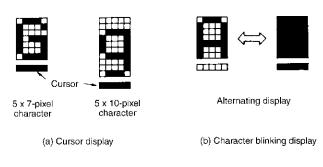

Cursor display and blinking of the character at the cursor position are controlled using the Display ON/OFF instruction. The cursor position is at the character corresponding to the address counter value as shown in the following fig-

ure. Note that the cursor and blinking character are also displayed at the address counter value when CG RAM is selected.

#### Microcontroller Interface

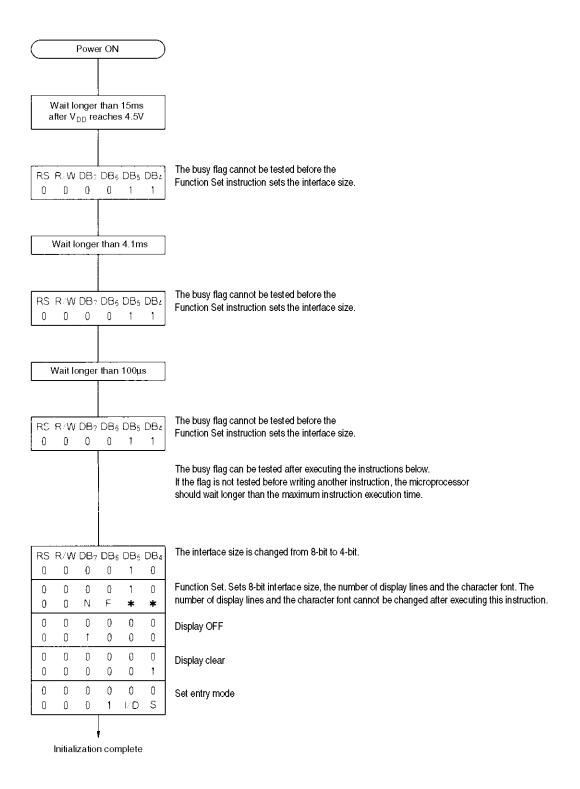

The LC7985 interfaces to both 4-bit and 8-bit microcontrollers.

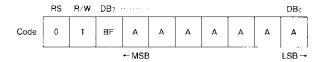

DB0 to DB7 are used for the 4-bit data bus. Two read or write cycles, therefore, are required to transfer each data,

status or instruction byte. The high-order four bits—bits DB4 to DB7 in 8-bit interface mode—are transferred first. The low-order four bits are then transferred as shown in the following figure.

### **Reset Circuit**

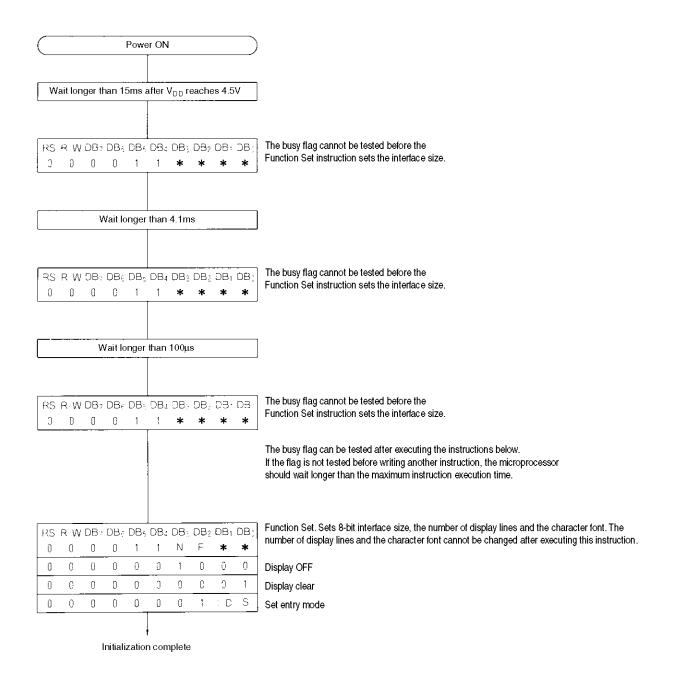

The internal reset circuit initializes the LC7985 at power-ON. The busy flag remains ON from power-ON until initialization is complete 10ms after  $V_{DD}$  reaches 4.5V. Note that if power supply conditions are such that the internal reset circuit does not operate to initialize the device, the LC7985 must be initialized using commands from the microcontroller.

The initialization sequence is as follows.

- 1. Clear Display

- Set Function (D/L = 1, N = 0, F = 0)

Sets 8-bit interface size, 1-line display size and 5 × 7-pixel character font.

- 3. Cursor/Display Control (D = 0, C = 0, B = 0) Sets the display, the cursor and character blinking OFF.

- 4. Set Entry Mode (I/D = 1, S = 0)

Sets address counter auto-increment and sets display shift OFF.

#### Instructions

The external microcontroller accesses two register—instruction register and data register—to control the LC7985. So the microcontroller interface is independent of the microcontroller clock frequency, the LC7985 stores the instruction of data internally before executing it.

There are four types of instructions.

- Function set instructions such as display type or interface size set

- Address set instructions

- Data read and write instructions

- · Other instructions

The Busy Flag/Address Read instruction is the only instruction that can be executed while the LC7985 is executing a previous instruction. Before transmitting any other instruction, the microcontroller should either check that the busy flag is OFF or else wait longer than the execution time of the previous instruction.

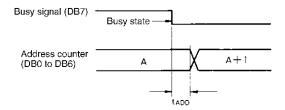

Data read and write instructions are usually the most frequently used instructions. For increased microcontroller efficiency, a display shift and display data write can be executed simultaneously. In addition, the address counter automatically increments or decrements after either a data read or data write instruction, which reduces the operations required by the microcontroller. Note that the increment or decrement occurs after the busy flag turns OFF. The delay until the address counter updates is  $t_{\rm ADD} = 1.5/t_{\rm CP}$  or  $t_{\rm ADD} = 1.5/t_{\rm OSC}$ , and is shown in the following figure.

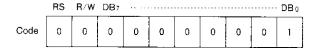

The instructions are shown in the following table. The instruction code comprises the RS, R/W and DB0 to DB7 signals.

| landari di n           |                                                        |                                                               |                                             |                   | Co  | xde                                                                                                                                                                                    |                                                                                                                                                                                              |                  |     |     | December 1                                                                                                                                                                                                                         | Execution time 1 (max)                         |

|------------------------|--------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Instruction            | RS                                                     | R/W                                                           | DB7                                         | DB6               | DB5 | DB4                                                                                                                                                                                    | DB3                                                                                                                                                                                          | DB2              | DB1 | DB0 | Description                                                                                                                                                                                                                        | (f <sub>CP</sub> or f <sub>OSC</sub> = 250kHz) |

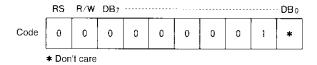

| Display Clear          | 0                                                      | 0                                                             | 0                                           | 0                 | 0   | 0                                                                                                                                                                                      | 0                                                                                                                                                                                            | 0                | 0   | 1   | Clears the display and sets the address counter to DD RAM address 0.                                                                                                                                                               | 1.64ms                                         |

| Cursor Home            | 0                                                      | 0                                                             | 0                                           | 0                 | 0   | 0                                                                                                                                                                                      | 0                                                                                                                                                                                            | 0                | 1   | ×   | Sets the address counter to DD RAM address 0. Returns a shifted display to the original position. Does not alter the DD RAM data                                                                                                   | 1.64ms                                         |

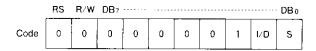

| Set Entry Mode         | 0                                                      | 0                                                             | 0                                           | 0                 | 0   | 0                                                                                                                                                                                      | 0                                                                                                                                                                                            | 1                | I/D | s   | Sets cursor movement and display shift following a data read or write. When I/D is 1, the cursor increments, and when 0, decrements. When S is 1, the display also shifts.                                                         | 40µs                                           |

| Display ON/OFF         | 0                                                      | 0 0 0 0 0 0 1 D C B cursor is ON, and w                       |                                             |                   |     | When D is 1, the display is ON, and when 0, OFF. When C is 1, the cursor is ON, and when 0, OFF. When B is 1, blinking of the character at the cursor position is ON, and when 0, OFF. | 40μs                                                                                                                                                                                         |                  |     |     |                                                                                                                                                                                                                                    |                                                |

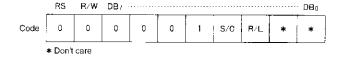

| Cursor/Display Shift   | 0                                                      | Moves the cursor or the display without altering the DD RAM d |                                             |                   |     |                                                                                                                                                                                        | Moves the cursor or the display without altering the DD FIAM data. When S/C is 1, the display shifts, and when 0, the cursor moves. When R/L is 1, the direction is right, and when 0, left. | 40μs             |     |     |                                                                                                                                                                                                                                    |                                                |

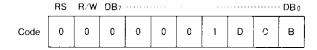

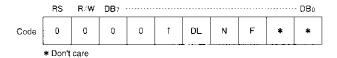

| Set Function           | 0                                                      | 0                                                             | 0                                           | 0                 | 1   | DL                                                                                                                                                                                     | N                                                                                                                                                                                            | F                | ×   | ×   | When DL is 1, the interface size is eight bits, and when 0, four bits. When N is 1, the display size is two lines, and when 0, a single line. When F is 1, the font size is $5 \times 10$ pixels, and when $0, 5 \times 7$ pixels. | 40μs                                           |

| Set CG FIAM Address    | 0                                                      | 0                                                             | 0                                           | 1                 |     |                                                                                                                                                                                        | CG RAN                                                                                                                                                                                       | address          |     |     | Sets the CG RAM address. Data read and writes after this instruction are to and from CG RAM.                                                                                                                                       | 40µs                                           |

| Set DD FIAM Address    | 0                                                      | 0                                                             | 1                                           |                   |     | DD                                                                                                                                                                                     | RAM add                                                                                                                                                                                      | lress            |     |     | Sets the DD FAM address. Data read and writes after this instruction are to and from DD FAM.                                                                                                                                       | 40µs                                           |

| Busy Flag/Address Read | 0                                                      | 1                                                             | BF                                          |                   |     | Adı                                                                                                                                                                                    | dress cou                                                                                                                                                                                    | nter             |     |     | Used during execution of other instructions, outputs the busy flag state and the address counter value. The address counter is used for both DD RAM and CG RAM.                                                                    | 0µs                                            |

| Data Write             | 1                                                      | 0                                                             |                                             | •                 |     | Write                                                                                                                                                                                  | e data                                                                                                                                                                                       |                  |     |     | Writes data to DD RAM or CG RAM.                                                                                                                                                                                                   | 40µs (t <sub>ADD</sub> = 6µs)                  |

| Data Read              | 1                                                      | 1                                                             |                                             |                   |     | Read                                                                                                                                                                                   | d data                                                                                                                                                                                       |                  |     |     | Reads data from DD RAM or CG RAM.                                                                                                                                                                                                  | 40µs (t <sub>ADD</sub> = 6µs)                  |

|                        | S =1:<br>S/C=1:<br>F/L =1:<br>DL =1:<br>N =1:<br>F =1: | display s<br>right shi<br>8-bit<br>two rows                   | anied by o<br>shift<br>it<br>s<br>pixel ch: | I/D =0: decrement |     |                                                                                                                                                                                        |                                                                                                                                                                                              | hift<br>ixel cha |     |     | DD RAM : display data RAM CG RAM : character generator RAM ACG : CG RAM address ADD : DD RAM address corresponding to cursor address AC : address counter used for both DD RAM and CG RAM                                          |                                                |

Note: \*1. The execution time depends on the operating frequency. For example, if  $f_{CP}$  or  $f_{OSC} = 270 \text{kHz}$ , the execution time is  $40 \mu \text{s} \times 250/270 = 37 \mu \text{s}$ .

#### **Display Clear**

Fills the DD RAM with space characters  $(20_{\rm H})$ , returns the display to the unshifted position and sets the address counter to zero, returning the cursor to the top-left display position. The address counter increment/decrement mode is set to increment. The character blinking and display shift modes are not affected.

Note that if a custom character generator ROM is used, the space character must correspond to the  $20_{\rm H}$  character code for the display to be cleared correctly.

#### **Cursor Home**

Returns the display to the unshifted position and sets the address counter to zero, returning the cursor to the top-left display position. Does not alter the DD RAM data.

#### **Set Entry Mode**

Sets the cursor auto-increment direction and the display shift mode and direction. When I/D is 1, the address counter increments when data is read from or written to either the DD RAM or the CG RAM, thereby shifting the cursor right one character position. When I/D is 0, the address counter decrements, shifting the cursor left.

When S is 1, display shift is ON, and the display also shifts one character position to the right or left when data is written to the DD RAM so that the cursor position relative to the display is unchanged. No display shift occurs when data is read from the DD RAM or when data is read from or written to the CG RAM, although the address counter increments or decrements for all read and write operations. When S is 0, display shift is OFF.

#### Display ON/OFF

Sets the display, the cursor and character blinking ON or OFF

When D is 1, the display is ON, and when 0, OFF. Setting the display ON or OFF does not alter the address counter or the DD RAM data.

When C is 1, the cursor is ON, and when 0, OFF. Setting the cursor ON or OFF does not affect the cursor autoincrement and display shift modes.

When B is 1, the cursor and the character at the cursor position blink, alternating between black (all pixels ON) and the displayed character as shown in the following figure. When  $f_{CP}$  or  $f_{OSC} = 250 \mathrm{kHz}$ , the blink interval is 409.6ms, and when  $f_{CP}$  or  $f_{OSC} = 270 \mathrm{kHz}$ , 379.2ms.

### **Cursor/Display Shift**

Shifts the cursor or the display either left or right as shown in the following table. A DD RAM write is not required.

When shifting a 2-line display, both rows shift simultaneously, but characters do not move from one row to another. Each time the display shifts, the characters in each row only move within the row.

| S/C | R/L | Description                                                                                           |

|-----|-----|-------------------------------------------------------------------------------------------------------|

| 0   | 0   | Decrements the address counter and shifts the cursor left.                                            |

| 0   | 1   | Increments the address counter and shifts the cursor right.                                           |

| 1   | 0   | Shifts the display left. The address counter does not change, and the cursor moves with the display.  |

| 1   | 1   | Shifts the display right. The address counter does not change, and the cursor moves with the display. |

#### **Set Function**

Sets the microcontroller interface bus size and the display mode. When DL is 1, the interface size is eight bits, and when 0, four bits. When the interface size is four bits, two reads or writes of the high-order bits of the data bus, DB4 toB7, are required.

N and F set the display mode as shown in the following table. N sets the number of lines in the display, and F, the font size. Note that a 2-line display cannot use the  $5\times 10$ -pixel font size.

| N | F | Display lines | Font size (pixels) | Duty |

|---|---|---------------|--------------------|------|

| 0 | 0 | 1             | 5×7                | 1/8  |

| 0 | 1 | 1             | 5×10               | 1/11 |

| 1 | × | 2             | 5×7                | 1/16 |

Note that the font size and number of lines cannot be changed once any other instruction is executed following the Set Function instruction.

#### Set CG RAM Address

Loads the 6-bit character generator RAM address into the address counter. Data reads and writes after this instruction is executed are to and from the CG RAM.

#### Set DD RAM Address

Loads the 7-bit display data RAM address into the address counter. Data reads and writes after this instruction is executed are to and from the DD RAM.

#### **Busy Flag/Address Read**

Outputs the busy flag state and the address counter value. The busy flag is used to check if the previous instruction has finished executing. When BF is 1, the previous instruc-

tion is executing, and when 0, the instruction has completed. The next instruction cannot be received until BF is 0. The microcontroller should, therefore, confirm that BF is 0 before writing the next instruction.

The address counter is used for both the DD RAM and the CG RAM. The address output on DB0 to DB7 is the counter value before the currently executing instruction began.

#### **Data Write**

Writes the 8-bit data on DB0 to DB7 to either the DD RAM or the CG RAM, according to whether a Set DD RAM Address or a Set CG RAM Address instruction was executed previously. After writing, the address counter automatically increments or decrements according to the entry mode setting, and the display can also shift.

#### **Data Read**

Outputs 8-bit data on DB0 to DB7 from either the DD RAM or the CG RAM, according to whether a Set DD RAM Address or a Set CG RAM Address instruction was executed previously. After the data is read, the address counter automatically increments or decrements according to the entry mode setting, but the display does not shift.

Note that a Set DD RAM Address or Set CG RAM Address instruction should be executed before executing this command. If a Data Read instruction is executed without first executing an address set instruction, the output data will not be valid. If the instruction is repeated, however, the output data will be valid data from the next address. Subsequent Data Read instructions will output valid data.

The output data will not be valid if this command is executed following a Data Write command, even though the address counter has just incremented or decremented.

A Cursor/Display Shift instruction has the same effect as a Set DD RAM Address instruction. If a Cursor/Display Shift instruction moves the cursor, an address set instruction does not have to be executed before the Data Read instruction, and the data is read from the DD RAM.

#### Microcontroller Interface

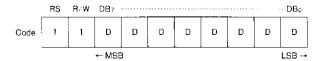

#### 8-bit interface

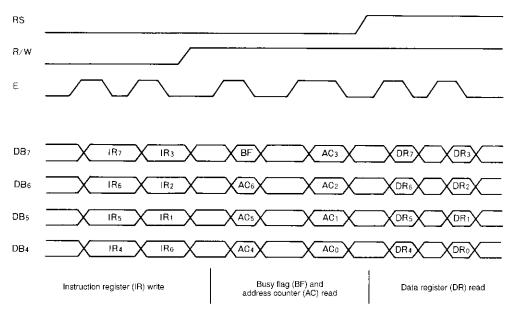

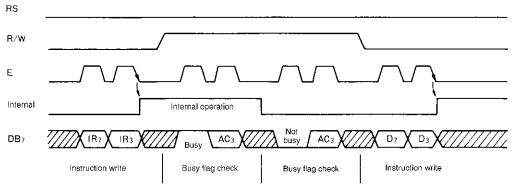

DB0 to DB7 are used for the 8-bit data bus. The timing sequence for instruction write, instruction execution, and busy flag checking is shown in the following figure.

#### 4-bit interface

The timing sequence for instruction write, instruction execution and busy flag checking is shown in the following figure. The busy flag is checked after transferring two 4-bit sets of data. The busy flag and address counter value are

output as two 4-bit words. Checking the busy flag, therefore, requires two read cycles so the low-order four bits of the address counter value are flushed from the data buffer.

Note. IR7 and IR3 are the 7th and 3rd bit, respectively, of the instruction. AC3 is the 3rd bit of the address counter.

## **LCD** Interface

The number of common signals and the duty cycle for each combination of font and display lines are shown in the following table. One common signal is required for each pixel-row in the character, and an additional common signal is required for the cursor row beneath the character.

| Display lines | Font size                | Common<br>signals | Duty |

|---------------|--------------------------|-------------------|------|

| 1             | 5 × 7-pixel +<br>cursor  | 8                 | 1/8  |

| 1             | 5 × 10-pixel +<br>cursor | 11                | 1/11 |

| 2             | 5 × 7-pixel +<br>cursor  | 16                | 1/16 |

# **Sample Application Circuits**

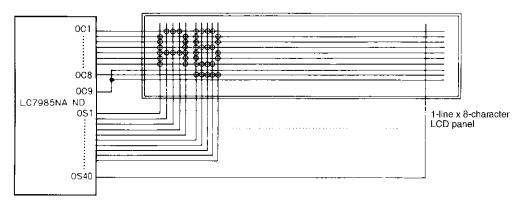

# 1-line $\times$ 8-character, 1/4-bias and 1/8-duty Display with 5 $\times$ 7-pixel Font

1-line  $\times$  8-character, 1/4-bias and 1/11-duty Display with 5  $\times$  10-pixel Font

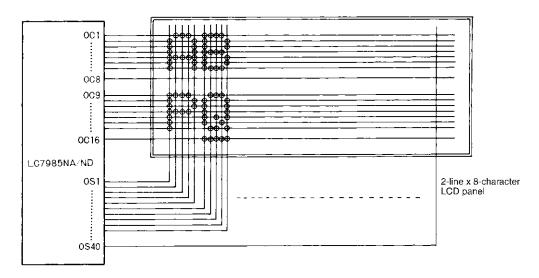

2-line  $\times$  8-character, 1/5-bias and 1/16-duty Display with 5  $\times$  7-pixel Font

# **Connecting Unused Display Rows**

Connecting unused LCD panel common pins to an unused LC7985 common output pin as shown in the following figure prevents crosstalk from the active drive signals affecting the display.

### 1-line $\times$ 8-character, 1/4-bias and 1/8-duty Display with 5 $\times$ 7 pixel Font

## **Alternative Display Connections**

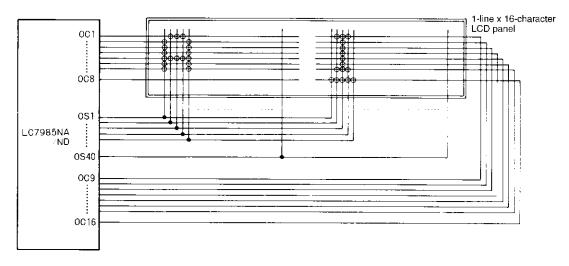

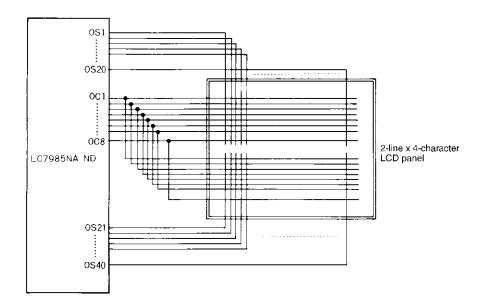

The LC7985 to LCD panel connections can be varied to match the LCD panel matrix as shown in the following sections.

## 1-line $\times$ 16-character, 1/8-bias and 1/16-duty Display with 5 $\times$ 7 pixel Font

2-line  $\times$  4-character, 1/4-bias and 1/8-duty Display with 5  $\times$  7 pixel Font

# LCD driver power supply

The reference voltage levels required to generate the LCD drive waveforms are shown in the following table.

Voltages  $V_1$  to  $V_5$  are input on pins V1 to V5, respectively. The voltages can be produced using a voltage-divider resistor network. The voltages required depend upon the duty cycle.  $V_{\rm LCD}$  is the LCD driver peak voltage, where  $V_{\rm LCD} = V_{\rm DD} - V_5.$

| Voltage        | 1/4 bias and 1/8 or 1/11 duty          | 1/5 bias and 1/16 duty               |

|----------------|----------------------------------------|--------------------------------------|

| V <sub>1</sub> | V <sub>DD</sub> - 0.25V <sub>LCD</sub> | $V_{\text{DD}} - 0.2 V_{\text{LCD}}$ |

| V <sub>2</sub> | $V_{\text{DD}} - 0.5 V_{\text{LCD}}$   | $V_{\text{DD}} - 0.4 V_{\text{LCD}}$ |

| V <sub>3</sub> | $V_{\text{DD}} - 0.5 V_{\text{LCD}}$   | $V_{\text{DD}} - 0.6V_{\text{LCD}}$  |

| $V_4$          | $V_{\text{DD}} - 0.75 V_{\text{LCD}}$  | $V_{\text{DD}} - 0.8 V_{\text{LCD}}$ |

| V <sub>5</sub> | $V_{DD} - V_{LCD}$                     | $V_{DD} - V_{LCD}$                   |

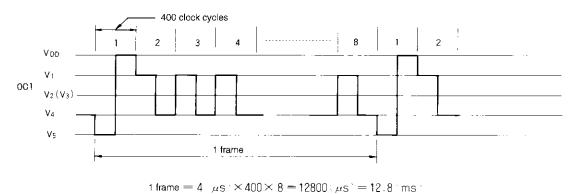

## 1/8 duty LCD drive

Frame frequency =

$$\frac{1}{12.8}$$

= 78.1 · Hz °

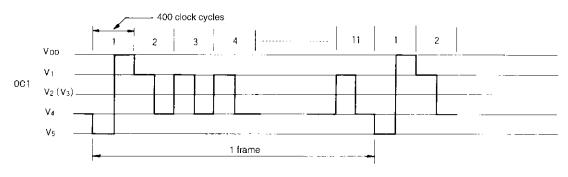

# 1/11 duty LCD drive

1 frame = 4

$$^{\prime}\mu s$$

:  $\times 400 \times 11 = 17600 (\mu s) = 17.6 \, ms$

Frame frequency =  $\frac{1}{17.6 \, (ms)} = 56.8 \, (Hz)$

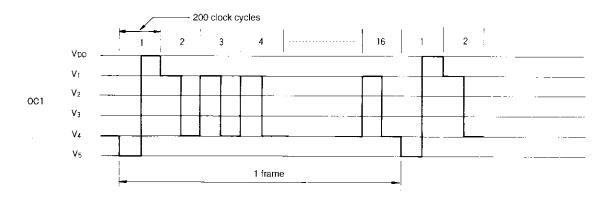

# 1/16 duty LCD drive

1 frame = 4  $^{\circ}\mu$ s .  $\times$  200  $\times$  16 = 12800  $^{\circ}\mu$ s . = 12.8  $^{\circ}$ ms . Frame frequency =  $\frac{1}{12.8 \text{ ms}}$  = 78.1 Hz .

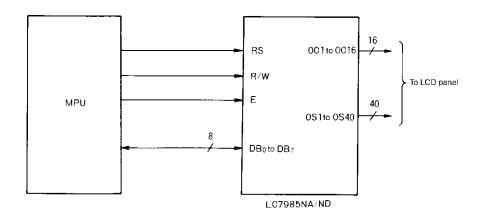

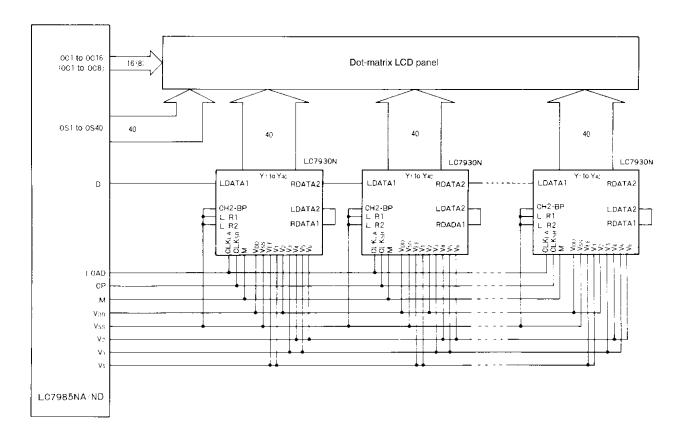

## LC7930N Interface

When using a single-line display, up to nine LC7930Ns, and when using a two-line display, up to four LC7930Ns can interface to the LC7985 using the circuit shown in the following figure. The LC7985 LOAD, CP, M and D outputs connect directly to the LC7930Ns. Take care that the V1 to V5 voltage reference outputs are connected correctly to the LC7930Ns.

## **Examples**

# 8-bit interface size, 1-line $\times$ 8-character display and internal reset circuit

The programming example is shown in the following table. This example assumes that the internal reset circuit initializes the LC7985.

The Set Function instruction that is executed before the display is turned ON determines the operation of the device.

Since the DD RAM stores 80 characters, the display shift function can be used as shown in the example. Note that display shifts only change the display position and do not alter the DD RAM. Using the Cursor Home instruction, therefore, returns the display to its original position.

| Instruction          |    |     |     |     | Co  | xde |     |     |     | Dianter | Description |                                                                                                                                                            |

|----------------------|----|-----|-----|-----|-----|-----|-----|-----|-----|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| instruction          | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0     | Display     | Description                                                                                                                                                |

| Power-ON             |    |     |     |     |     |     |     |     |     |         |             | The internal reset circuit initializes the LC7985. The display is OFF.                                                                                     |

| Set Function         | 0  | 0   | 0   | 0   | 1   | 1   | 0   | 0   | ×   | ×       |             | Sets 8-bit interface size, 1-line display size and 5 × 7-pixel character font. The number of display lines and the character font cannot be changed later. |

| Display ON/OFF       | 0  | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0       | _           | Turns the display ON and enables the cursor.<br>The display is blank.                                                                                      |

| Set Entry Mode       | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0       |             | Sets address auto-increment and automatic cursor right shift on writing to DD RAM or CG RAM. The display is not shifted.                                   |

| Data Write           | 1  | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 0   | 0       | L_          | Writes "L' to DD RAM, since DD RAM was selected when the LC7995 was initialized at power-ON. The cursor position increments and the cursor moves right.    |

| Data Write           | 1  | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 1   | 1       | LC_         | Writes 'C'.                                                                                                                                                |

| Data Write           |    |     |     |     |     | 1   |     |     |     |         | <b>↓</b>    | <b>†</b>                                                                                                                                                   |

| Data Write           | 1  | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 0   | 1       | LC7985_     | Writes °5.                                                                                                                                                 |

| Set Entry Mode       | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1       | LC7985_     | Sets display shift on writing to DD RAM.                                                                                                                   |

| Data Write           | 1  | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0       | C7985       | Writes a space ' '.                                                                                                                                        |

| Data Write           | 1  | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 0   | 0       | 7985 L_     | Writes T.                                                                                                                                                  |

| Data Write           |    |     |     |     |     |     |     |     |     |         | <b>↓</b>    | <b>↓</b>                                                                                                                                                   |

| Data Write           | 1  | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 1   | 1       | LCD KO_     | Writes °C'.                                                                                                                                                |

| Cursor/Display Shift | 0  | 0   | 0   | 0   | 0   | 1   | 0   | 0   | ×   | ×       | LCD KO      | Shifts the cursor left.                                                                                                                                    |

| Cursor/Display Shift | 0  | 0   | 0   | 0   | 0   | 1   | 0   | 0   | ×   | ×       | LCD KO      | Shifts the cursor left.                                                                                                                                    |

| Data Write           | 1  | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 1   | 1       | CD CO       | Writes 'C', the correct character. The display scrolls left.                                                                                               |

| Cursor/Display Shift | 0  | 0   | 0   | 0   | 0   | 1   | 1   | 1   | ×   | ×       | LCD CO      | Shifts both the display and the cursor right.                                                                                                              |

| Cursor/Display Shift | 0  | 0   | 0   | 0   | 0   | 1   | 0   | 1   | ×   | ×       | rcd co_     | Shifts the cursor right.                                                                                                                                   |

| Data Write           | 1  | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 1   | 0       | CD CON_     | Writes 'N.'                                                                                                                                                |