**MOSEL VITELIC**

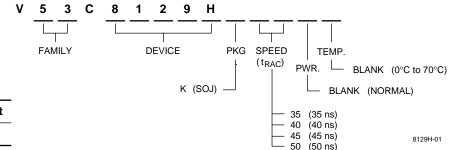

# V53C8129H ULTRA-HIGH PERFORMANCE, 128K X 8 EDO PAGE MODE CMOS DYNAMIC RAM

**PRELIMINARY**

| HIGH PERFORMANCE                                     | 35    | 40    | 45    | 50    |

|------------------------------------------------------|-------|-------|-------|-------|

| Max. RAS Access Time, (t <sub>RAC</sub> )            | 35 ns | 40 ns | 45 ns | 50 ns |

| Max. Column Address Access Time, (t <sub>CAA</sub> ) | 18 ns | 20 ns | 22 ns | 24 ns |

| Min. Fast Page Mode With EDO Cycle Time, $(t_{PC})$  | 14 ns | 15 ns | 17 ns | 19 ns |

| Min. Read/Write Cycle Time, (t <sub>RC</sub> )       | 70 ns | 75 ns | 80 ns | 90 ns |

#### Features

- 128K x 8-bit organization

- RAS access time: 35, 40, 45, 50 ns

- EDO Page Mode supports sustained I/O data rates up to 71.5 MHz

- Low power dissipation

- V53C8129H-50

- Operating Current: 135 mA max

- TTL Standby Current: 2.0 mA max

- Low CMOS Standby Current: 1.0 mA max

- Read-Modify-Write, RAS-Only Refresh, CAS-Before-RAS Refresh capability

- Refresh Interval: 512 cycles/8 ms

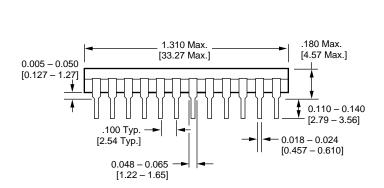

- Available in 26/24 pin 300 mil SOJ package

#### Description

The V53C8129H is a high speed 131,072 x 8 bit CMOS dynamic random access memory. The V53C8129H offers a combination of features: EDO Page Mode for high data bandwidth, fast usable speed, CMOS standby current.

All inputs and outputs are TTL compatible. Input and output capacitances are significantly lowered to allow increased system performance. Page Mode with extended data out operation allows random access of up to 256 columns (x8) bits within a row with cycle times as short as 14 ns. Because of static circuitry, the CAS clock is not in the critical timing path. The flow-through column address latches allow address pipelining while relaxing many critical system timing requirements for fast usable speed. These features make the V53C8129H ideally suited for graphics, digital signal processing and high performance peripherals.

#### Device Usage Chart

| Operating            | Package Outline |    | Access | Γime (ns) |    | Power | Townserves          |  |  |

|----------------------|-----------------|----|--------|-----------|----|-------|---------------------|--|--|

| Temperature<br>Range | К               | 35 | 40     | 45        | 50 | Std.  | Temperature<br>Mark |  |  |

| 0°C to 70 °C         | •               | •  | •      | •         | •  | •     | Blank               |  |  |

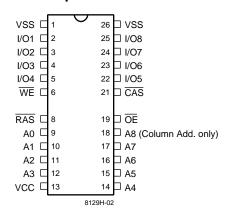

## 26/24 Lead SOJ PIN CONFIGURATION Top View

#### Pin Names

| A <sub>0</sub> -A <sub>8</sub>     | Address Inputs (A <sub>8</sub> : Column Address only) |

|------------------------------------|-------------------------------------------------------|

| RAS                                | Row Address Strobe                                    |

| CAS                                | Column Address Strobe                                 |

| WE                                 | Write Enable                                          |

| OE                                 | Output Enable                                         |

| I/O <sub>1</sub> –I/O <sub>8</sub> | Data Input, Output                                    |

| V <sub>CC</sub>                    | +5V Supply                                            |

| V <sub>SS</sub>                    | 0V Supply                                             |

#### Absolute Maximum Ratings\*

\*Note: Operation above Absolute Maximum Ratings can adversely affect device reliability.

#### Capacitance\*

$T_A = 25^{\circ}C$ ,  $V_{CC} = 5~V \pm 10\%$ ,  $V_{SS} = 0~V$

| Symbol           | Parameter         | Тур. | Max. | Unit |

|------------------|-------------------|------|------|------|

| C <sub>IN1</sub> | Address Input     | 3    | 4    | pF   |

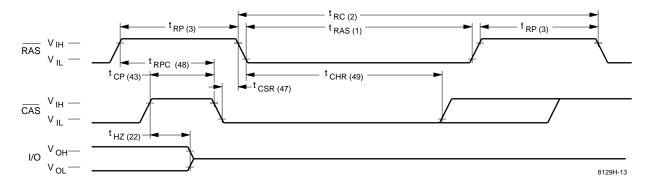

| C <sub>IN2</sub> | RAS, CAS, WE, OE  | 4    | 5    | pF   |

| C <sub>OUT</sub> | Data Input/Output | 5    | 7    | pF   |

<sup>\*</sup> Note: Capacitance is sampled and not 100% tested

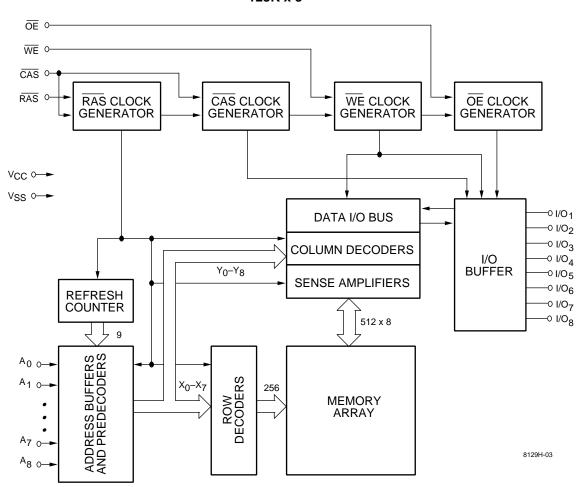

## **Block Diagram**

#### 128K x 8

**DC and Operating Characteristics** (1-2) T<sub>A</sub> = 0°C to 70°C, V<sub>CC</sub> = 5 V  $\pm$  10%, V<sub>SS</sub> = 0 V, unless otherwise specified.

|                  |                                                            | A              | V53C8129H |      | Н                   |      |                                                                                                                                                                                  |       |

|------------------|------------------------------------------------------------|----------------|-----------|------|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Symbol           | Parameter                                                  | Access<br>Time | Min.      | Тур. | Max                 | Unit | Test Conditions                                                                                                                                                                  | Notes |

| ILI              | Input Leakage Current (any input pin)                      |                | -10       |      | 10                  | μА   | $V_{SS} \le V_{IN} \le V_{CC}$                                                                                                                                                   |       |

| I <sub>LO</sub>  | Output Leakage Current (for High-Z State)                  |                | -10       |      | 10                  | μА   | $V_{SS} \le V_{OUT} \le V_{CC}$<br>RAS, CAS at $V_{IH}$                                                                                                                          |       |

| I <sub>CC1</sub> | V <sub>CC</sub> Supply Current,                            | 35             |           |      | 160                 | mA   | $t_{RC} = t_{RC} \text{ (min.)}$                                                                                                                                                 | 1, 2  |

|                  | Operating                                                  | 40             |           |      | 150                 |      |                                                                                                                                                                                  |       |

|                  |                                                            | 45             |           |      | 145                 |      |                                                                                                                                                                                  |       |

|                  |                                                            | 50             |           |      | 135                 |      |                                                                                                                                                                                  |       |

| I <sub>CC2</sub> | V <sub>CC</sub> Supply Current,<br>TTL Standby             |                |           |      | 4                   | mA   | RAS, CAS at V <sub>IH</sub> other inputs ≥ V <sub>SS</sub>                                                                                                                       |       |

| I <sub>CC3</sub> | V <sub>CC</sub> Supply Current,                            | 35             |           |      | 160                 | mA   | $t_{RC} = t_{RC}$ (min.)                                                                                                                                                         | 2     |

|                  | RAS-Only Refresh                                           | 40             |           |      | 150                 |      |                                                                                                                                                                                  |       |

|                  |                                                            | 45             |           |      | 145                 |      |                                                                                                                                                                                  |       |

|                  |                                                            | 50             |           |      | 135                 |      |                                                                                                                                                                                  |       |

| I <sub>CC4</sub> | V <sub>CC</sub> Supply Current,                            | 35             |           |      | 95                  | mA   | Minimum cycle                                                                                                                                                                    | 1, 2  |

|                  | EDO Page Mode Operation                                    | 40             |           |      | 90                  |      |                                                                                                                                                                                  |       |

|                  |                                                            | 45             |           |      | 85                  |      |                                                                                                                                                                                  |       |

|                  |                                                            | 50             |           |      | 80                  |      |                                                                                                                                                                                  |       |

| I <sub>CC5</sub> | V <sub>CC</sub> Supply Current,<br>Standby, Output Enabled |                |           |      | 2                   | mA   | $\overline{RAS} = V_{IH}, \overline{CAS} = V_{IL}$<br>other inputs $\geq V_{SS}$                                                                                                 | 1     |

| I <sub>CC6</sub> | V <sub>CC</sub> Supply Current,<br>CMOS Standby            |                |           |      | 1                   | mA   | $\label{eq:rate} \begin{split} \overline{RAS} &\geq V_{CC} - 0.2 \text{ V,} \\ \overline{CAS} &\geq V_{CC} - 0.2 \text{ V,} \\ \text{All other inputs} &\geq V_{SS} \end{split}$ |       |

| V <sub>IL</sub>  | Input Low Voltage                                          |                | -1        |      | 0.8                 | V    |                                                                                                                                                                                  | 3     |

| V <sub>IH</sub>  | Input High Voltage                                         |                | 2.4       |      | V <sub>CC</sub> + 1 | V    |                                                                                                                                                                                  | 3     |

| V <sub>OL</sub>  | Output Low Voltage                                         |                |           |      | 0.4                 | V    | I <sub>OL</sub> = 4.2 mA                                                                                                                                                         |       |

| V <sub>OH</sub>  | Output High Voltage                                        |                | 2.4       |      |                     | V    | I <sub>OH</sub> = -5 mA                                                                                                                                                          |       |

V53C8129H **MOSEL VITELIC**

$\pmb{AC\ Characteristics}$   $T_A=0^{\circ}C$  to 70°C,  $V_{CC}=5$  V  $\pm 10\%,\,V_{SS}=0V$  unless otherwise noted AC Test conditions, input pulse levels 0 to 3V

|    | JEDEC                  |                      |                                                              | 35   |      | 40   |      | 45   |      | 50   |      |      |          |

|----|------------------------|----------------------|--------------------------------------------------------------|------|------|------|------|------|------|------|------|------|----------|

| #  | Symbol                 | Symbol               | Parameter                                                    | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Unit | Notes    |

| 1  | t <sub>RL1RH1</sub>    | t <sub>RAS</sub>     | RAS Pulse Width                                              | 35   | 75K  | 40   | 75K  | 45   | 75K  | 50   | 75K  | ns   |          |

| 2  | t <sub>RL2RL2</sub>    | t <sub>RC</sub>      | Read or Write Cycle Time                                     | 70   |      | 75   |      | 80   |      | 90   |      | ns   |          |

| 3  | t <sub>RH2RL2</sub>    | t <sub>RP</sub>      | RAS Precharge Time                                           | 25   |      | 25   |      | 25   |      | 30   |      | ns   |          |

| 4  | t <sub>RL1CH1</sub>    | t <sub>CSH</sub>     | CAS Hold Time                                                | 35   |      | 40   |      | 45   |      | 50   |      | ns   |          |

| 5  | t <sub>CL1CH1</sub>    | t <sub>CAS</sub>     | CAS Pulse Width                                              | 7    |      | 8    |      | 9    |      | 9    |      | ns   |          |

| 6  | t <sub>RL1CL1</sub>    | t <sub>RCD</sub>     | RAS to CAS Delay                                             | 16   | 23   | 17   | 28   | 18   | 32   | 19   | 36   | ns   |          |

| 7  | t <sub>WH2CL2</sub>    | t <sub>RCS</sub>     | Read Command Setup Time                                      | 0    |      | 0    |      | 0    |      | 0    |      | ns   | 4        |

| 8  | t <sub>AVRL2</sub>     | t <sub>ASR</sub>     | Row Address Setup Time                                       | 0    |      | 0    |      | 0    |      | 0    |      | ns   |          |

| 9  | t <sub>RL1AX</sub>     | t <sub>RAH</sub>     | Row Address Hold Time                                        | 6    |      | 7    |      | 8    |      | 9    |      | ns   |          |

| 10 | t <sub>AVCL2</sub>     | t <sub>ASC</sub>     | Column Address Setup Time                                    | 0    |      | 0    |      | 0    |      | 0    |      | ns   |          |

| 11 | t <sub>CL1AX</sub>     | t <sub>CAH</sub>     | Column Address Hold Time                                     | 4    |      | 5    |      | 6    |      | 7    |      | ns   |          |

| 12 | t <sub>CL1RH1(R)</sub> | t <sub>RSH (R)</sub> | RAS Hold Time (Read Cycle)                                   | 14   |      | 14   |      | 15   |      | 15   |      | ns   |          |

| 13 | t <sub>CH2RL2</sub>    | t <sub>CRP</sub>     | CAS to RAS Precharge Time                                    | 5    |      | 5    |      | 5    |      | 5    |      | ns   |          |

| 14 | t <sub>CH2WX</sub>     | t <sub>RCH</sub>     | Read Command Hold Time Referenced to $\overline{\text{CAS}}$ | 0    |      | 0    |      | 0    |      | 0    |      | ns   | 5        |

| 15 | t <sub>RH2WX</sub>     | t <sub>RRH</sub>     | Read Command Hold Time Referenced to RAS                     | 0    |      | 0    |      | 0    |      | 0    |      | ns   | 5        |

| 16 | t <sub>OEL1RH2</sub>   | t <sub>ROH</sub>     | RAS Hold Time Referenced to OE                               | 8    |      | 9    |      | 10   |      | 10   |      | ns   |          |

| 17 | t <sub>GL1QV</sub>     | t <sub>OAC</sub>     | Access Time from OE                                          |      | 12   |      | 12   |      | 13   |      | 14   | ns   |          |

| 18 | t <sub>CL1QV</sub>     | t <sub>CAC</sub>     | Access Time from CAS (EDO)                                   |      | 12   |      | 12   |      | 13   |      | 14   | ns   | 6, 7     |

| 19 | t <sub>RL1QV</sub>     | t <sub>RAC</sub>     | Access Time from RAS                                         |      | 35   |      | 40   |      | 45   |      | 50   | ns   | 6, 8, 9  |

| 20 | t <sub>AVQV</sub>      | t <sub>CAA</sub>     | Access Time from Column Address                              |      | 18   |      | 20   |      | 22   |      | 24   | ns   | 6, 7, 10 |

| 21 | t <sub>CL1QX</sub>     | t <sub>LZ</sub>      | CAS to Low-Z Output                                          | 0    |      | 0    |      | 0    |      | 0    |      | ns   | 16       |

| 22 | t <sub>CH2QZ</sub>     | t <sub>HZ</sub>      | Output buffer turn-off delay time                            | 0    | 6    | 0    | 6    | 0    | 7    | 0    | 8    | ns   | 16       |

| 23 | t <sub>RL1AX</sub>     | t <sub>AR</sub>      | Column Address Hold Time from RAS                            | 28   |      | 30   |      | 35   |      | 40   |      | ns   |          |

| 24 | t <sub>RL1AV</sub>     | t <sub>RAD</sub>     | RAS to Column Address Delay Time                             | 11   | 17   | 12   | 20   | 13   | 23   | 14   | 26   | ns   | 11       |

| 25 | t <sub>CL1RH1(W)</sub> | t <sub>RSH (W)</sub> | RAS or CAS Hold Time in Write Cycle                          | 12   |      | 12   |      | 13   |      | 14   |      | ns   |          |

| 26 | t <sub>WL1CH1</sub>    | t <sub>CWL</sub>     | Write Command to CAS Lead Time                               | 12   |      | 12   |      | 13   |      | 14   |      | ns   |          |

| 27 | t <sub>WL1CL2</sub>    | t <sub>WCS</sub>     | Write Command Setup Time                                     | 0    |      | 0    |      | 0    |      | 0    |      | ns   | 12, 13   |

| 28 | t <sub>CL1WH1</sub>    | t <sub>WCH</sub>     | Write Command Hold Time                                      | 5    |      | 5    |      | 6    |      | 7    |      | ns   |          |

| 29 | t <sub>WL1WH1</sub>    | t <sub>WP</sub>      | Write Pulse Width                                            | 5    |      | 5    |      | 6    |      | 7    |      | ns   |          |

| 30 | t <sub>RL1WH1</sub>    | t <sub>WCR</sub>     | Write Command Hold Time from RAS                             | 28   |      | 30   |      | 35   |      | 40   |      | ns   |          |

| 31 | t <sub>WL1RH1</sub>    | t <sub>RWL</sub>     | Write Command to RAS Lead Time                               | 12   |      | 12   |      | 13   |      | 14   |      | ns   |          |

# AC Characteristics (Cont'd)

|    | JEDEC                        |                  |                                               | 35   |      | 4    | 0    | 4    | 5    | 5    | 0    |      |       |

|----|------------------------------|------------------|-----------------------------------------------|------|------|------|------|------|------|------|------|------|-------|

| #  | Symbol                       | Symbol           | Parameter                                     | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Unit | Notes |

| 32 | t <sub>DVWL2</sub>           | t <sub>DS</sub>  | Data in Setup Time                            | 0    |      | 0    |      | 0    |      | 0    |      | ns   | 14    |

| 33 | t <sub>WL1DX</sub>           | t <sub>DH</sub>  | Data in Hold Time                             | 4    |      | 5    |      | 6    |      | 7    |      | ns   | 14    |

| 34 | t <sub>WL1GL2</sub>          | t <sub>WOH</sub> | Write to OE Hold Time                         | 5    |      | 6    |      | 7    |      | 8    |      | ns   | 14    |

| 35 | t <sub>GH2DX</sub>           | t <sub>OED</sub> | OE to Data Delay Time                         | 5    |      | 6    |      | 7    |      | 8    |      | ns   | 14    |

| 36 | t <sub>RL2RL2</sub><br>(RMW) | t <sub>RWC</sub> | Read-Modify-Write Cycle Time                  | 105  |      | 110  |      | 115  |      | 130  |      | ns   |       |

| 37 | t <sub>RL1RH1</sub><br>(RMW) | t <sub>RRW</sub> | Read-Modify-Write Cycle RAS Pulse Width       | 70   |      | 75   |      | 80   |      | 87   |      | ns   |       |

| 38 | t <sub>CL1WL2</sub>          | t <sub>CWD</sub> | CAS to WE Delay                               | 28   |      | 30   |      | 32   |      | 34   |      | ns   | 12    |

| 39 | t <sub>RL1WL2</sub>          | t <sub>RWD</sub> | RAS to WE Delay in Read-Modify-Write Cycle    | 54   |      | 58   |      | 62   |      | 68   |      | ns   | 12    |

| 40 | t <sub>CL1CH1</sub>          | t <sub>CRW</sub> | CAS Pulse Width (RMW)                         | 46   |      | 48   |      | 50   |      | 52   |      | ns   |       |

| 41 | t <sub>AVWL2</sub>           | t <sub>AWD</sub> | Col. Address to WE Delay                      | 35   |      | 38   |      | 41   |      | 42   |      | ns   | 12    |

| 42 | t <sub>CL2CL2</sub>          | t <sub>PC</sub>  | EDO Page Mode Read or Write Cycle<br>Time     | 14   |      | 15   |      | 17   |      | 19   |      | ns   |       |

| 43 | t <sub>CH2CL2</sub>          | t <sub>CP</sub>  | CAS Precharge Time                            | 4    |      | 5    |      | 6    |      | 7    |      | ns   |       |

| 44 | t <sub>AVRH1</sub>           | t <sub>CAR</sub> | Column Address to RAS Setup Time              | 18   |      | 20   |      | 22   |      | 24   |      | ns   |       |

| 45 | t <sub>CH2QV</sub>           | t <sub>CAP</sub> | Access Time from Column Precharge             |      | 21   |      | 23   |      | 25   |      | 27   | ns   | 7     |

| 46 | t <sub>RL1DX</sub>           | t <sub>DHR</sub> | Data in Hold Time Referenced to RAS           | 28   |      | 30   |      | 35   |      | 40   |      | ns   |       |

| 47 | t <sub>CL1RL2</sub>          | t <sub>CSR</sub> | CAS Setup Time CAS-before-RAS Refresh         | 10   |      | 10   |      | 10   |      | 10   |      | ns   |       |

| 48 | t <sub>RH2CL2</sub>          | t <sub>RPC</sub> | RAS to CAS Precharge Time                     | 0    |      | 0    |      | 0    |      | 0    |      | ns   |       |

| 49 | t <sub>RL1CH1</sub>          | t <sub>CHR</sub> | CAS Hold Time CAS-before-RAS Refresh          | 8    |      | 8    |      | 10   |      | 12   |      | ns   |       |

| 50 | t <sub>CL2CL2</sub><br>(RMW) | t <sub>PCM</sub> | EDO Page Mode Read-Modify-Write<br>Cycle Time | 58   |      | 60   |      | 65   |      | 70   |      | ns   |       |

| 51 | t <sub>T</sub>               | t <sub>T</sub>   | Transition Time (Rise and Fall)               | 3    | 50   | 3    | 50   | 3    | 50   | 3    | 50   | ns   | 15    |

| 52 |                              | t <sub>REF</sub> | Refresh Interval (512 Cycles)                 |      | 8    |      | 8    |      | 8    |      | 8    | ms   |       |

| 53 |                              | t <sub>COH</sub> | Output Hold After CAS Low                     | 5    |      | 5    |      | 5    |      | 5    |      | ns   |       |

#### Notes:

I<sub>CC</sub> is dependent on output loading when the device output is selected. Specified I<sub>CC</sub> (max.) is measured with the output open.

- I<sub>CC</sub> is dependent upon the number of address transitions. Specified I<sub>DD</sub> (max.) is measured with a maximum of two transitions per address cycle in EDO Page Mode.

- Specified V<sub>IL</sub> (min.) is steady state operating. During transitions, V<sub>IL</sub> (min.) may undershoot to −1.0 V for a period not to exceed 20 ns. All AC parameters are measured with V<sub>IL</sub> (min.) ≥ V<sub>SS</sub> and V<sub>IH</sub> (max.) ≤ V<sub>DD</sub>.

- 4. t<sub>RCD</sub> (max.) is specified for reference only. Operation within t<sub>RCD</sub> (max.) limits insures that t<sub>RAC</sub> (max.) and t<sub>CAA</sub> (max.) can be met. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max.), the access time is controlled by t<sub>CAA</sub> and t<sub>CAC</sub>.

- 5. Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisified for a Read Cycle to occur.

- 6. Measured with a load equivalent to two TTL inputs and 50 pF.

- 7. Access time is determined by the longest of  $t_{CAA}$ ,  $t_{CAC}$  and  $t_{CAP}$ .

- Assumes that t<sub>RAD</sub> ≤ t<sub>RAD</sub> (max.). If t<sub>RAD</sub> is greater than t<sub>RAD</sub> (max.), t<sub>RAC</sub> will increase by the amount that t<sub>RAD</sub> exceeds t<sub>RAD</sub> (max.).

- 9. Assumes that  $t_{RCD} \le t_{RCD}$  (max.). If  $t_{RCD}$  is greater than  $t_{RCD}$  (max.),  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds  $t_{RCD}$  (max.).

- 10. Assumes that  $t_{RAD} \ge t_{RAD}$  (max.).

- 11. Operation within the t<sub>RAD</sub> (max.) limit ensures that t<sub>RAC</sub> (max.) can be met. t<sub>RAD</sub> (max.) is specified as a reference point only. If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub> (max.) limit, the access time is controlled by t<sub>CAA</sub> and t<sub>CAC</sub>.

- 12.  $t_{WCS}$ ,  $t_{RWD}$ ,  $t_{AWD}$  and  $t_{CWD}$  are not restrictive operating parameters.

- 13. t<sub>WCS</sub> (min.) must be satisfied in an Early Write Cycle.

- 14.  $t_{DS}$  and  $t_{DH}$  are referenced to the latter occurrence of  $\overline{CAS}$  or  $\overline{WE}$ .

- 15.  $t_T$  is measured between  $V_{IH}$  (min.) and  $V_{IL}$  (max.). AC-measurements assume  $t_T = 3$  ns.

- 16. Assumes a three-state test load (5 pF and a 380 Ohm Thevenin equivalent).

- 17. An initial 200 μs pause and 8 RAS-containing cycles are required when exiting an extended period of bias without clocks. An extended period of time without clocks is defined as one that exceeds the specified Refresh Interval.

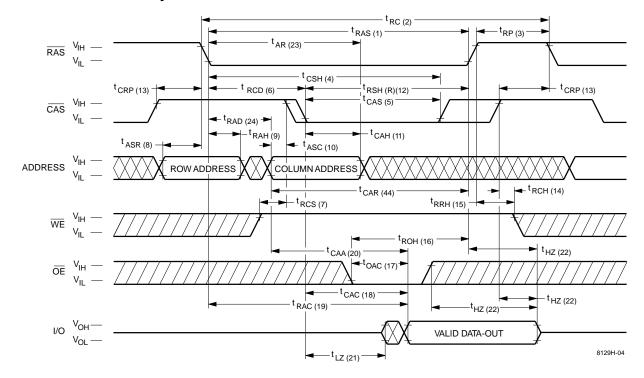

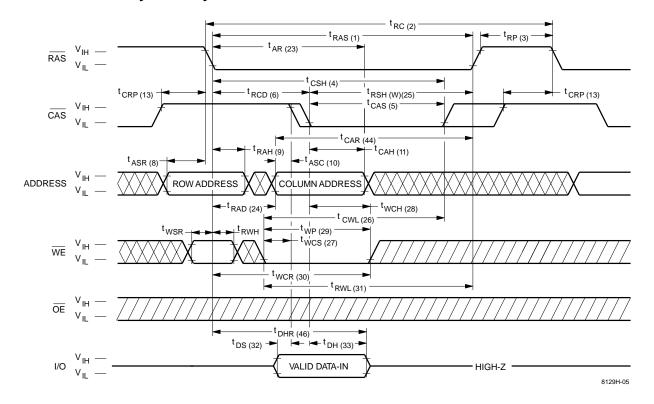

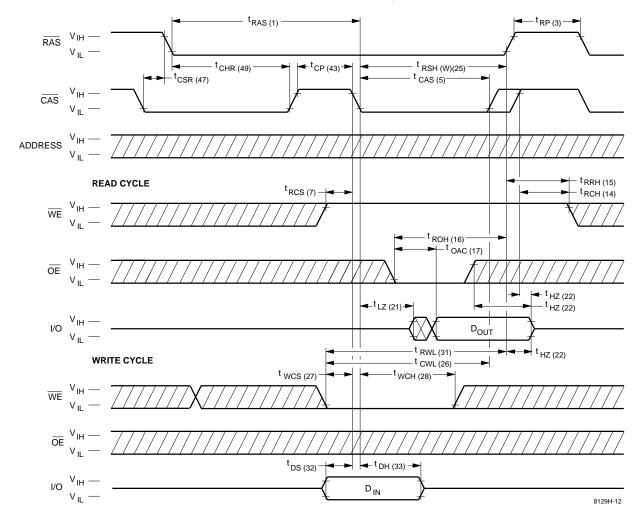

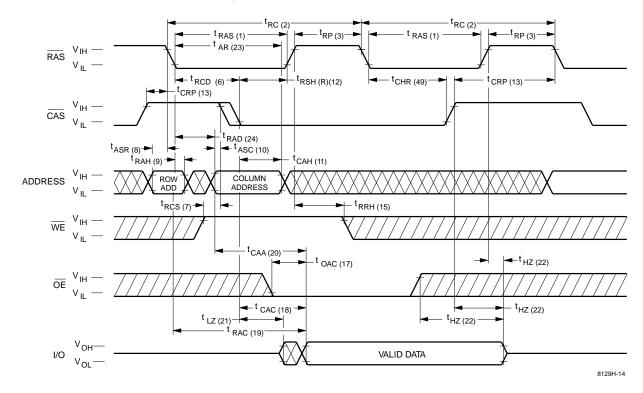

## Waveforms of Read Cycle

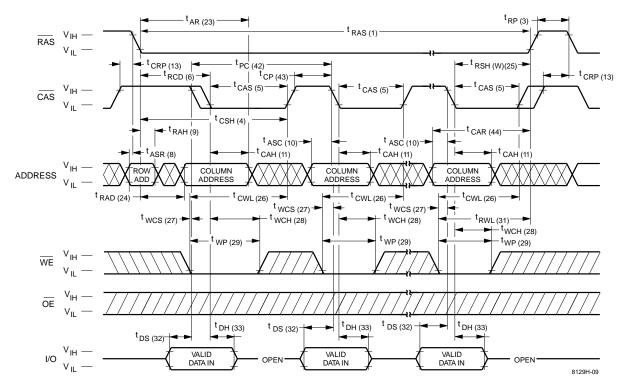

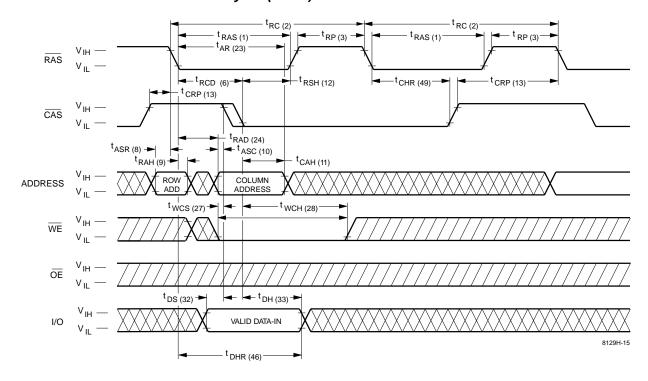

# Waveforms of Early Write Cycle

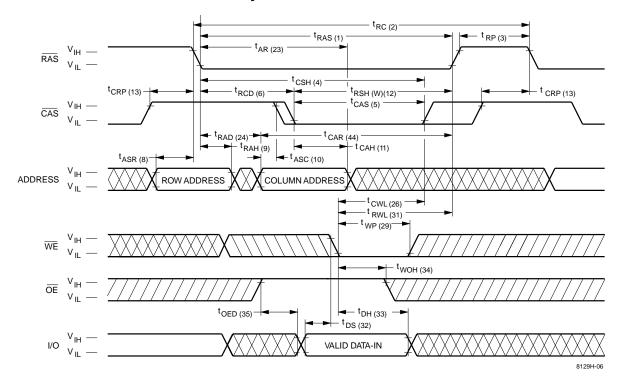

# Waveforms of OE-Controlled Write Cycle

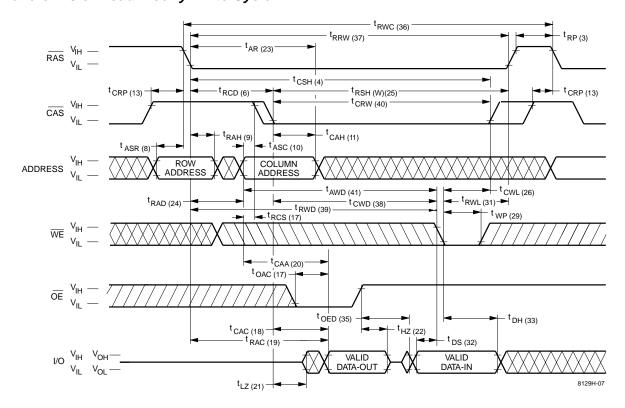

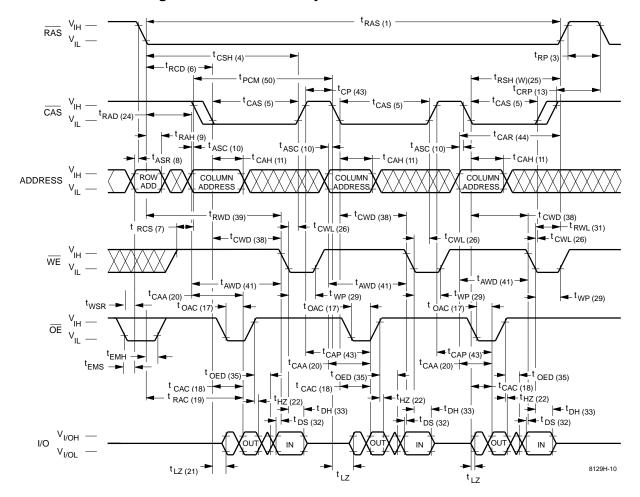

## Waveforms of Read-Modify-Write Cycle

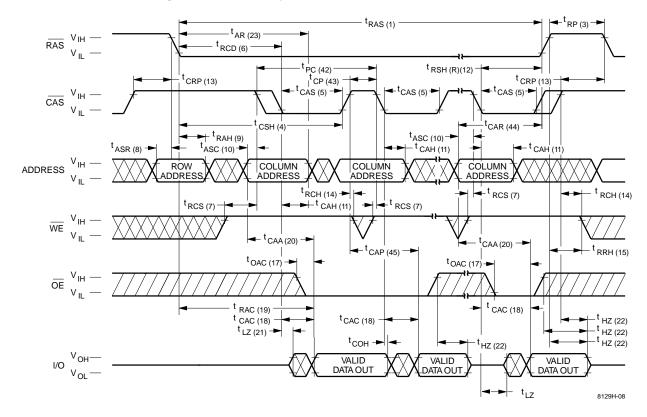

# Waveforms of EDO Page Mode Read Cycle

## Waveforms of EDO Page Mode Write Cycle

## Waveforms of EDO Page Mode Read-Write Cycle

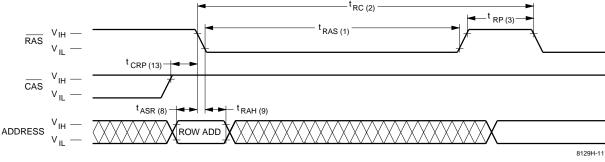

# Waveforms of RAS-Only Refresh Cycle

NOTE:  $\overline{WE}$ ,  $\overline{OE}$  = Don't care

# Waveforms of CAS-before-RAS Refresh Counter Test Cycle

# Waveforms of CAS-before-RAS Refresh Cycle

NOTE:  $\overline{WE}$ ,  $\overline{OE}$ ,  $A_0-A_8 = Don't care$

# Waveforms of Hidden Refresh Cycle (Read)

# Waveforms of Hidden Refresh Cycle (Write)

### Functional Description

The V53C8129H is a CMOS dynamic RAM optimized for high data bandwidth, low power applications. It is functionally similar to a traditional dynamic RAM. The V53C8129H reads and writes data by multiplexing an 17-bit address into a 8-bit row and an 9-bit column address. The row address is latched by the Row Address Strobe (RAS). The column address "flows through" an internal address buffer and is latched by the Column Address Strobe (CAS). Because access time is primarily dependent on a valid column address rather than the precise time that the CAS edge occurs, the delay time from RAS to CAS has little effect on the access time.

### Memory Cycle

A memory cycle is initiated by bringing  $\overline{RAS}$  low. Any memory cycle, once initiated, must not be ended or aborted before the minimum  $t_{RAS}$  time has expired. This ensures proper device operation and data integrity. A new cycle must not be initiated until the minimum precharge time  $t_{RP}/t_{CP}$  has elapsed.

### Read Cycle

A Read cycle is performed by holding the Write Enable ( $\overline{WE}$ ) signal High during a  $\overline{RAS}/\overline{CAS}$  operation. The column address must be held for a minimum specified by  $t_{AR}$ . Data Out becomes valid only when  $t_{OAC}$ ,  $t_{RAC}$ ,  $t_{CAA}$  and  $t_{CAC}$  are all satisifed. As a result, the access time is dependent on the timing relationships between these parameters. For example, the access time is limited by  $t_{CAA}$  when  $t_{RAC}$ ,  $t_{CAC}$  and  $t_{OAC}$  are all satisfied.

#### Write Cycle

A Write Cycle is performed by taking  $\overline{\text{WE}}$  and  $\overline{\text{CAS}}$  low during a  $\overline{\text{RAS}}$  operation. The column address is latched by  $\overline{\text{CAS}}$ . The Write Cycle can be  $\overline{\text{WE}}$  controlled or  $\overline{\text{CAS}}$  controlled depending on whether  $\overline{\text{WE}}$  or  $\overline{\text{CAS}}$  falls later. Consequently, the input data must be valid at or before the falling edge of  $\overline{\text{WE}}$  or  $\overline{\text{CAS}}$ , whichever occurs last. In the  $\overline{\text{CAS}}$ -controlled Write Cycle, when the leading edge of  $\overline{\text{WE}}$  occurs prior to the  $\overline{\text{CAS}}$  low transition, the I/O data pins will be in the High-Z state at the beginning of the Write function. Ending the Write with  $\overline{\text{RAS}}$  or  $\overline{\text{CAS}}$  will maintain the output in the High-Z state.

In the  $\overline{\text{WE}}$  controlled Write Cycle,  $\overline{\text{OE}}$  must be in the high state and  $t_{\text{OED}}$  must be satisfied.

### Refresh Cycle

To retain data, 512 Refresh Cycles are required in each 8 ms period. There are two ways to refresh the memory:

- By clocking each of the 512 row addresses (A<sub>0</sub> through A<sub>8</sub>) with RAS at least once every 8 ms.

Any Read, Write, Read-Modify-Write or RAS-only cycle refreshes the addressed row.

- Using a CAS-before-RAS Refresh Cycle. If CAS makes a transition from low to high to low after the previous cycle and before RAS falls, CAS-before-RAS refresh is activated. The V53C8129H uses the output of an internal 9-bit counter as the source of row addresses and ignore external address inputs.

CAS-before-RAS is a "refresh-only" mode and no data access or device selection is allowed. Thus, the output remains in the High-Z state during the cycle. A CAS-before-RAS counter test mode is provided to ensure reliable operation of the internal refresh counter.

### Extended Data Out Page Mode

The V53C8129H offers fast access within a row. Unlike ordinary fast page mode DRAM, the V53C8129H output remains active and valid even after CAS goes high and it will stay valid for 5ns after CAS changes low. The feature allows the V53C8129H to CAS cycle faster than ordinary page mode DRAM since the cycle time be short as data access time.

The outputs are disabled at the tHZ time after  $\overline{RAS}$  and  $\overline{CAS}$  are high. The tHZ time is referenced from rising edge of  $\overline{RAS}$  or  $\overline{CAS}$  whichever occurs last. In addition, high on  $\overline{OE}$  input and activation of the write-cycle will also disable the outputs.

The following equation can be used to calculate the maximum data rate:

$$\text{Data Rate} \, = \, \frac{256}{t_{RC} + 255 \times t_{PC}}$$

#### **Data Output Operation**

The V53C8129H Input/Output is controlled by OE. CAS. WE and RAS. A RAS low transition enables the transfer of data to and from the selected row address in the Memory Array. A RAS high transition disables data transfer and latches the output data if the output is enabled. After a memory cycle is initiated with a RAS low transition, a CAS low transition or CAS low level enables the internal I/O path. A CAS high transition or a CAS high level disables the I/O path and the output driver if it is enabled. A CAS low transition while RAS is high has no effect on the I/O data path or on the output drivers. The output drivers, when otherwise enabled. can be disabled by holding OE high. The OE signal has no effect on any data stored in the output latches. A WE low level can also disable the output drivers when CAS is low. During a Write cycle, if WE goes low at a time in relationship to CAS that would normally cause the outputs to be active, it is necessary to use  $\overline{OE}$  to disable the output drivers prior to the WE low transition to allow Data In Setup Time (t<sub>DS</sub>) to be satisfied.

#### Power-On

After application of the  $V_{CC}$  supply, an initial pause of 200  $\mu s$  is required followed by a minimum of 8 initialization cycles (any combination of cycles containing a  $\overline{RAS}$  clock). Eight initialization cycles are required after extended periods of bias without clocks (greater than the Refresh Interval).

During Power-On, the  $V_{CC}$  current requirement of the V53C8129H is dependent on the input levels of  $\overline{RAS}$  and  $\overline{CAS}$ . If  $\overline{RAS}$  is low during Power-On, the device will go into an active cycle and  $I_{CC}$  will exhibit current transients. It is recommended that  $\overline{RAS}$  and  $\overline{CAS}$  track with  $V_{CC}$  or be held at a valid  $V_{IH}$  during Power-On to avoid current surges.

**Table 1. V53C8129H Data Output**Operation for Various Cycle Types

| Cycle Type                                | I/O State                               |

|-------------------------------------------|-----------------------------------------|

| Read Cycles                               | Data from Addressed Memory<br>Cell      |

| CAS-Controlled Write Cycle (Early Write)  | High-Z                                  |

| WE-Controlled Write Cycle (Late Write)    | ŌĒ Controlled.<br>High ŌĒ = High-Z I/Os |

| Read-Modify-Write Cycles                  | Data from Addressed Memory<br>Cell      |

| EDO Page Mode Read                        | Data from Addressed Memory<br>Cell      |

| EDO Page Mode Write Cycle (Early Write)   | High-Z                                  |

| EDO Page Mode Read-<br>Modify-Write Cycle | Data from Addressed Memory<br>Cell      |

| RAS-only Refresh                          | High-Z                                  |

| CAS-before-RAS Refresh<br>Cycle           | Data remains as in previous cycle       |

| CAS-only Cycles                           | High-Z                                  |

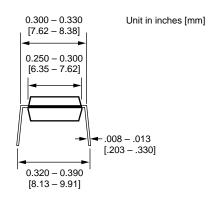

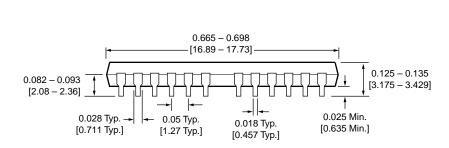

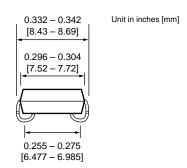

## Package Outlines

## 24-pin 300 mil PDIP

## 26/24-pin 300 mil SOJ

#### **MOSEL VITELIC**

#### **WORLDWIDE OFFICES**

#### V53C8129H

#### U.S.A.

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0185

#### **HONG KONG**

19 DAI FU STREET TAIPO INDUSTRIAL ESTATE TAIPO, NT, HONG KONG PHONE: 011-852-665-4883 FAX: 011-852-664-7535

#### **TAIWAN**

7F, NO. 102 MIN-CHUAN E. ROAD, SEC. 3 TAIPEI

PHONE: 011-886-2-545-1213 FAX: 011-886-2-545-1209

1 CREATION ROAD I SCIENCE BASED IND. PARK HSIN CHU, TAIWAN, R.O.C. PHONE: 011-886-35-783344 FAX: 011-886-35-792838

#### **JAPAN**

RM.302 ANNEX-G HIGASHI-NAKANO NAKANO-KU, TOKYO 164 PHONE: 011-81-03-3365-2851 FAX: 011-81-03-3365-2836

## U.S. SALES OFFICES

#### **NORTHWESTERN**

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0185

#### **NORTHEASTERN**

SUITE 436 20 TRAFALGAR SQUARE NASHUA, NH 03063 PHONE: 603-889-4393 FAX: 603-889-9347

#### **SOUTHWESTERN**

SUITE 200 5150 E. PACIFIC COAST HWY. LONG BEACH, CA 90804 PHONE: 310-498-3314 FAX: 310-597-2174

#### **CENTRAL & SOUTHEASTERN**

604 FIELDWOOD CIRCLE RICHARDSON, TX 75081 PHONE: 972-690-1402 FAX: 972-690-0341

© Copyright 1997, MOSEL VITELIC Inc.

7/97 Printed in U.S.A.

The information in this document is subject to change without notice.

MOSEL VITELIC makes no commitment to update or keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of MOSEL-VITELIC.

MOSEL VITELIC subjects its products to normal quality control sampling techniques which are intended to provide an assurance of high quality products suitable for usual commercial applications. MOSEL VITELIC does not do testing appropriate to provide 100% product quality assurance and does not assume any liability for consequential or incidental arising from any use of its products. If such products are to be used in applications in which personal injury might occur from failure, purchaser must do its own quality assurance testing appropriate to such applications.