Advance Information

DS4575 - 2.2 October 1998

## **NTSC/PAL Digital Video Encoder**

## SEMICONDUCTOR

Supersedes DS4575 1.5 May 1997 version

**/ITEL**

The VP5311/VP5511 converts digital Y, Cr, Cb, data

into analog NTSC/PAL composite video and S-video signals. The outputs are capable of driving doubly terminated 75 ohm loads with standard video levels.

The device accepts data inputs complying with CCIR Recommendation 601 and 656. The data is time multiplexed on an 8 bit bus at 27MHz and is formatted as Y, Cr, Y, Cb (i.e. 4:2:2). The video blanking and sync information from REC 656 is included in the data stream when the VP5311/ VP5511 is working in slave mode.

The output pixel rate is 27MHz and the input pixel rate is half this frequency, i.e. 13.5MHz.

All necessary synchronisation signals are generated internally when the device is operating in master mode. In slave mode the device will lock to the TRS codes or the HS and VS inputs.

The rise and fall times of sync, burst envelope and video blanking are internally controlled to be within composite video specifications.

Three digital to analog converters (DACs) are used to convert the digital luminance, chrominance and composite data into true analog signals. An internally generated reference voltage provides the biasing for the DACs.

## FEATURES

- Converts Y, Cr, Cb data to analog composite video and S-video

- Supports CCIR recommendations 601 and 656

- All digital video encoding

- Selectable master/slave mode for sync signals

- Switchable chrominance bandwidth

- Switchable pedestal with gain compensation

- SMPTE 170M NTSC or CCIR 624 PAL compatible outputs

- GENLOCK mode

- Line 21 Closed Caption encoding

- I<sup>2</sup>C bus serial microprocessor interface

- VP5311B supports Macrovision anti-taping format Rev. 6.1, in PAL and Rev. 7.01 in NTSC.

## **APPLICATIONS**

- Digital Cable TV

- Digital Satellite TV

- Multi-media

- Video games

- Karaoke

- Digital VCRs

#### **ORDERING INFORMATION**

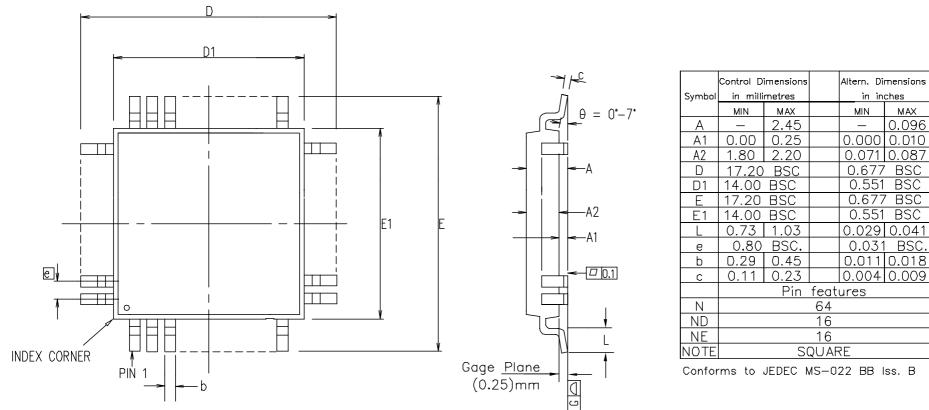

VP5311B/CG/GP1N VP5511B/CG/GP1N

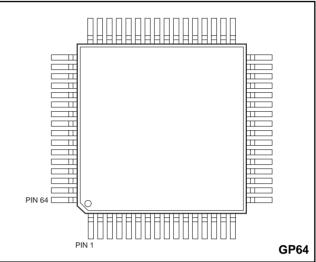

Figure 1 Pin connections (top view)

|     | <u> </u>        | ,   |           |

|-----|-----------------|-----|-----------|

| PIN | FUNCTION        | PIN | FUNCTION  |

| 1   | VDD             | 33  | VDD       |

| 2   | GND             | 34  | RESET     |

| 3   | D0 (VS I/O)     | 35  | REFSQ     |

| 4   | D1 (HS I/O)     | 36  | GND       |

| 5   | D2 (FC0 O/P)    | 37  | VDD       |

| 6   | D3 (FC1 O/P)    | 38  | GND       |

| 7   | D4 (FC2 O/P)    | 39  | PD7       |

| 8   | D5              | 40  | PD6       |

| 9   | D6 (SCSYNC I/P) | 41  | PD5       |

| 10  | D7 (PALID I/P)  | 42  | PD4       |

| 11  | GND             | 43  | PD3       |

| 12  | VDD             | 44  | PD2       |

| 13  | GND             | 45  | PD1       |

| 14  | GND             | 46  | PD0       |

| 15  | PXCK            | 47  | GND       |

| 16  | VDD             | 48  | VDD       |

| 17  | CLAMP           | 49  | AGND      |

| 18  | COMPSYNC        | 50  | VREF      |

| 19  | GND             | 51  | DACGAIN   |

| 20  | VDD             | 52  | COMP      |

| 21  | TDO             | 53  | AVDD      |

| 22  | TDI             | 54  | LUMAOUT   |

| 23  | TMS             | 55  | AGND      |

| 24  | TCK             | 56  | COMPOUT   |

| 25  | GND             | 57  | AGND      |

| 26  | SA1             | 58  | CHROMAOUT |

| 27  | SA2             | 59  | AVDD      |

| 28  | SCL             | 60  | N/C       |

| 29  | VDD             | 61  | N/C       |

| 30  | SDA             | 62  | AVDD      |

| 31  | GND             | 63  | AVDD      |

| 32  | VDD             | 64  | N/C       |

## **ELECTRICAL CHARACTERISTICS**

# Test conditions (unless otherwise stated): As specified in Recommended Operating Conditions DC CHARACTERISTICS

| Parameter                                       | Conditions | Symbol | Min.    | Тур. | Max.    | Units |

|-------------------------------------------------|------------|--------|---------|------|---------|-------|

| Digital Inputs TTL compatible (except SDA, SCL) |            |        |         |      |         |       |

| Input high voltage                              |            | VIN    | 2.0     |      |         | V     |

| Input low voltage                               |            | VIL    |         |      | 0.8     | V     |

| Digital Inputs SDA, SCL                         |            |        |         |      |         |       |

| Input high voltage                              |            | VIH    | 0.7 VDD |      |         | V     |

| Input low voltage                               |            | VIL    |         |      | 0.3 VDD | V     |

| Input high current                              | VIN = VDD  | IIH    |         |      | 10      | μΑ    |

| Input low current                               | VIN = VSS  | IIL    |         |      | -10     | μΑ    |

| Digital Outputs CMOS compatible                 |            |        |         |      |         |       |

| Output high voltage                             | IOH = -1mA | VOH    | 3.7     |      |         | V     |

| Output low voltage                              | IOL = +4mA | VOL    |         |      | 0.4     | V     |

| Digital Output SDA                              |            |        |         |      |         |       |

| Output low voltage                              | IOL = +6mA | VOL    |         |      | 0.6     | V     |

### **ELECTRICAL CHARACTERISTICS**

## Test conditions (unless otherwise stated): As specified in Recommended Operating Conditions DC CHARACTERISTICS DACs

| Parameter                                                                                                                                                                                                                                                     | Symbol                           | Min. | Тур.                                            | Max.             | Units                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|-------------------------------------------------|------------------|---------------------------------------|

| Accuracy (each DAC)<br>Integral linearity error<br>Diffential linearity error<br>DAC matching error<br>Monotonicity<br>LSB size<br>Internal reference voltage<br>Internal reference voltage output impedance<br>Reference Current (VREF/RREF) RREF = 769Ω     | INL<br>DNL<br>Vref<br>Zr<br>Iref |      | guaranteed<br>66.83<br>1.050<br>27k<br>1.3699   | ±1.5<br>±1<br>±5 | LSB<br>LSB<br>%<br>μA<br>V<br>Ω<br>mA |

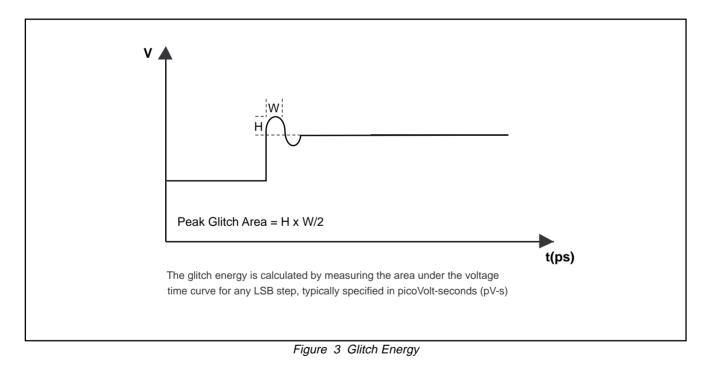

| DAC Gain Factor (Vout = KDAC x IREF x RL), Vout = DAC code 511<br>Peak Glitch Energy (see fig.3)                                                                                                                                                              | Kdac                             |      | 24.93<br>50                                     |                  | pV-s                                  |

| CVBS, Y and C - NTSC (pedestal enabled)<br>Maximum output, relative to sync bottom<br>White level relative to black level<br>Black level relative to blank level<br>Blank level relative to sync level<br>Colour burst peak - peak<br>DC offset (bottom sync) |                                  |      | 33.75<br>17.64<br>1.40<br>7.62<br>7.62<br>0.40  |                  | mA<br>mA<br>mA<br>mA<br>mA            |

| CVBS, Y and C - PAL<br>Maximum output<br>White level relative to black level<br>White level relative to sync level<br>Black level relative to sync level<br>Colour burst peak - peak<br>DC offset (bottom sync)                                               |                                  |      | 34.15<br>18.71<br>26.73<br>8.02<br>8.02<br>0.00 |                  | mA<br>mA<br>mA<br>mA<br>mA            |

**Note:** All figures are for:  $R_{REF} = 769\Omega R_{L} = 37.5\Omega$ . When the device is set up in NTSC mode there is a +0.25% error in the PAL levels. If  $R_{L} = 75\Omega$  then  $R_{REF} = 1538\Omega$ .

## ABSOLUTE MAXIMUM RATINGS

Supply voltageVDD, AVDDVoltage on any non power pin-0-3 toAmbient operating temperature-55

-0.3 to 7.0V -0.3 to VDD+0.3V 0 to 70°C -55°C to 150°C Note: Stresses exceeding these listed under Absolute Maximum Ratings may induce failure. Exposure to Absolute Maximum Ratings for extended periods may reduce reliability. Functionality at or above these conditions is not implied.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                       | Symbol    | Min.   | Тур.  | Max.   | Units |

|-------------------------------------------------|-----------|--------|-------|--------|-------|

| Power supply voltage                            | VDD, AVDD | 4.75   | 5.00  | 5.25   | V     |

| Power supply current (including analog outputs) | IDD       |        | 150   |        | mA    |

| Input clock frequency                           | PXCK      | -50ppm | 27.00 | +50ppm | MHz   |

| SCL clock frequency                             | fsc∟      |        |       | 500    | kHz   |

| Analog video output load                        |           |        | 37.5  |        | Ω     |

| DAC gain resistor                               |           |        | 769   |        | Ω     |

| Ambient operating temperature                   |           | 0      |       | 70     | °C    |

## VIDEO CHARACTERISTICS

| 5.5<br>1.3<br>650<br>3.57954545<br>4.43361875<br>3.58205625<br>9<br>10 |                                                                    | MHz<br>MHz<br>kHz<br>MHz<br>MHz<br>Fsc cycles                                           |

|------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 650<br>3.57954545<br>4.43361875<br>3.58205625<br>9                     |                                                                    | kHz<br>MHz<br>MHz<br>MHz<br>Fsc cycles                                                  |

| 3.57954545<br>4.43361875<br>3.58205625<br>9                            |                                                                    | MHz<br>MHz<br>MHz<br>Fsc cycles                                                         |

| 4.43361875<br>3.58205625<br>9                                          |                                                                    | MHz<br>MHz<br>Fsc cycles                                                                |

| 3.58205625<br>9                                                        |                                                                    | MHz<br>Fsc cycles                                                                       |

| 9                                                                      |                                                                    | Fsc cycles                                                                              |

| °                                                                      |                                                                    |                                                                                         |

| 10                                                                     |                                                                    |                                                                                         |

|                                                                        |                                                                    | Fsc cycles                                                                              |

| 300                                                                    |                                                                    | ns                                                                                      |

| 300                                                                    |                                                                    | ns                                                                                      |

| 145                                                                    |                                                                    | ns                                                                                      |

| 245                                                                    |                                                                    | ns                                                                                      |

| 1.5                                                                    |                                                                    | % pk-pk                                                                                 |

| 0.5                                                                    |                                                                    | ° pk-pk                                                                                 |

| -61                                                                    |                                                                    | dB                                                                                      |

| -56                                                                    | -61                                                                | dB                                                                                      |

| -58                                                                    | -56                                                                | dB                                                                                      |

|                                                                        | -58                                                                | %                                                                                       |

|                                                                        | 2.5                                                                | %                                                                                       |

| -60                                                                    | 2.5                                                                | dB                                                                                      |

| 10                                                                     |                                                                    | ns                                                                                      |

|                                                                        | 300<br>300<br>145<br>245<br>1.5<br>0.5<br>-61<br>-56<br>-58<br>-60 | 300<br>300<br>145<br>245<br>1.5<br>0.5<br>-61<br>-56<br>-58<br>-58<br>2.5<br>-60<br>2.5 |

## ESD COMPLIANCE

| Pins     | Test             | Test Levels                              | Notes                     |

|----------|------------------|------------------------------------------|---------------------------|

| All pins | Human body model | 2kV on 100pF through 1k5 $\Omega$        | Meets Mil-Std-883 Class 2 |

| All pins | Machine model    | 200V on 200pF through 0 $\Omega$ & 500nH |                           |

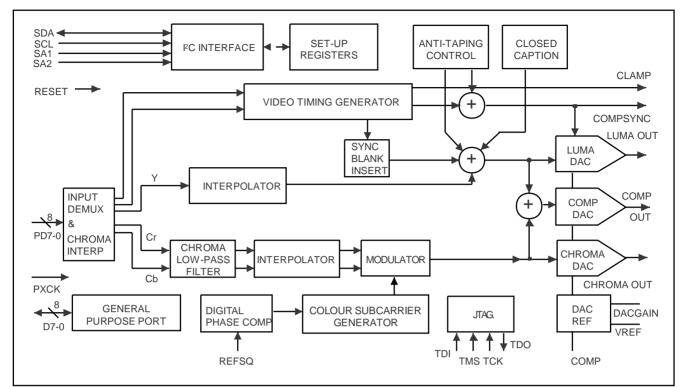

Figure 2 Functional block diagram of the VP5311B, the VP5511B is identical except there is no Anti-Taping Control

## **PIN DESCRIPTIONS**

| Pin Name  | Pin No.    | Description                                                                                                                                                                                                                                                                     |

|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD0-7     | 39 - 46    | 8 Bit Pixel Data inputs clocked by PXCK. PD0 is the least significant bit, corresponding to Pin 46. These pins are internally pulled low.                                                                                                                                       |

| D0-7      | 3 - 10     | 8 Bit General Purpose Port input/output. D0 is the least significant bit, corresponding to Pin 3. These pins are internally pulled low.                                                                                                                                         |

| PXCK      | 15         | 27MHz Pixel Clock input. The VP5311 internally divides PXCK by two to provide the pixel clock.                                                                                                                                                                                  |

| CLAMP     | 17         | The CLAMP output signal is synchronised to COMPSYNC output and indicates the position of the BURST pulse, (lines 10-263 and 273-525 for NTSC; lines 6-310 and 319-623 for PAL-B,D, G,I,N(Argentina)).                                                                           |

| COMPSYNC  | 18         | Composite sync pulse output. This is an active low output signal.                                                                                                                                                                                                               |

| TDO       | 21         | JTAG Data scan output port.                                                                                                                                                                                                                                                     |

| TDI       | 22         | JTAG Data scan input port.                                                                                                                                                                                                                                                      |

| TMS       | 23         | JTAG Scan select input.                                                                                                                                                                                                                                                         |

| тск       | 24         | JTAG Scan clock input.                                                                                                                                                                                                                                                          |

| SA1       | 26         | Slave address select.                                                                                                                                                                                                                                                           |

| SA2       | 27         | Slave address select.                                                                                                                                                                                                                                                           |

| SCL       | 28         | Standard I <sup>2</sup> C bus serial clock input.                                                                                                                                                                                                                               |

| SDA       | 30         | Standard I <sup>2</sup> C bus serial data input/output.                                                                                                                                                                                                                         |

| RESET     | 34         | Master reset. This is an asynchronous, active low, input signal and must be asserted for a minimum 200ns in order to reset the VP5311.                                                                                                                                          |

| REFSQ     | 35         | Reference square wave input used only during Genlock mode.                                                                                                                                                                                                                      |

| VREF      | 50         | Voltage reference output. This output is nominally $1.055V$ and should be decoupled with a 100nF capacitor to GND.                                                                                                                                                              |

| DAC GAIN  | 51         | DAC full scale current control. A resistor connected between this pin and GND sets the magnitude of the video output current. An internal loop amplifier controls a reference current flowing through this resistor so that the voltage across it is equal to the Vref voltage. |

| COMP      | 52         | DAC compensation. A 100nF ceramic capacitor must be connected between pin 52 and pin 53.                                                                                                                                                                                        |

| LUMAOUT   | 54         | True luminance, composite and chrominance video signal outputs. These are high                                                                                                                                                                                                  |

| COMPOUT   | 56 >       | impedance current source outputs. A DC path to GND must exist from each of these pins.                                                                                                                                                                                          |

| CHROMAOUT | 58 )       |                                                                                                                                                                                                                                                                                 |

| NOT USED  | 60, 61, 64 |                                                                                                                                                                                                                                                                                 |

| VDD       | 1, 12, 16, | Positive supply input. All VDD pins must be connected.                                                                                                                                                                                                                          |

|           | 20, 29,    |                                                                                                                                                                                                                                                                                 |

|           | 32, 33,    |                                                                                                                                                                                                                                                                                 |

|           | 37, 48     |                                                                                                                                                                                                                                                                                 |

| AVDD      | 53, 59     | Analog positive supply input. All AVDD pins must be connected.                                                                                                                                                                                                                  |

|           | 62, 63     |                                                                                                                                                                                                                                                                                 |

| GND       | 2, 11, 13, | Negative supply input. All GND pins must be connected.                                                                                                                                                                                                                          |

|           | 14, 19,    |                                                                                                                                                                                                                                                                                 |

|           | 25, 31,    |                                                                                                                                                                                                                                                                                 |

|           | 36, 38, 47 |                                                                                                                                                                                                                                                                                 |

| AGND      | 49, 55, 57 | Negative supply input. All AGND pins must be connected.                                                                                                                                                                                                                         |

All other pins are N/C and should not be connected.

### **REGISTERS MAP**

See Register Details for further explanations.

| ADDRESS        | REGISTER           |              |          |             |             |             |          |                  |        |            | DEFAULT |

|----------------|--------------------|--------------|----------|-------------|-------------|-------------|----------|------------------|--------|------------|---------|

| hex            | NAME               | 7            | 6        | 5           | 4           | 3           | 2        | 1                | 0      | R/W        | hex     |

|                | BAR                | RA7          | RA6      | RA5         | RA4         | RA3         | RA2      | RA1              | RA0    | W          |         |

| 00             | PART ID2           | ID17         | ID16     | ID15        | ID14        | ID13        | ID12     | ID11             | ID10   | R          | 13      |

| 01             | PART ID1           | ID0F         | ID0E     | ID0D        | ID0C        | ID0B        | ID0A     | ID09             | ID08   | R          | 66      |

| 02             | PART ID0           | ID07         | ID06     | ID05        | ID04        | ID03        | ID02     | ID01             | ID00   | R          | 58      |

| 03             | REV ID             | REV7         | REV6     | REV5        | REV4        | REV3        | REV2     | REV1             | REV0   | R          | 05      |

| 04             | GCR                | -            | -        | YCDELAY     |             | SLH&V       | CVBSCLP  | VFS1             | VFS0   | R/W        | 00      |

| 05             | VOCR               | -            | CLAMPDIS |             | SYNCDIS     | BURDIS      | LUMDIS   | CHRDIS           | PEDEN  | R/W        | 00      |

| 06             | HANC               | -            | -        | DFI2        | DFI1        | DFI0        | Reserved | Reserved         | ACTREN | *          | 00      |

| 07             | ANCID              | AN7          | AN6      | AN5         | AN4         | AN3         | AN2      | AN1              | PARITY | R/W        | 00      |

| 08             | SC_ADJ             | SC7          | SC6      | SC5         | SC4         | SC3         | SC2      | SC1              | SC0    | R/W        | 9C      |

| 09             | FREQ2              | FR17         | FR16     | FR15        | FR14        | FR13        | FR12     | FR11             | FR10   | R/W        | 87      |

| 0A             | FREQ1              | FR0F         | FR0E     | FR0D        | FR0C        | FR0B        | FR0A     | FR09             | FR08   | R/W        | C1      |

| 0B             | FREQ0              | FR07         | FR06     | FR05        | FR04        | FR03        | FR02     | FR01             | FR00   | R/W        | F1      |

| 0C             | SCHPHM             | -            | -        | -           | -           | -           | -        | -                | SCH8   | R/W        | 00      |

| 0D             | SCHPHL             | SCH7         | SCH6     | SCH5        | SCH4        | SCH3        | SCH2     | SCH1             | SCH0   | R/W        | 00      |

| 0E to 1F       | Reserved           |              |          |             |             |             |          |                  |        |            |         |

| 20             | GPPCTL             | CTL7         | CTL6     | CTL5        | CTL4        | CTL3        | CTL2     | CTL1             | CTL0   | W          | FF      |

| 21             | GPPRD              | RD7          | RD6      | RD5         | RD4         | RD3         | RD2      | RD1              | RD0    | R          | -       |

| 22             | GPPWR              | WR7          | WR6      | WR5         | WR4         | WR3         | WR2      | WR1              | WR0    | W          | 00      |

| 23 to EF       | Not used           |              |          |             |             |             |          |                  |        |            |         |

| F0             | CCREG1             | -            | F1W1D6   | F1W1D5      | F1W1D4      | F1W1D3      | F1W1D2   | F1W1D1           | F1W1D0 | R/W        | 00      |

| F1             | CCREG2             | -            | F1W2D6   | F1W2D5      | F1W2D4      | F1W2D3      | F1W2D2   | F1W2D1           | F1W2D0 | R/W        | 00      |

| F2             | CCREG3             | -            | F2W1D6   | F2W1D5      | F2W1D4      | F2W1D3      | F2W1D2   | F2W1D1           | F2W1D0 | R/W        | 00      |

| F3<br>F4       | CCREG4             | -            | F2W2D6   | F2W2D5      | F2W2D4      | F2W2D3      | F2W2D2   | F2W2D1           | F2W2D0 | R/W        | 00      |

| F4<br>F0 to F7 | CC_CTL<br>Reserved | -            | -        | -           | -           | F2ST        | F1ST     | F2EN             | F1EN   | R/W        | 00      |

| F0 t0 F7<br>F8 | HSOFFL             | HSOFF7       | HSOFF6   | HSOFF5      | HSOFF4      | HSOFF3      | HSOFF2   | HSOFF1           | HS0FF0 | R/W        | 7E      |

| F0<br>F9       | HSOFFL             |              | -        |             |             | -           |          | HSOFF1<br>HSOFF9 | HSOFF8 | R/W<br>R/W | 00      |

| F9<br>FB       | SLAVE1             | -<br>NCORSTD | VBITDIS  | -<br>VSMODE | -<br>F SWAP | -<br>SL HS1 | SL HS0   | HCNT9            | HCNT8  | R/W        | 00      |

| FC             | SLAVE1             | HCNT7        | HCNT6    | HCNT5       | HCNT4       | HCNT3       | HCNT2    | HCNT1            | HCNT0  | R/W        | 00      |

| FD             | TEST1              |              |          |             | RESERVED    | FOR         | TEST     |                  |        | R/W        |         |

| FE             | TEST2              |              |          |             | RESERVED    | FOR         | TEST     |                  |        | R/W        |         |

| FF             | GPSCTL             | FSC4SEL      |          |             | NOLOCK      | PALIDEN     | TSURST   | CHRMCLIP         | TRSEL  | R/W        | 00      |

#### Table.1 Register map

NOTE \* For register HANC, bits 3, 4 and 5 are read only. Bits 1 and 2 are reserved. N/A = not applicable. For register PART ID0 the VP551 value is AB

| Standard          | Lines/<br>field | Field<br>freq. Hz | Number of<br>pixels/line<br>at 27MHz | Horizontal<br>freq. kHz.<br>fн | Subcarrier<br>freq. kHz.<br>fsc | fsc/fн         | SC_ADJ<br>register<br>hex | FREQ2-0<br>registers hex |

|-------------------|-----------------|-------------------|--------------------------------------|--------------------------------|---------------------------------|----------------|---------------------------|--------------------------|

| NTSC (default)    | 525             | 59.94             | 1716                                 | 15.734266                      | 3.57954545                      | (455/2)        | XX                        | 87 C1 F1                 |

| PAL-B, G, H, I    | 625             | 50                | 1728                                 | 15.625000                      | 4.43361875                      | (1135/4+1/625) | 9C                        | A8 26 2B                 |

| PAL-N (Argentina) | 625             | 50                | 1728                                 | 15.625000                      | 3.58205625                      | (917/4+1/625)  | 57                        | 87 DA 51                 |

Table.2 Line, field and subcarrier standards and register settings

xx = don't care.

The calculation of the FREQ register value is according to the following formula:-

FREQ =  $2^{26} \times \text{fsc/PXCK}$  hex, where PXCK = 27.00MHz

NTSC value is rounded UP from the decimal number. PAL-B, D, G, H, I and N (Argentina) are rounded DOWN. The SC\_ADJ value is derived from the adjustment needed to be added after 8 fields to ensure accuracy of the Subcarrier frequency. Note the SC\_ADJ value of 9C required for PAL-B, D, G, H, I, is different to the default state of the register.

In NTSC the NCO is reset at the end of every line, this can be disabled by setting the NCORSTD bit in SLAVE1, this allows the VP5311 to cope with line lengths that are not exactly as specified in REC656.

| REGISTER D                    |                                                                                                                                                                                          | PEDEN                     | High = Pedestal (set-up) enable a<br>7·5 IRE pedestal on lines 23-262 and                                                                                                                                                                                                     |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAR                           | Base register                                                                                                                                                                            |                           | 286-525. Valid for NTSC                                                                                                                                                                                                                                                       |

| RA7-0                         | Register address.                                                                                                                                                                        | HANC                      | Horizontal Ancillary Data Control                                                                                                                                                                                                                                             |

| <b>PART ID 2-0</b><br>ID17-00 | <b>Part number</b><br>Chip part identification (ID) number.                                                                                                                              |                           | y)Digital Field Identification, 000=Field1<br>Ancillary timing reference enable. When<br>High use FIELD COUNT from ancillary                                                                                                                                                  |

| <b>REV ID</b><br>REV7-0       | Revision number<br>Chip revision ID number.                                                                                                                                              |                           | data stream. When low, data is ignored.                                                                                                                                                                                                                                       |

| <b>GCR</b><br>YCDELAY         | <b>Global Control</b><br>Luma to Chroma delay.<br>High = 37ns luma delay, this may be<br>used to compensate for group delay in<br>external filters.<br>Low = normal operation (default). | ANCID<br>AN7-1<br>AN0     | Ancillary data ID<br>Ancillary data ID<br>Parity bit (odd)<br>Only ancillary data in REC 656 data<br>stream with the same ID as this byte will<br>be decoded by the VP5311/VP5511 to<br>produce H and V synchronisation and<br>FIELD COUNT.                                   |

| RAMPEN                        | Modulated ramp enable.<br>High = ramp output for differential phase<br>and gain measurements. A 27MHz clock<br>must be applied to PXCK pin.<br>Low = normal operation (default).         | SC_ADJ<br>SC7-0           | <b>Sub Carrier Adjust</b><br>Sub carrier frequency seed value, see<br>table 2.                                                                                                                                                                                                |

| SL_HS_VS<br>CVBSCLMP          | <ul> <li>1 = Slave to HS and VS inputs</li> <li>1 = Enables clamp on composite output,<br/>to prevent flatenning of chroma peak<br/>throughs</li> </ul>                                  | FREQ2-0<br>FR17-00        | <b>Sub carrier frequency</b><br>24 bit Sub carrier frequency programmed<br>via I <sup>2</sup> C bus, see table 2. FREQ2 is the<br>most significant byte (MSB).                                                                                                                |

| VFS1-0                        | Video format select<br>VFS1VFS0<br>0 0 NTSC (default)<br>0 1 PAL-B, D, G,H,I,N(Argentina)<br>1 0 Reserved<br>1 1 Reserved                                                                | SCHPHM-L<br>SCH9-0        | Sub carrier phase offset<br>9 bit Sub carrier phase relative to the<br>50% point of the leading edge of the<br>horizontal part of composite sync.<br>SCHPHM bit 0 is the MSB. The nominal<br>value is zero. This register is used to<br>compensate for delays external to the |

| VOCR<br>CLAMPDIS              | <b>Video Output Control</b><br>High = Clamp signal disable<br>Low = normal operation with clamp signal<br>enabled (default).                                                             | <b>GPPCTL</b><br>CTL7-0   | VP5311/VP5511.<br>General purpose port control<br>Each bit controls port direction                                                                                                                                                                                            |

|                               |                                                                                                                                                                                          |                           | Low = output High = input                                                                                                                                                                                                                                                     |

| CHRBW                         | Chroma bandwidth select.<br>High = $\pm 1.3$ MHz.<br>Low = $\pm 650$ kHz (default)                                                                                                       | <b>GPPRD</b><br>RD7-0     | General purpose port read data<br>I <sup>2</sup> C bus read from general purpose port<br>(only INPUTS defined in GPPCTL)                                                                                                                                                      |

| SYNCDIS                       | High = Sync disable (in composite video<br>signal). COMPSYNC is not affected.<br>Low = normal operation with sync<br>enabled (default).                                                  | <b>GPPWR</b><br>WR7-0     | General purpose port write data<br>I <sup>2</sup> C bus write to general purpose port<br>(only OUTPUTS defined in GPPCTL)                                                                                                                                                     |

| BURDIS                        | High = Chroma burst disable.<br>Low = normal operation, with burst<br>enabled (default).                                                                                                 | <b>CCREG1</b><br>F1W1D6-0 | <b>Closed Caption register 1</b><br>Field one (line 21), first data byte                                                                                                                                                                                                      |

| LUMDIS                        | High = Luma input disable - force black<br>level with synchronisation pulses main-                                                                                                       | CCREG2<br>F1W2D6-0        | <b>Closed Caption register 2</b><br>Field one (line 21), second data byte                                                                                                                                                                                                     |

|                               | tained.<br>Low = normal operation, with Luma input<br>enabled (default).                                                                                                                 | CCREG3<br>F2W2D6-0        | <b>Closed Caption register 3</b><br>Field two (line 284), first data byte                                                                                                                                                                                                     |

| CHRDIS                        | High = Chroma input disable - force<br>monochrome.<br>Low = normal operation, with Chroma<br>input enabled (default).                                                                    | <b>CCREG4</b><br>F2W2D6-0 | Closed Caption register 4<br>Field two (line 284), second data byte                                                                                                                                                                                                           |

| CCCTL<br>F1ST                                                        | <b>Closed Caption control register</b><br>Field one (line 21) status<br>High = data has been encoded<br>Low = new data has been loaded to<br>CCREG1-2                                                                                                                       |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F2ST                                                                 | Field two (line 284) status<br>High = data has been encoded<br>Low = new data has been loaded to<br>CCREG3-4                                                                                                                                                                |

| F1EN                                                                 | Closed Caption field one (line 21)<br>High = enable Low = disable (default)                                                                                                                                                                                                 |

| F2EN                                                                 | Closed Caption field two (line 284)<br>High = enable Low = disable (default)                                                                                                                                                                                                |

| HSOFFM-L<br>HSOFF9-0                                                 | <b>HS offset</b><br>This is a 10 bit number which allows the<br>user to offset the start of digital data input<br>with reference to the pulse HS.                                                                                                                           |

| SLAVE1<br>NCORSTD                                                    | H &V Slave mode control register<br>1 = NCO Line Reset Disable (NTSC only)                                                                                                                                                                                                  |

| VBITDIS<br>F_SWAP<br>SL_HS1-0<br>HCNT9-8<br><b>SLAVE2</b><br>HCNT7-0 | 0 = Video blanked when Rec601 V bit set<br>1 = V bit is ignored<br>The odd and even fields are swapped<br>Selects pixel sample (1 to 4)<br>As HCNT7-0 but MSBs<br><b>H &amp;V Slave position register</b><br>Adjusts for delay at which pixel data<br>occurs relative to HS |

| GPSCTL<br>FSC4SEL                                                    | <b>GPS Control</b><br>When high, REFSQ = 4xFSC and GPP<br>bit D6 is forced to become an input for a<br>SCSYNC signal (high = reset), which<br>provides a synchronous phase reset for<br>FSC divider. Low = normal operation with<br>REFSQ = 1xFSC. (default).               |

| GENDITH                                                              | 1 = Gen lock dither added.                                                                                                                                                                                                                                                  |

| GENLKEN                                                              | High = enable Genlock to REFSQ signal<br>input.<br>Low = internal subcarrier generation<br>(default).                                                                                                                                                                       |

| NOLOCK                                                               | Genlock status bit (read only)<br>Low = Genlocked.<br>High = cannot lock to REFSQ. This bit is<br>cleared by reading and set again if lock<br>cannot be attained.                                                                                                           |

| PALIDEN                                                              | High = enable external PAL ID phase<br>control and GPP bit D7 is forced to<br>become an input for PAL ID switch signal,<br>(GPP bit D7 - Low = +135°,<br>High = -135°).<br>Low = normal operation, internal PAL ID<br>phase switch is used (default).                       |

| TSURST   | High = chip soft reset. Registers are NOT<br>reset to default values.<br>Low = normal operation (default).                                                 |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHRMCLIP | High = enable clipping of chroma data<br>when luma goes below black level and is<br>clipped.<br>Low = no chroma clipping (default).                        |

| TRSEL    | High = master mode, GPP bits D0 - 4 are<br>forced to become a video timing port with<br>VS, HS and FIELD outputs.<br>Low = slave mode, timing from REC656. |

## I<sup>2</sup>C BUS CONTROL INTERFACE

#### I<sup>2</sup>C bus address

| A6 | A5 | A4 | A3 | A2 | A1  | A0  | R/ W |

|----|----|----|----|----|-----|-----|------|

| 0  | 0  | 0  | 1  | 1  | SA2 | SA1 | Х    |

The serial microprocessor interface is via the bidirectional port consisting of a data (SDA) and a clock (SCL) line. It is compatible to the Philips I<sup>2</sup>C bus standard (Jan. 1992 publication number 9398 393 40011). The interface is a slave transmitter - receiver with a sub-address capability. All communication is controlled by the microprocessor. The SCL line is input only. The most significant bit (MSB) is sent first. Data must be stable during SCL high periods.

A bus free state is indicated by both SDA and SCL lines being high. START of transmission is indicated by SDA being pulled low while SCL is high. The end of transmission, referred to as a STOP, is indicated by SDA going from low to high while SCL is high. The STOP state can be omitted if a repeated START is sent after the acknowledge bit. The reading device acknowledges each byte by pulling the SDA line low on the ninth clock pulse, after which the SDA line is released to allow the transmitting device access to the bus.

The device address can be partially programmed by the setting of the pins SA1 and SA2. This allows the device to respond to one of four addresses, providing for system flexibility. The I<sup>2</sup>C bus address is seven bits long with the last bit indicating read / write for subsequent bytes.

The first data byte sent after the device address, is the sub-address - BAR (base address register). The next byte will be written to the register addressed by BAR and subsequent bytes to the succeeding registers. The BAR maintains its data after a STOP signal.

#### **NTSC/PAL Video Standards**

Both NTSC (4-field, 525 lines) and PAL (8-field, 625 lines) video standards are supported by the VP5311/VP5511. All raster synchronisation, colour sub-carrier and burst characteristics are adapted to the standard selected. The VP5311/VP5511 generates outputs which follow the requirements of SMPTE 170M and CCIR 624 for PAL signals.

The device supports the following: NTSC, PAL B, D, G, H, I, N (Argentina).

#### **Video Blanking**

The VP5311/VP5511 automatically performs standard composite video blanking. Lines 1-9, 264-272 inclusive, as well as the last half of line 263 are blanked in NTSC mode. In PAL mode, lines 1-5, 311-318, 624-625 inclusive, as well as the last half of line 623 are blanked.

The V bit within REC656 defines the video blanking when TRSEL (bit 0 of GPSCTL register) is set low. When in MASTER mode with TRSEL set high the video encoder is still enabled. Therefore if these lines are required to be blank they must have no video signal input.

#### Interpolator

The luminance and chrominance data are separately passed through interpolating filters to produce output sampling rates double that of the incoming pixel rate. This reduces the sinx/x distortion that is inherent in the digital to analog converters and also simplifies the analog reconstruction filter requirements.

#### **Digital to Analog Converters**

The VP5311/VP5511 contained three 9 bit digital to analog converters which produce the analog video signals. The DACs use a current steering architecture in which bit currents are routed to one of two outputs; thus the DAC has true and complementary outputs. The use of identical current sources and current steering their outputs means that monotonicity is guaranteed. An on-chip voltage reference of 1.050V provides the necessary biasing. However, the VP5311/VP5511 may be used in applications where an external 1V reference is provided on the VREF pin, to adjust the video levels. In this case, the external reference should be temperature compensated and provide a low impedance output.

The full-scale output currents of the DACs is set by an external 769 $\Omega$  resistor between the DACGAIN and GND pins. An on-chip loop amplifier stabilises the full-scale output current against temperature and power supply variations.

The analog outputs of the VP5311/VP5511 are capable of directly driving doubly terminated  $75\Omega$  load then the DACGAIN resistor is simply doubled.

#### Luminance, Chrominance and Composite Video Outputs

The Luminance video output (LUMAOUT pin 54) drives a  $37.5\Omega$  load at 1.0V, sync tip to peak white. It contains only the luminance content of the image plus the composite sync pulses. In the NTSC mode, a set-up level offset can be added during the active video portion of the raster.

The Chrominance video output (CHROMAOUT pin 58) drives a 37.5 $\Omega$  load at levels proportional in amplitude to the luma output (40 IRE pk-pk burst). This output has a fixed offset current which will produce approximately a 0.5V DC bias across the 37.5 $\Omega$  load. Burst is injected with the appropriate timing relative to the luma signal.

The composite video output (COMPOUT pin 56) will also drive a 37.5 $\Omega$  load at 1.0V, sync tip to peak white. It contains both the luminance and chrominance content of the signal plus the composite sync pulses.

The CVBS DAC output clipping feature limits the digital data going into the DAC so that if it goes outside the range it is limited to the maximum or minimum (511 or 000). This feature is permanently enabled.

CVBSCLP in register GCR. When set to a '1' this bit

enables an envelope prediction circuit that establishes if the chroma and luma added together is likely to go outside the CVBS DAC limits. If it is, then a smooth rounding of the chroma peaks is made to stop this happening. This prevents any high frequency components being produced as with the clipping function which will produce flat peaks. In practice there will be some loss of saturation in the colour.

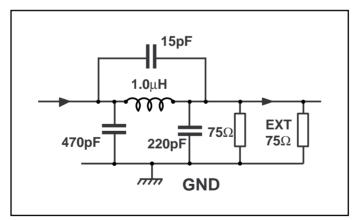

Output sinx/x compensation filters are required on all video output, as shown in the typical application diagram, see figs. 8 & 9.

#### Video Timing - Slave sync mode

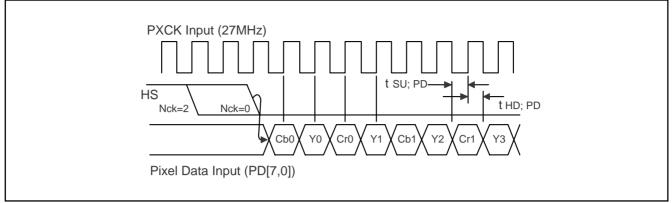

The VP5311/VP5511 has an internal timing generator which produces video timing signals appropriate to the mode of operation. In the default (power up) slave mode, all timing signals are derived from the input clock, PXCK, which must be derived from a crystal controlled oscillator. Input pixel data is latched on the rising edge of the PXCK clock.

The video timing generator produces the internal blanking and burst gate pulses, together with the composite sync output signal, using timing data (TRS codes) from the Ancillary data stream in the REC656 input signal, (when TRSEL (bit 0 of GPSCTL register) is set low).

#### HCNT

To ensure that the incoming data is sampled correctly a 10 bit binary number (HCNT) has to be programmed into the SLAVE1 and 2 registers. This will allow the device's internal horizontal counter to align with the video data, each bit represents one 13.5MHz cycle. To calculate this use the formula below:

#### NTSC

HCNT = SN + 119 (SN = 0 - 738) HCNT = SN + 739 (SN = 739 - 857)

PAL

HCNT = SN + 127 (SN = 0 - 738)

HCNT = SN + 737 (SN = 737 - 863)

where SN is Rec. 656/601 sample number on which the negative edge of HSYNC occurs.

#### SL\_HS

A further adjustment is also required to ensure that the correct Cr and Cb sample alignment. The bits SL\_HS1-0 allows for four sampling positions in the CbYCrY sequence, failure to set this correctly will mean corruption of the colour or colour being interpreted as luma.

#### F\_SWAP

If the field synchronisation is wrong it can be swapped by setting this bit.

#### V\_SYNC

When set to a '1' this bit allows an odd/even square wave to provide the field synchronisation.

## Example

NTSC

HSYNC occurs on Rec656 sample 721 (end of active video), then;

HCNT = 721 + 119 = 839 = 348 Hex

SL\_HS = 10 (for correct sample)

to set slave mode send .04w08pzfbw48pzffw01

| this sets registers as follows: | this | sets | registers | as fol | lows: |

|---------------------------------|------|------|-----------|--------|-------|

|---------------------------------|------|------|-----------|--------|-------|

| reg  | 04 | fb | ff |

|------|----|----|----|

| data | 08 | 0b | 01 |

Note: HSOFF should always be zero when using slave mode.

#### Video Timing - Master sync mode

When TRSEL (bit 0 of GPSCTL register) is set high, the VP5311 operates in a MASTER sync mode, all REC656 timing reference codes are ignored and GPP bits D0 - 4 become a video timing port with VS, HS and FIELD outputs. The PXCK signal is, however, still used to generate all internal clocks. When TRSEL is set high, the direction setting of bits 4 - 0 of the GPPCTL register is ignored.

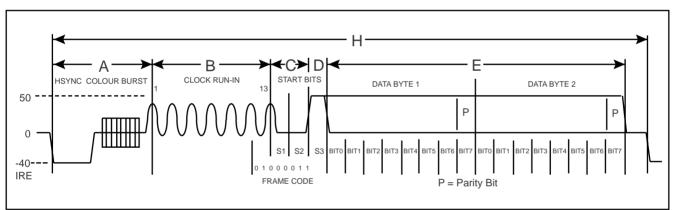

VS is the start of the field sync datum in the middle of the equalisation pulses. HS is the line sync which is used by the preceding MPEG2 decoder to define when to output digital video data to the VP5311. The position of the falling edge of HS relative to the first data Cb0, can be programmed in HSOFFM-L registers, see fig. 4.

#### HS offset

The position of the falling edge of HS relative to the first data Cb0, can be programmed in HSOFFM-L registers, see figure 4, this is called the pipeline delay and may need adjusting for a particular application. This is done by programming a 10 bit number called HSOFF into the HSOFFM and HSOFFL registers, HSOFFM being the most significant two bits and HSOFFL the least significant eight bits. A default value of 07EH is held in the registers.

The value to program into HSOFF can be looked up in tables 3 &4:

| <b>N</b> ск      | HSOFF      | Comment             |  |  |  |  |

|------------------|------------|---------------------|--|--|--|--|

| 0 to 120         | 126 to 6   | HS normal (64 cks)  |  |  |  |  |

| 121 to 138       | 863 to 801 | HS pulse shortened* |  |  |  |  |

| 184 to 857       | 800 to 127 | HS normal (64 cks)  |  |  |  |  |

| Table.3 for NTSC |            |                     |  |  |  |  |

| Nск        | HSOFF      | Comment             |

|------------|------------|---------------------|

| 0 to 131   | 137 to 6   | HS normal (64 cks)  |

| 132 to 194 | 869 to 807 | HS pulse shortened* |

| 195 to 863 | 806 to 138 | HS normal (64 cks)  |

Table.4 for PAL-B, D, G, H, I, N

where  $N_{CK}$  = number of 13.5MHz clock cycles between the falling edge of HS and Cb0 (first data I/P on PD7-0) see fig. 4. Decreasing HSOFF advances the HS pulse (numbers are in decimal).

\*HS pulse shortened means that the width of the pulse will be less than the normal 64 13.5MHz clock cycles.

The interruption in the sequence of values is because the HS signal is jumping across a line boundary to the previous line as the offset is increased. The register default value is 7EH and this sets Nck to 0, ie. the HS negative edge and Cb0 are co-incident in NTSC mode.

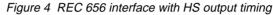

#### Genlock using REFSQ input

The VP5311 can be Genlocked to another video source by setting GENLKEN high (in GPSCTL register) and feeding a phase coherent sub carrier frequency signal into REFSQ. Under normal circumstances, REFSQ will be the same frequency as the sub carrier. But by setting FSC4SEL high (in GPSCTL register), a 4 x sub carrier frequency signal may be input to REFSQ. In this case, the Genlock circuit can be reset to the required phase of REFSQ, by supplying a pulse to SCSYNC (pin 9). The frequency of SCSYNC can be at sub carrier frequency, but once per line, or once per field could be adequate, depending on the application. When GENLKEN is set high, the direction setting of bit 6 in the GPPCTL register is igonred.

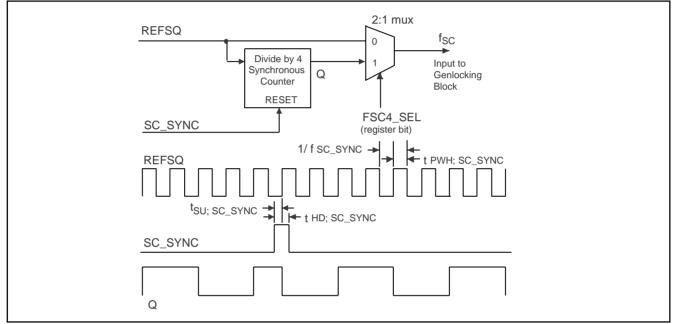

#### **PALID** Input

When in Genlock mode with GENLKEN set high (in GPSCTL register), the VP5311 requires a PAL phase identification signal, to define the correct phase on every line. This is supplied to PALID input (pin 10), High =  $-135^{\circ}$  and low =  $+135^{\circ}$ . The signal is asynchronous and should be changed before the sub carrier burst signal. PALID input is enabled by setting PALIDEN high (in GPSCTL register). When GENLKEN is high, the direction setting of bit 7 of the GPPCTL register is ignored

#### **Master Reset**

The VP5311/VP5511 must be initialised with the RESET pin 34. This is an asynchronous active low signal and must be active for a minimum of 200ns in order for the VP5311/ VP5511 to be reset. The device resets to line 64, start of horizontal sync (i.e. line blanking active). There is no on-chip power on reset circuitry.

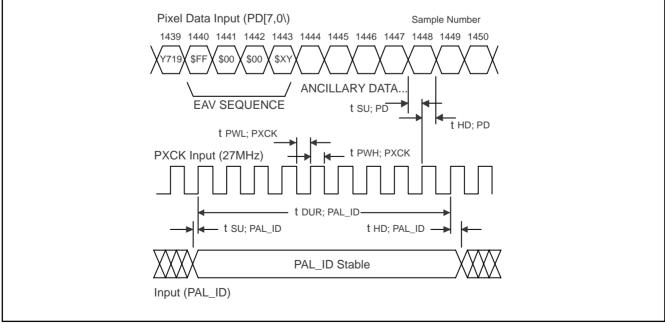

#### Line 21 coding

Two bytes of data are coded on the line 21 of each field, see figure 7. In the NTSC Closed Caption service, the default state is to code on line 21 of field one only. An additional service can also be provided using line 21 (284) of the second field. The data is coded as NRZ with odd parity, after a clock run-in and framing code. The clock run-in frequency = 0.5034965MHz which is related to the nominal line period, D = H / 32.

D = 63.5555556 / 32µs

Two data bytes per field are loaded via I<sup>2</sup>C bus registers CCREG1-4. Each field can be independently enabled by programming the enable bits in the control register (CC\_CTL). The data is cleared to zero in the Closed Caption shift registers after it has been encoded by the VP5311/VP5511. Two status bit are provided (in CC\_CTL), which are set high when data is written to the registers and set low when the data has been encoded on the Luma signal. The data is cleared to zero in the Closed Caption shift registers after it has been encoded by the VP5311/VP5511. The next data bytes must be written to the registers when the status bit goes high, otherwise the Closed Caption data output will contain Null characters. If a transmission slot is missed (ie. no data received) the encoder will send Null characters. Null characters are invisible to a closed caption reciever. The MSB (bit 7) is the parity bit and is automatically added by the encoder.

Figure 5 REFSQ and SC\_SYNC input timing

Figure 6 PAL\_ID input timing

## TIMING INFORMATION

| Parameters                          | Conditions        | Symbol             | Min. | Тур. | Max. | Units   |

|-------------------------------------|-------------------|--------------------|------|------|------|---------|

| Master clock frequency (PXCK input) |                   | fрхск              |      | 27.0 |      | MHz     |

| PXCX pulse width, HIGH              |                   | <b>t</b> рwн; рхск | 10   |      |      | ns      |

| PXCX pulse width, LOW               |                   | tpwl; pxck         | 14.5 |      |      | ns      |

| PXCX rise time                      | 10% to 90% points | <b>t</b> RP        |      |      | TBD  | ns      |

| PXCX fall time                      | 90% to 10% points | <b>t</b> FP        |      |      | TBD  | ns      |

| PD7-0 set up time                   |                   | tsu;pd             | 10   |      |      | ns      |

| PD7-0 hold time                     |                   | thd;pd             | 5    |      |      | ns      |

| SC_SYNC set up time                 |                   | tsu;sc_sync        | 10   |      |      | ns      |

| SC_SYNC hold time                   |                   | thd;sc_sync        | 0    |      |      | ns      |

| PAL_ID set up time                  |                   | tsu;pal_id         | 10   |      |      | ns      |

| PAL_ID hold time                    |                   | thd;pal_id         | 0    |      |      | ns      |

| PAL_ID duration                     |                   | tdur;pal_id        | 9    |      |      | PXCX    |

|                                     |                   |                    |      |      |      | periods |

| Output delay                        | PXCK to COMPSYNC  | toos               |      |      | 25   | ns      |

|                                     | PXCK to CLAMP     |                    |      |      |      |         |

Note: Timing reference points are at the 50% level. Digital C  $_{\text{LOAD}}$  <40pF.

Figure 7 Closed Capation format

| Interval | Description                                                               | Encoder minimum | Encoder nominal  | Encoder maximum |

|----------|---------------------------------------------------------------------------|-----------------|------------------|-----------------|

| А        | H-sync to clock run-in                                                    | 10.250µs        | 10.500µs         | 10.750µs        |

| В        | Clock run-in <sup>2, 3</sup>                                              |                 | 6.5D (12.910μs)  |                 |

| С        | Clock run-in to third start bit <sup>3</sup>                              |                 | 2.0D (3.972µs)   |                 |

| D        | Data bit <sup>1, 3</sup>                                                  |                 | 1.0D (1.986µs)   |                 |

| Е        | Data characters <sup>4</sup>                                              |                 | 16.0D (31.778μs) |                 |

| Н        | Horizontal line <sup>1</sup>                                              |                 | 32.0D (63.556)   |                 |

|          | Rise / fall time of data bit transitions <sup>5</sup>                     |                 | 0.240µs          | 0.288µs         |

|          | Data bit high (logic level one) <sup>6</sup><br>Clock run-in maximum      | 48 IRE          | 50 IRE           | 52 IRE          |

|          | Data bit low (logic level zero) <sup>6</sup><br>Clock run-in minimum      | 0 IRE           | 0 IRE            | 2 IRE           |

|          | Data bit differential (high - low)<br>Clock run-in differential (max min) | 48 IRE          | 50 IRE           | 52 IRE          |

Table. 5 Closed Caption data timing. (source EIA R - 4.3 Sept 16 1992)

Notes

- 1. The Horizontal line frequency f  $_{H}$  is nominally 15734.26Hz ±0.05Hz. Interval D shall be adjusted to D = 1/(f  $_{H}$  x 32) for the instantaneous f  $_{H}$  at line 21.

- 2. The clock run-in signal consists of 7.0 cycles of a 0.5034965MHz (1/D) sine wave when measured from the leading to trailing 0 IRE points. The sine wave is to be symmetrical about the 25 IRE level.

- 3. The negative going midpoints (half amplitude) of the clock run-in shall be coherent with the midpoints (half amplitude) of the Start and Data bit transitions.

- 4. Two characters, each consisting of 7 data bits and 1 odd parity bit.

- 5. 2 T Bar, measured between the 10% and 90% amplitude points.

- 6. The clock run-in maximum level shall not differ from the data bit high level by more than ±1 IRE. The clock run-in minimum level shall not differ from the data bit low level by more than ±1 IRE.

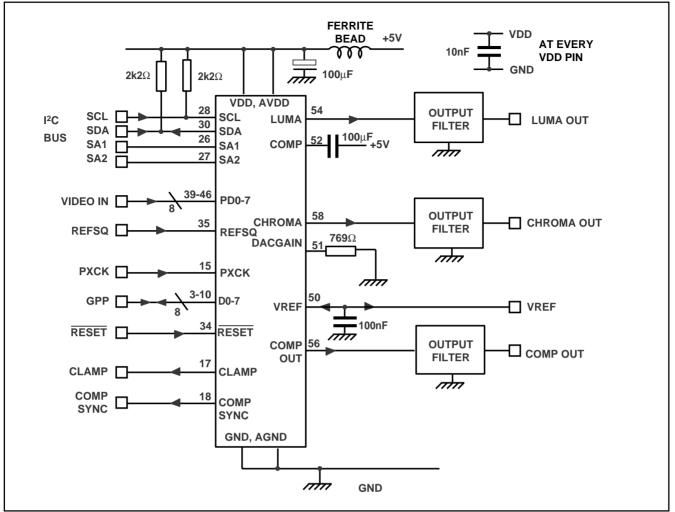

Figure 8 Typical application diagram, SLAVE mode. (Output filter - see Fig.9)

Figure 9 Output reconstruction filter

## Note:

The VP5311 is only available to customers with a valid and existing authorisation to purchase issued by MACROVISION CORPORATION.

This device is protected by U.S. patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. Use of the Macrovision anticopy process in the device is licensed by Macrovision for non-commercial, home and limited exhibition uses only. Reverse engineering or disassembly is prohibited.

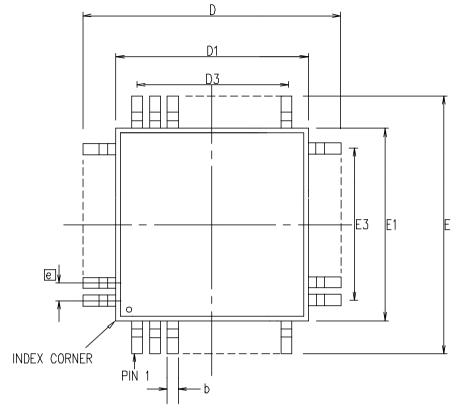

| Symbol | Di    | าร      |       |

|--------|-------|---------|-------|

| • )    | MIN   | Nominal | MAX   |

| Α      |       |         | 3.07  |

| A1     | 0.25  |         |       |

| A2     |       |         | 2.82  |

| D      | 16.95 | 17.20   | 17.45 |

| D1     | 14.82 | 13.97   | 14.12 |

| D3     | 11.90 | 12.00   | 12.10 |

| Ε      | 16.95 | 17.20   | 17.45 |

| E1     | 14.82 | 13.97   | 14.12 |

| E3     | 11.90 | 12.00   | 12.10 |

| L      | 0.60  |         | 1.40  |

| е      |       | 0.80    | BSC   |

| В      | 0.30  | 0.35    | 0.40  |

| С      |       | 0.15    |       |

| Ν      |       | 64      |       |

| ND     |       | 16      |       |

| NE     |       | 16      |       |

| NOTE   | S     | QUARE   |       |

## Notes:

- Pin 1 indentification will be either a dot or a cutout.

All dimensions are in mm.

Applies to GG, GK and GC package types

Coplanarity at [-c-] 0.15mm

This drawing supersedes 418/ED/5380/023 (Swindon)

|          |         |  | <br>        |                  | · · · · · · · · · · · · · · · · · · · |  |  |

|----------|---------|--|-------------|------------------|---------------------------------------|--|--|

| © Mitel  |         |  |             |                  | ORIGINATING SITE: SWINDON             |  |  |

| ISSUE    | 1       |  |             |                  | Title: OUTLINE DRAWING FOR            |  |  |

| ACN      | 203202  |  | <br>  MITEI | EL SEMICONDUCTOR | 64 LEAD QUAD CERPAC (14 X 14 X 2.8)MM |  |  |

| DATE     | 200CT97 |  |             |                  | Drawing Number                        |  |  |

| APPROVED |         |  |             |                  | GPD00463                              |  |  |

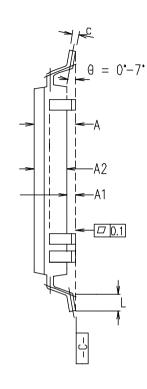

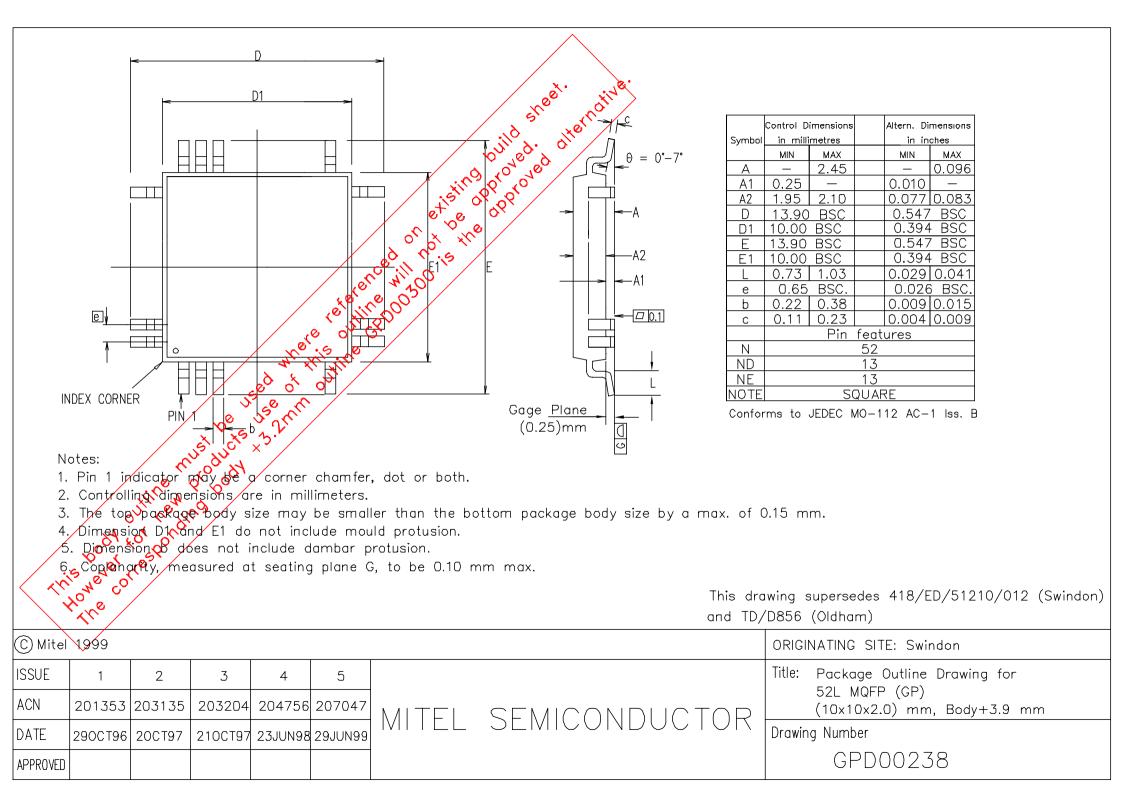

Notes:

- 1. Pin 1 indicator may be a corner chamfer, dot or both.

- 2. Controlling dimensions are in millimeters.

- 3. The top package body size may be smaller than the bottom package body size by a max. of 0.15 mm.

- 4. Dimension D1 and E1 do not include mould protusion.

- 5. Dimension b does not include dambar protusion.

- 6. Coplanarity, measured at seating plane G, to be 0.010 mm max.

This drawing supersedes 418/ED/51210/029 (Swindon)

| © Mitel 1999. All rights reserved. |         |         |         |         |  |                     |               | ORIGINATING SITE: SWINDON                    |

|------------------------------------|---------|---------|---------|---------|--|---------------------|---------------|----------------------------------------------|

| ISSUE                              | 1       | 2       | 3       | 4       |  |                     |               | Title: Package Outline Drawing for           |

| ACN                                | 202049  | 204613  | 205110  | 207057  |  |                     | SEMICONDUCTOR | 64L MQFP (GP)<br>(14x14x2.0) mm, Body+3.2 mm |

| DATE                               | 20FEB97 | 22MAY98 | 10SEP98 | 30JUN99 |  | MITEL SEMICUNDUCTOR |               | Drawing Number                               |

| APPD.                              |         |         |         |         |  |                     |               | GPD00230                                     |

http://www.mitelsemi.com

#### World Headquarters - Canada

Tel: +1 (613) 592 2122 Fax: +1 (613) 592 6909

#### North America

Tel: +1 (770) 486 0194 Fax: +1 (770) 631 8213

#### Asia/Pacific

Tel: +65 333 6193 Fax: +65 333 6192

### Europe, Middle East, and Africa (EMEA) Tel: +44 (0) 1793 518528 Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Mitel Corporation or its subsidiaries (collectively "Mitel") is believed to be reliable. However, Mitel assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Mitel or licensed from third parties by Mitel, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Mitel, or non-Mitel furnished goods or services may infringe patents or other intellectual property rights owned by Mitel.

This publication is issued to provide information only and (unless agreed by Mitel in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Mitel without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or services (Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Mitel's conditions of sale which are available on request.

M Mitel (design) and ST-BUS are registered trademarks of MITEL Corporation Mitel Semiconductor is an ISO 9001 Registered Company Copyright 1999 MITEL Corporation All Rights Reserved Printed in CANADA

TECHNICAL DOCUMENTATION - NOT FOR RESALE