# DATA SHEET

# BIPOLAR DIGITAL INTEGRATED CIRCUITS μ**PB1502GR**, **1502GR**(1)

# 1.7 GHz/ 2.0 GHz LOW-POWER TWO-MODULUS PRESCALER DIVIDED-BY-64/65, 128/129

# FEATURES

NEC

- High toggle frequency 2.0 GHz: μPB1502GR(1), 1.7 GHz: μPB1502GR

- Low power consumption 6.7 mA TYP. at 3 V

- Operating supply voltage 2.7 V to 3.3 V

- High input sensitivity 130 to 220 mV<sub>P-P</sub>: μPB1502GR(1), 100 to 320 mV<sub>P-P</sub>: μPB1502GR (@50 Ω)

- Equipped with power-save function: 5  $\mu$ A (standard) on power-save mode.

- Packaged in 8 pins plastic SOP suitable for surface mounting.

## DESCRIPTION

$\mu$ PB1502GR and  $\mu$ PB1502GR(1) are two-modulus prescaler divided by 64/65 or 128/129. This device is designed for mobile communication applications for example 0.8-1.9 GHz cellular and cordless telephones. The ICs operate on low power and therefore are suitable for hand-held, battery-operated systems.

These products are manufactured using NEC's 20 GHz f⊤ NESAT<sup>™</sup> III silicon bipolar process. This process uses silicon nitride passivation film and gold metallization wirings. These materials can protect the chips from external pollution and prevent corrosion and migration. Thus, these products have excellent performance, uniformity and reliability.

#### **ORDER INFORMATION**

| ORDER NUMBER    | PACKAGE           | SUPPLYING FORM                           | fin MAX. |

|-----------------|-------------------|------------------------------------------|----------|

| μPB1502GR-E1    | 8 pin plastic SOP | Embossed tape 12 mm wide. QTY 2.5 k/reel | 1.7 GHz  |

| μPB1502GR(1)–E1 | (225 mil)         | Pin1 is in tape pull-out direction.      | 2.0 GHz  |

Remarks To order evaluation samples, please contact your local NEC sales office. (Order number: µPB1502GR, µPB1502GR(1))

#### Caution electro-static sensitive devices

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

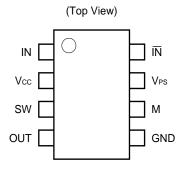

# **PIN ASSIGNMENT**

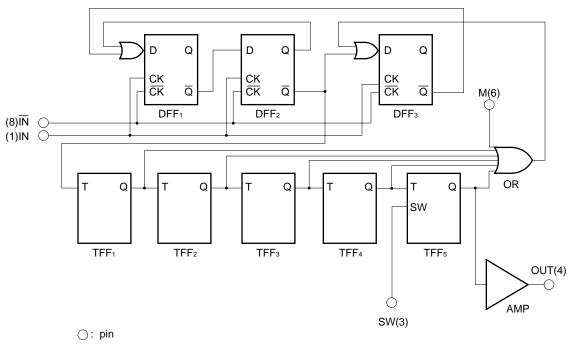

# INTERNAL BLOCK DIAGRAM

(): pin No.

# ABSOLUTE MAXIMUM RATINGS

| PARAMETER               | SYMBOL | RATINGS          | UNIT | CONDITION                                                                                                    |

|-------------------------|--------|------------------|------|--------------------------------------------------------------------------------------------------------------|

| Supply voltage          | Vcc    | -0.5 to +6       | V    | T <sub>A</sub> = +25 °C                                                                                      |

| Input voltage           | Vin    | -0.5 to Vcc +0.5 | V    | T <sub>A</sub> = +25 °C                                                                                      |

| Total power dissipation | PD     | 250              | mW   | Mounted on double sided copper clad 50 $\times$ 50 $\times$ 1.6 mm epoxy glass PWB (T <sub>A</sub> = +85 °C) |

| Operating temperature   | Topt   | -40 to +85       | °C   |                                                                                                              |

| Storage temperature     | Tstg   | -65 to +150      | °C   |                                                                                                              |

# **RECOMMENDED OPERATING RANGE**

| PARAMETER             | SYMBOL | MIN. | TYP. | MAX. | UNIT |

|-----------------------|--------|------|------|------|------|

| Supply voltage        | Vcc    | 2.7  | 3.0  | 3.3  | V    |

| Operating temperature | Topt   | -40  | +25  | +85  | °C   |

# ELECTRICAL CHARACTERISTICS (TA = -40 to +85 °C, Vcc = 2.7 to 3.3 V)

| PARAMETER                            | SYMBOL | μPB1502GR |      | μPB1502GR(1) |      | UNIT | CONDITION |                  |                                |  |

|--------------------------------------|--------|-----------|------|--------------|------|------|-----------|------------------|--------------------------------|--|

| PARAMETER                            | STMBOL | MIN.      | TYP. | MAX.         | MIN. | TYP. | MAX.      | UNIT             | CONDITION                      |  |

| Response frequency                   | fin    | 0.5       |      | 1.7          | 0.5  |      | 2.0       | GHz              | $P_{in} = -10 \text{ dBm}$     |  |

| Circuit current                      | lcc    | 3.2       | 6.7  | 11.0         | 3.2  | 6.7  | 11.0      | mA               | V⊧sH level,<br>No input signal |  |

| Input power sensitivity 1            | Pin1   | -11       | _    | 0            | -11  | _    | 0         | dBm              | fin = 0.5 to 0.8 GHz           |  |

| Input power sensitivity 2            | Pin2   | -15       |      | 0            | -15  | _    | 0         | dBm              | $f_{in} = 0.8$ to 1.5 GHz      |  |

| Input power sensitivity 3            | Pin3   | -15       | _    | -6           | -15  | —    | -1        | dBm              | fin = 1.5 to 1.7 GHz           |  |

| Input power sensitivity 4            | Pin4   | —         | _    | —            | -14  | _    | -9        | dBm              | fin = 1.7 to 2.0 GHz           |  |

| Modulus control input high (M)       | VIH1   | 2.5       | _    | —            | 2.5  | —    |           | V                |                                |  |

| Modulus control input low (M)        | VIL1   | —         | —    | 0.8          | _    | —    | 0.8       | V                |                                |  |

| Divide ratio control input high (SW) | VIH2   | Vcc       | Vcc  | Vcc          | Vcc  | Vcc  | Vcc       | V                |                                |  |

| Divide ratio control input low (SW)  | VIL2   | OPEN      | OPEN | OPEN         | OPEN | OPEN | OPEN      | V                |                                |  |

| Output voltage swing                 | Vout   | 0.8       | _    | _            | 0.8  | _    | _         | V <sub>P-P</sub> | CL = 8 pF                      |  |

| Modulus set up time                  | tset   | —         | 11   | —            | _    | 11   | _         | ns               | finMAX.                        |  |

| Power-save input high                | VpsH   | Vcc       | Vcc  | Vcc          | Vcc  | Vcc  | Vcc       | V                |                                |  |

| Power-save input low                 | VinL   | _         | _    | 0.8          | —    | —    | 0.8       | V                | *                              |  |

| Circuit current on power-save mode   | IPS    | _         | 5    | 20           | _    | 5    | 20        | μΑ               | VpsL level *                   |  |

\* Standard reference value on power-save mode.

# **PIN DESCRIPTIONS**

| Pin No. | Symbol | Assignment                         | Functions and Explanation                                                                                                                                                                   |  |  |  |  |

|---------|--------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | IN     | Frequency input pin                | Input frequency from an external VCO output.<br>Must be coupled with capacitor (e.g. 1 000 pF) for DC cut.                                                                                  |  |  |  |  |

| 2       | Vcc    | Power supply pin                   | Supply voltage 3.0 $\pm$ 0.3 V for operation. Must be connected bypass capacitor (e.g. 1 000 pF) to minimize ground impedance.                                                              |  |  |  |  |

| 3       | SW     | Divided ratio<br>control input pin | Divided ratio and modulus control can be governed by following input data to these pins.                                                                                                    |  |  |  |  |

| 6       | М      | Modulus                            | М                                                                                                                                                                                           |  |  |  |  |

|         |        | control input pin                  | H L                                                                                                                                                                                         |  |  |  |  |

|         |        |                                    | SW H 1/64 1/65                                                                                                                                                                              |  |  |  |  |

|         |        |                                    | L 1/128 1/129                                                                                                                                                                               |  |  |  |  |

| 4       | OUT    | Divided frequency output pin       | This frequency output can be interfaced to CMOS PLL.<br>Must be coupled with capacitor (e.g. 1 000 pF) for DC cut.                                                                          |  |  |  |  |

| 5       | GND    | Ground pin                         | Must be connected to the system ground with minimum inductance.<br>Ground pattern on the board should be formed as wide as possible.<br>(Track length should be kept as short as possible). |  |  |  |  |

| 7       | Vps    | Power-save<br>function pin         | ON/OFF-operation control can be governed by following input data to this pin.                                                                                                               |  |  |  |  |

|         |        |                                    | Operation                                                                                                                                                                                   |  |  |  |  |

|         |        |                                    | H ON                                                                                                                                                                                        |  |  |  |  |

|         |        |                                    | V <sub>PS</sub> L OFF                                                                                                                                                                       |  |  |  |  |

| 8       | ĪN     | Frequency-input<br>bypass pin      | Must be connected bypass capacitor (e.g. 1 000 pF) to minimize ground impedance.                                                                                                            |  |  |  |  |

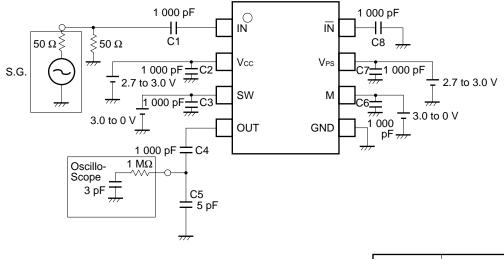

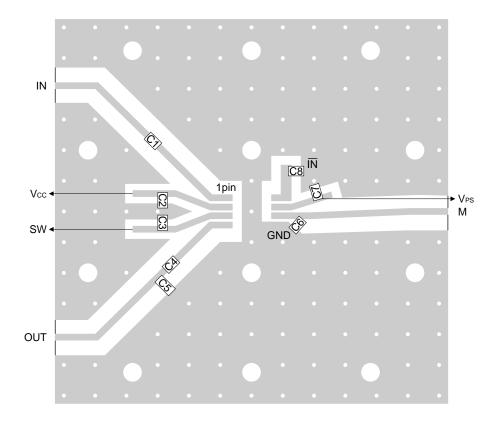

# **TEST CIRCUIT**

|     |   | М     |       |  |  |

|-----|---|-------|-------|--|--|

|     |   | Н     | L     |  |  |

| 0.4 | Н | 1/64  | 1/65  |  |  |

| SW  | L | 1/128 | 1/129 |  |  |

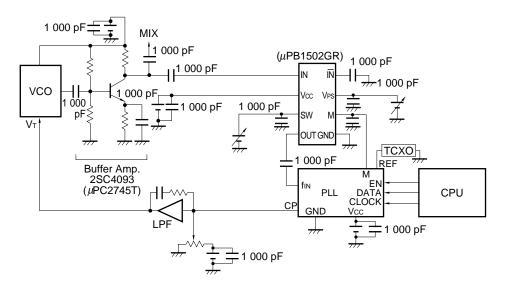

#### **APPLICATION CIRCUIT FOR REFERENCE**

The application circuits and their parameters are for references only and are not intended for use in actual design-in's. To know the real application circuits, please refer to PLL synthesizer LSI's documentations (e.g.µPD3160GS).

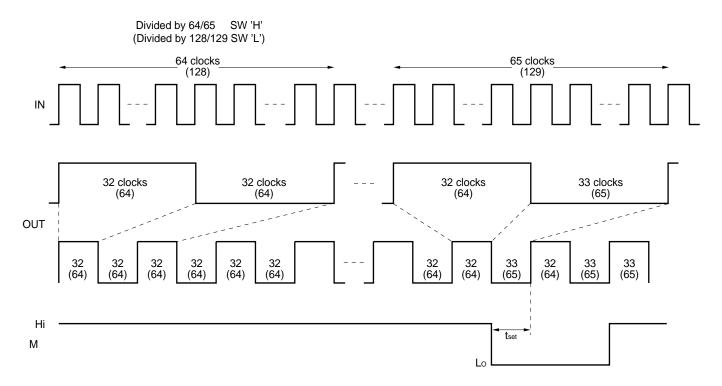

# TIMING DIAGRAM

tset = The minimum time required between 'Modulus Control' going low and next output rising edge, in order to ensure a P+1 modulus change.

# ILLUSTRATION OF THE TEST CIRCUIT ASSEMBLED ON EVALUATION BOARD

#### Component List

NEC

| No.     | Value    |  |  |

|---------|----------|--|--|

| C1 to 4 | 1 000 pF |  |  |

| C₅      | 8 pF     |  |  |

| C6 to 8 | 1 000 pF |  |  |

#### Note

- (1)  $50 \times 50 \times 0.4$  mm double copper clad polyimide board.

- (2) Back side: GND pattern

- (3) Solder plated on pattern

- (4) O: Through holes

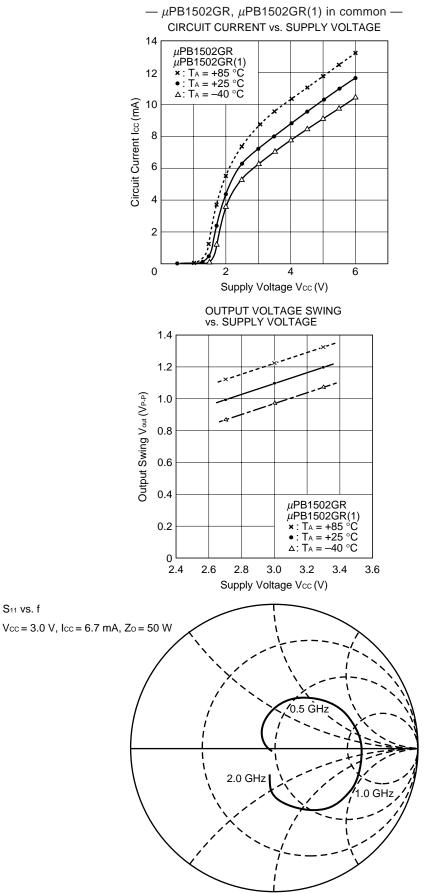

# TYPICAL CHARACTERISTICS (TA = +25 °C)

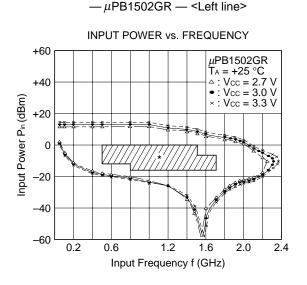

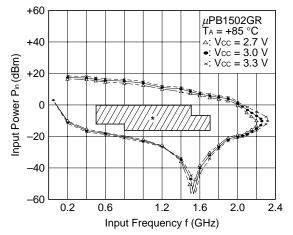

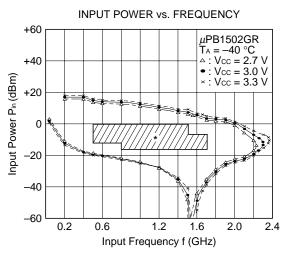

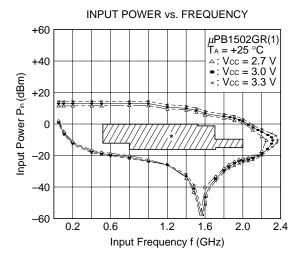

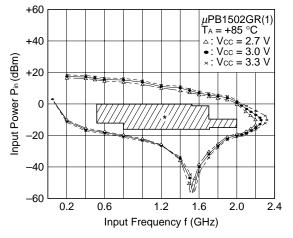

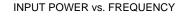

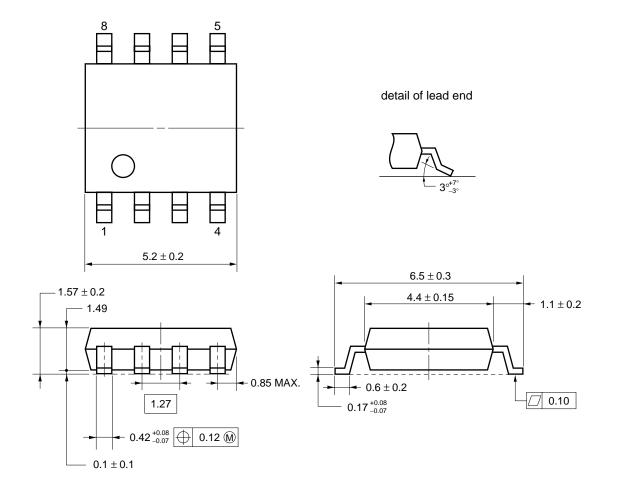

INPUT POWER vs. FREQUENCY

Guaranteed Operating Window

$-\mu$ PB1502GR(1) - <Right line>

INPUT POWER vs. FREQUENCY

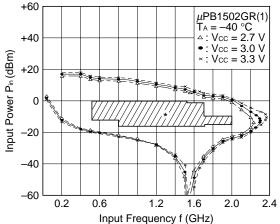

# **TYPICAL SYSTEM APPLICATION**

Digital Cellular System Block Diagram

# Other applicable systems

1.9 GHz digital cordless telephone, hand-held radio.

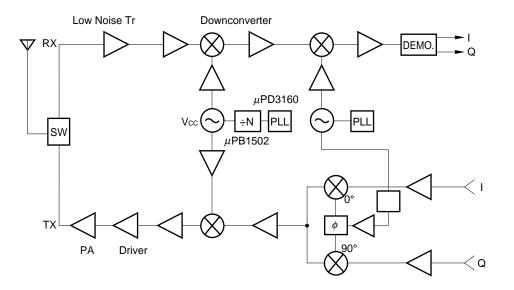

## PACKAGE DIMENSIONS

\*8 PIN PLASTIC SOP (225 mil) (UNIT: mm)

NOTE Each lead centerline is located within 0.12 mm of its true position (T.P.) at maximum material condition.

#### NOTE ON CORRECT USE

- (1) Observe precautions for handling because of electro-static sensitive devices.

- (2) Form a ground pattern as wide as possible to minimize ground impedance (to prevent abnormal operation).

- (3) Keep the wiring length of the ground pins as short as possible.

- (4) Connect a bypass capacitor (e.g. 1 000 pF) to the Vcc pin.

#### **RECOMMENDED SOLDERING CONDITIONS**

This product should be soldered in the following recommended conditions. Other soldering methods and conditions than the recommended conditions are to be consulted with our sales representatives.

#### μPB1502GR, 1502GR(1)

| Soldering method    | Soldering conditions                                                                                             | Recommended condition symbol |

|---------------------|------------------------------------------------------------------------------------------------------------------|------------------------------|

| Infrared ray reflow | Package peak temperature: 235 °C,<br>Hour: within 30 s. (more than 210 °C),<br>Time: 3 times, Limited days: no.* | IR35–00-3                    |

| VPS                 | Package peak temperature: 215 °C,<br>Hour: within 40 s. (more than 200 °C),<br>Time: 3 times, Limited days: no.* | VP15-00-3                    |

| Wave soldering      | Soldering tub temperature: less than 260 °C,<br>Hour: within 10 s.<br>Time: 1 time, Limited days: no.            | WS60-00-1                    |

| Pin part heating    | Pin area temperature: less than 300 °C,<br>Hour: within 3 s./pin<br>Limited days: no.*                           |                              |

\*: It is the storage days after opening a dry pack, the storage conditions are 25 °C, less than 65 % RH.

Note 1. The combined use of soldering method is to be avoided (However, except the pin area heating method).

For details of recommended soldering conditions for surface mounting, refer to information document SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL (C10535E).

[MEMO]

[MEMO]

[MEMO]

NESAT (NEC Silicon Advanced Technology) is a trademark of NEC Corporation.

- The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these circuits,

software, and information in the design of the customer's equipment shall be done under the full responsibility

of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third

parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a

customer designated "quality assurance program" for a specific application. The recommended applications of

a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device

before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.