# **CXD8302Q**

# **PLL for CCD Cameras**

# **Description**

The CXD8302Q has the functions needs to configure a PLL circuit with a timing generator and external sync signals for a CCD of 480K pixels (EIA, effective pixels) and 570K pixels (CCIR, effective pixels).

#### **Features**

- EIA and CCIR compatible

- Compatible with component digital and composite digital recording format

- Both SYNC and VD/HD signals can be used for external sync signals

### **Absolute Maximum Ratings**

Supply voltage

Input voltage

VDD

Vss - 0.3 to +7

V

Vss - 0.3 to Vdd+0.3

V

• Storage temperature Tstg -40 to +125 °C

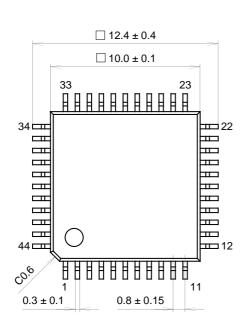

# 44 pin QFP (Plastic)

# **Applications**

CCD cameras

#### Structure

Silicon gate CMOS IC

#### **Recommended Operating Conditions**

Supply voltage VDD 4.5 to 5.5 V

Operating temperature Topr 0 to 70 °C

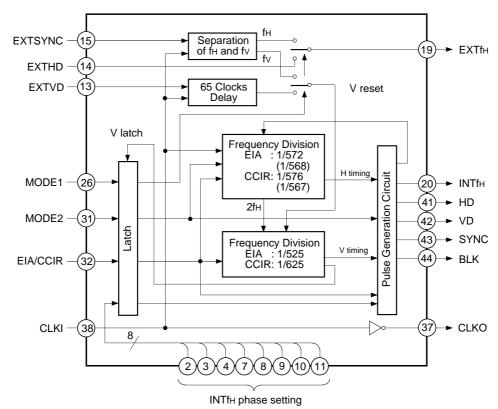

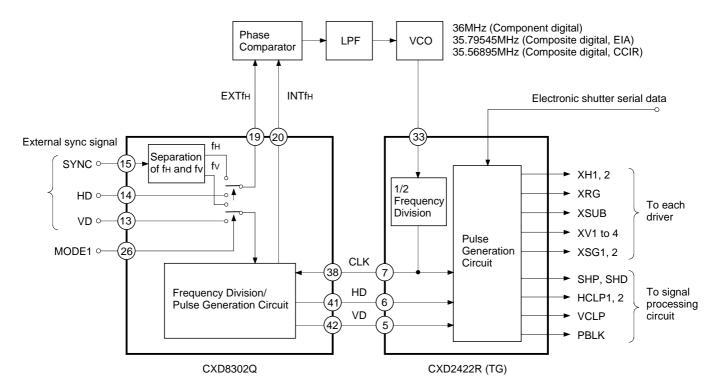

#### **Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

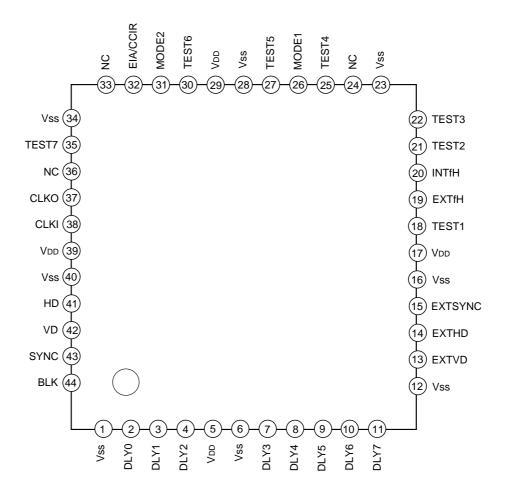

# **Pin Configuration**

# **Pin Description**

| Pin No. | Symbol          | I/O | Description                                                                         |                           |  |  |

|---------|-----------------|-----|-------------------------------------------------------------------------------------|---------------------------|--|--|

| 1       | Vss             | _   |                                                                                     |                           |  |  |

| 2       | DLY0            | I   | Pin 20 (INTfн) phase setting.                                                       | (With pull-up resistor)   |  |  |

| 3       | DLY1            | I   | Pin 20 (INTf <sub>H</sub> ) phase setting. (With pull-up resistor)                  |                           |  |  |

| 4       | DLY2            | I   | Pin 20 (INTfн) phase setting. (With pull-up resistor)                               |                           |  |  |

| 5       | VDD             | _   |                                                                                     |                           |  |  |

| 6       | Vss             |     |                                                                                     |                           |  |  |

| 7       | DLY3            | I   | Pin 20 (INTfн) phase setting.                                                       | (With pull-up resistor)   |  |  |

| 8       | DLY4            | I   | Pin 20 (INTfн) phase setting.                                                       | (With pull-up resistor)   |  |  |

| 9       | DLY5            | I   | Pin 20 (INTfн) phase setting.                                                       | (With pull-up resistor)   |  |  |

| 10      | DLY6            | I   | Pin 20 (INTfн) phase setting.                                                       | (With pull-up resistor)   |  |  |

| 11      | DLY7            | I   | Pin 20 (INTfн) phase setting (MSB).                                                 | (With pull-up resistor)   |  |  |

| 12      | Vss             |     |                                                                                     |                           |  |  |

| 13      | EXTVD           | I   | External VD input.                                                                  | (With pull-up resistor)   |  |  |

| 14      | EXTHD           | I   | External HD input.                                                                  | (With pull-up resistor)   |  |  |

| 15      | EXTSYNC         | I   | External SYNC input.                                                                | (With pull-up resistor)   |  |  |

| 16      | Vss             | _   |                                                                                     |                           |  |  |

| 17      | VDD             | _   |                                                                                     |                           |  |  |

| 18      | TEST1           | 0   | Test output (normally OPEN).                                                        |                           |  |  |

| 19      | EXTfн           | 0   | External fн output.                                                                 |                           |  |  |

| 20      | INTfн           | 0   | Internal fн output.                                                                 |                           |  |  |

| 21      | TEST2           | 0   | Test output (normally OPEN).                                                        |                           |  |  |

| 22      | TEST3           | 0   | Test output (normally OPEN).                                                        |                           |  |  |

| 23      | Vss             | _   |                                                                                     |                           |  |  |

| 24      | NC              | _   |                                                                                     |                           |  |  |

| 25      | TEST4           | I   | Test input (normally High).                                                         | (With pull-up resistor)   |  |  |

| 26      | MODE            | I   | High: SYNC sync mode, Low: VD/HD sync mode.                                         | (With pull-up resistor)   |  |  |

| 27      | TEST5           | I   | Test input (normally Low).                                                          | (With pull-down resistor) |  |  |

| 28      | Vss             | _   |                                                                                     |                           |  |  |

| 29      | V <sub>DD</sub> | _   |                                                                                     |                           |  |  |

| 30      | TEST6           | I   | Test input (normally High).                                                         | (With pull-up resistor)   |  |  |

| 31      | MODE2           | ı   | High: Component digital mode, Low: Composite digital mode.  (With pull-up resistor) |                           |  |  |

| 32      | EIA/CCIR        | I   | High: EIA mode, Low: CCIR mode.                                                     | (With pull-up resistor)   |  |  |

| 33      | NC              | _   |                                                                                     |                           |  |  |

| 34      | Vss             | _   |                                                                                     |                           |  |  |

| 35      | TEST7           | 0   | Test output (normally OPEN).                                                        |                           |  |  |

| 36      | NC              | _   |                                                                                     |                           |  |  |

| 37      | CLKO            | 0   | Inversed output of CLKI.                                                            |                           |  |  |

| Pin No. | Symbol | I/O | Description                          |

|---------|--------|-----|--------------------------------------|

| 38      | CLKI   | I   | Clock input (from timing generator). |

| 39      | VDD    | _   |                                      |

| 40      | Vss    | _   |                                      |

| 41      | HD     | 0   | Horizontal sync signal output.       |

| 42      | VD     | 0   | Vertical sync signal output.         |

| 43      | SYNC   | 0   | Sync signal output.                  |

| 44      | BLK    | 0   | Blanking pulse output.               |

#### **Electrical Characteristics**

# 1) DC characteristics

$(V_{DD} = 5V \pm 0.25V, Topr = 0 \text{ to } 70^{\circ}C, V_{SS} = 0V)$

| Item                                                 |      | Symbol | Conditions | Min.   | Тур. | Max.   | Unit |

|------------------------------------------------------|------|--------|------------|--------|------|--------|------|

| Input voltage                                        | High | ViH    |            | 0.7VDD |      |        | V    |

| input voltage                                        | Low  | VIL    |            |        |      | 0.3VDD | V    |

| Input current 1 (Input pins other than those below)  |      | lin1   |            | -10    | ±1   | 10     | μA   |

| Input current 2 (Input pins with pull-up resistor)   |      | lin2   | VI = VDD   | 10     | 35   | 120    | μA   |

| Input current 3 (Input pins with pull-down resistor) |      | lin3   | Vı = Vss   | -8     | -30  | -100   | μA   |

| Output voltage                                       | High | Vон    | Iон = −2mA | 2.4    | 4.5  |        | V    |

| Output voltage                                       | Low  | Vol    | IoL = 4mA  |        | 0.2  | 0.4    | V    |

# 2) AC characteristics

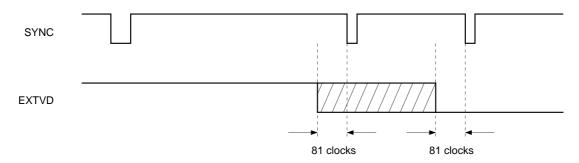

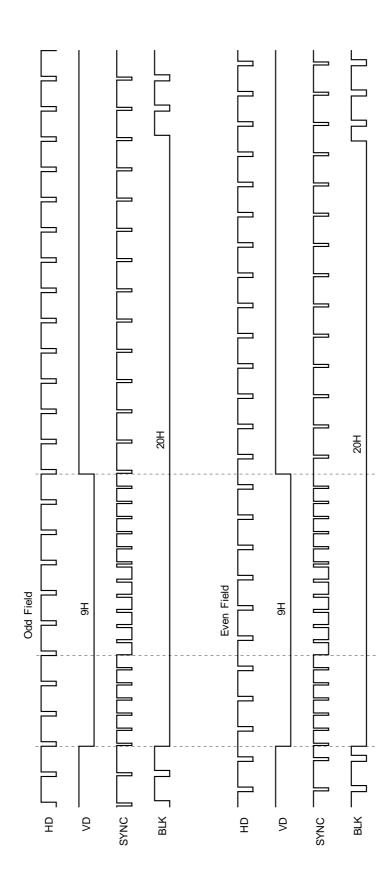

# Vertical reset in VD/HD sync mode

The phase of EXTVD should be input as shown in the diagram below against the first equivalent pulse during vertical blanking period.

(Take care as the following conditions might not be satisfied depending on the phase setting of INTfH if the phases are locked when the falling phase shifts a lot between EXTfH and INTfH.)

The EXTVD should fall at the timing shown with the slashes.

### 3) I/O pin capacitance (VDD = $5V\pm0.25V$ , Topr = 0 to $70^{\circ}C$ , Vss = 0V)

| Item                   | Symbol | Min. | Тур. | Max. | Unit |

|------------------------|--------|------|------|------|------|

| Input pin capacitance  | CIN    |      | 2.0  |      | pF   |

| Output pin capacitance | Соит   |      | 4.0  |      | pF   |

#### **Description of Operation**

### 1) Operation overview

• Functions as sync signal generator

Each of fH (INTfH), VD, HD, SYNC, and BLK pulses is generated from clocks input by the timing generator. These pulses are generated by free running if external sync signals are not input.

• External synchronization function (PLL)

When the SYNC (EXTSYNC) or VD/HD (EXTVD/EXTHD) external sync signal is input, the vertical reset is compulsorily triggered on each of the fh (INTfh), VD, HD, SYNC, and BLK pulses, and fh (EXTfh) is simultaneously generated according to the external sync signal. Phase comparison is done externally between INTfh and EXTfh and a PLL circuit is configured, then the timing generator is synchronized with an external sync signal.

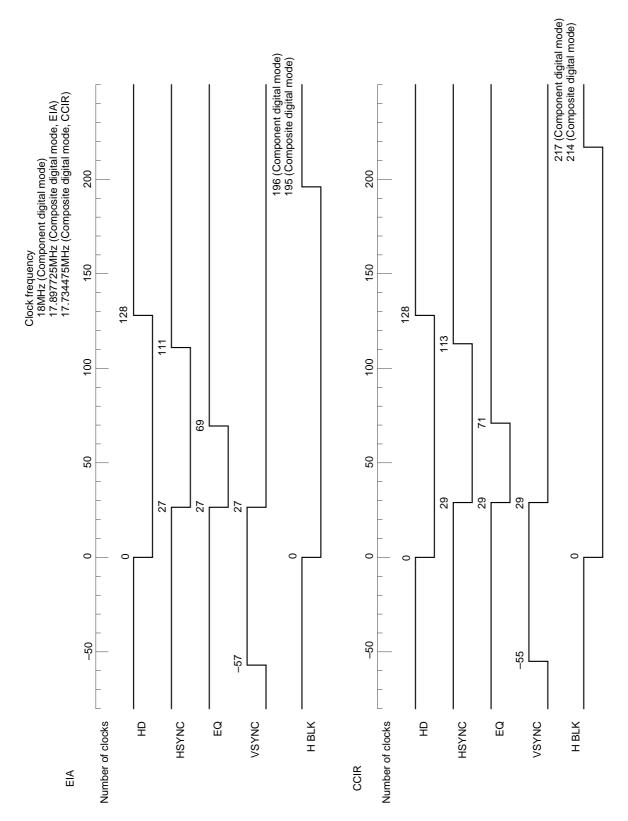

# 2) Mode setting

| Symbol   | Pin No. | L                                                                                                                                              | Н                                                                                                                    |  |  |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| EIA/CCIR | 32      | CCIR                                                                                                                                           | EIA                                                                                                                  |  |  |

| MODE1    | 26      | VD/HD sync mode:<br>EXTVD/EXTHD is used as the external<br>sync signal, and the EXTHD signal<br>becomes EXTfH.                                 | SYNC sync mode: EXTSYNC is used as the external sync signal, and the EXTfH is obtained by separating it from EXTSYNC |  |  |

| MODE2    | 31      | Composite digital mode; Clock frequency input by timing generator EIA 17.897725MHz (1137.5fH = 5fsc) CCIR 17.734475MHz (1135 + 4/625fH = 4fsc) | Component digital mode:<br>Clock frequency input by timing generator<br>EIA 18MHz (1144fH)<br>CCIR 18MHz (1152fH)    |  |  |

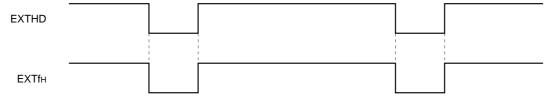

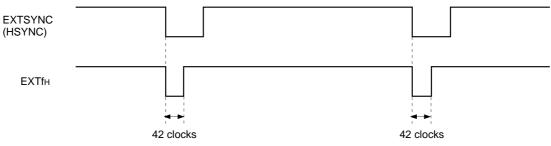

The phase relationship between external sync and EXTfH in each sync mode is shown below.

• VD/HD sync mode

The rise and fall timings of EXTHD signal are directly reflected on EXTfH.

• SYNC synchronous mode

The fall timing of EXTSYNC is the fall timing EXTfH, but the rise timing of EXTfH is generated by counting the number of clocks input by the timing generator. Therefore, make sure to compare phases of fall timing of between EXTfH and INTfH for PLL configuration in the SYNC synchronous mode.

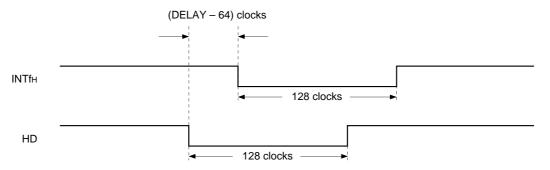

## 3) INTfH phase setting

In either VD/HD or SYNC sync mode, the INTfH phase should be adjusted in line with the phase variance of EXTfH, which forms the reference for phase comparison. The INTfH phase may be adjusted against VD, HD, SYNC and BLK pulses using DLY0 to DLY7, respectively. (The state of INTfH and EXTfH phases fixed by PLL leads to phase adjustment of VD, HD, SYNC, and BLK pulse against the external sync signal.)

The INTfH is set to the phase being delayed (DELAY-64) clocks from that of HD.

DELAY = 0 to 255: to be set in 8-bit binary with DLY7 as MSB. High: 1, low: 0.

# **Example of System Configuration**

**Note)** 1. Either SYNC or VD/HD is used as the external sync signal. When SYNC is used (SYNC synchronous mode), fix MODE1 to High; when VD/HD is used (VD/HD synchronous mode), fix MODE1 to Low.

2. Be sure to do phase comparison of the falling edge of EXTfH and INTfH for SYNC synchronous mode.

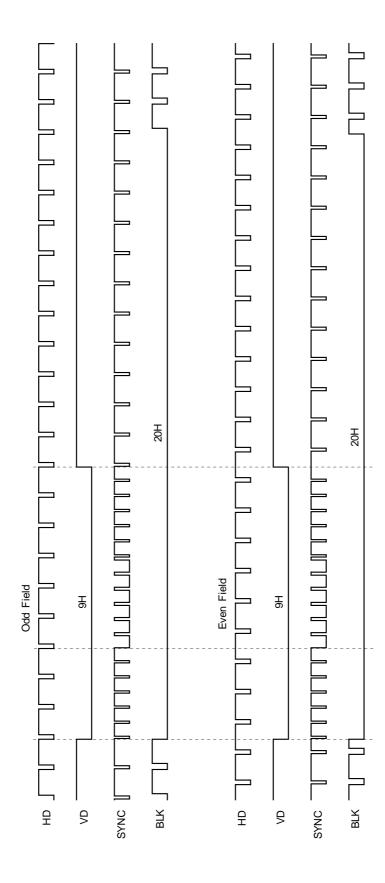

Timing Chart (2) CCIR vertical direction

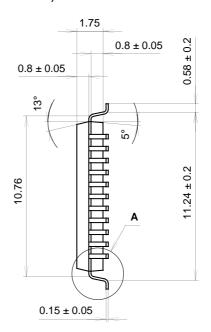

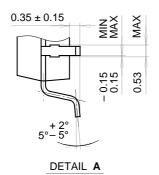

# Package Outline

#### Unit: mm

# 44PIN QFP (PLASTIC)

| SONY CODE  | QFP-44P-L221     |

|------------|------------------|

| EIAJ CODE  | *QFP044-P-1010-B |

| JEDEC CODE |                  |

# PACKAGE STRUCTURE

| PACKAGE MATERIAL | EPOXY RESIN    |  |

|------------------|----------------|--|

| LEAD TREATMENT   | SOLDER PLATING |  |

| LEAD MATERIAL    | 42 ALLOY       |  |

| PACKAGE WEIGHT   | 0.4g           |  |